# austriamicrosystems AG

is now

# ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

Headquarters: ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten, Austria Tel: +43 (0) 3136 500 0 e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

# AS3691

## 4 Precision 400mA Current Sources for RGB and Single Color Leds

#### **General Description** 1

The AS3691 (AS3691A and AS3691B) features four high precision current sources for lighting of up to four LED strings (RGB or single color leds). Each of the four currents sources can be controlled independently by PWM inputs. The full scale current value is set by external resistors.

#### **Key Features** 2

- 4 x up to 0.4A constant current outputs

- Programmable with external resistors

- 4 independent PWM inputs

- Absolute current accuracy +/-0.5%

- Automatic Supply Regulation' to reduce power dissipation<sup>1)</sup>

1) Patent Pending

4

#### Very wide output voltage current source voltage compliance

- Down to 0.41V

- Up to 15V<sup>2)</sup>

- Integrated overtemperature protection

- Separate sense pads (Rfb1-Rfb4) for easy and precise PCB Layout

- Package

- DIE

- QFN24 4x4mm

- eP-TSSOP

<sup>2)</sup> 15V is sufficient for most applications as the AS3691 dose not switch off the LED current completely

#### 3 Applications

- General Lighting

- Backlighting

- RGB Backlighting for LCD TV/Monitors with White Color Balancing

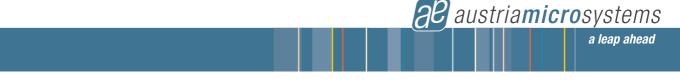

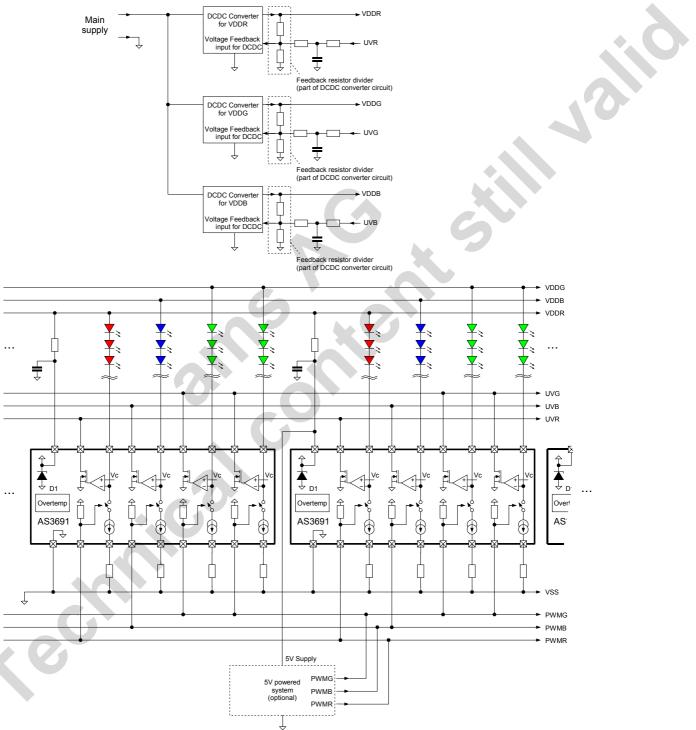

**Application Diagrams**

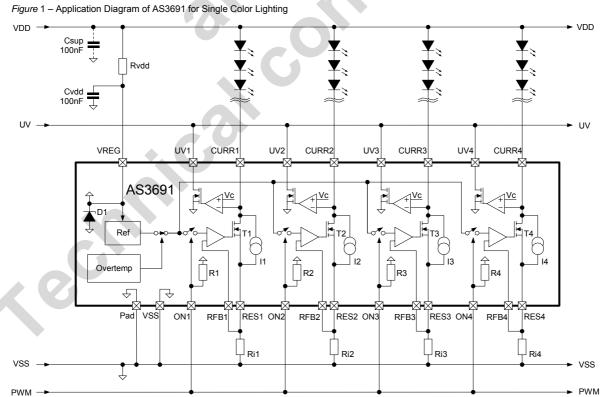

Figure 2 – Application Diagram of AS3691 for RGB Lighting

#### **Table of Contents**

| 1  | Ge   | neral Description                      | 1  |  |

|----|------|----------------------------------------|----|--|

| 2  |      | y Features                             |    |  |

| 3  | Ap   | plications                             | 1  |  |

| 4  | Ap   | plication Diagrams                     | 1  |  |

| 5  | Pin  | out                                    | 4  |  |

| Ę  | 5.1  | Pin Assignments                        | 4  |  |

| Ę  | 5.2  | Pin Descriptions                       | 4  |  |

| 6  | Ch   | aracteristics                          | 6  |  |

| 6  | 6.1  | Absolute Maximum Ratings               | 6  |  |

| 6  | 6.2  | Operating Conditions                   | 6  |  |

| 6  | 6.3  | Electrical Characteristics             | 7  |  |

| 7  | Тур  | Dical Operation Characteristics        | 8  |  |

| 8  | De   | tailed Functional Description          | 12 |  |

| 8  | 3.1  | Shunt Regulator                        | 12 |  |

| 8  | 3.2  | Overtemperature Protection             |    |  |

| 8  | 3.3  | Automatic Supply Regulation            |    |  |

| 9  | Ap   | plication Information                  |    |  |

| ę  | 9.1  | Design Example                         |    |  |

|    | 9.1  | ······································ |    |  |

|    | 9.2  | Layout Recommendations                 |    |  |

| 10 |      | Package Drawings and Markings          |    |  |

|    | 10.1 | QFN 4x4 Package Drawings and Marking   |    |  |

|    | 0.2  |                                        |    |  |

|    | 0.3  | DIE Delivery                           |    |  |

| 11 | (    | Drdering Information                   | 21 |  |

#### **Revision History**

L e C

| Revision | Date       | Owner | Description                                                                       |

|----------|------------|-------|-----------------------------------------------------------------------------------|

| 2.3      | 30.10.2007 | ptr   | <ul> <li>Added Trays as delivery option (order code AS3691A-<br/>ZQFT)</li> </ul> |

## 5 Pinout

## 5.1 Pin Assignments

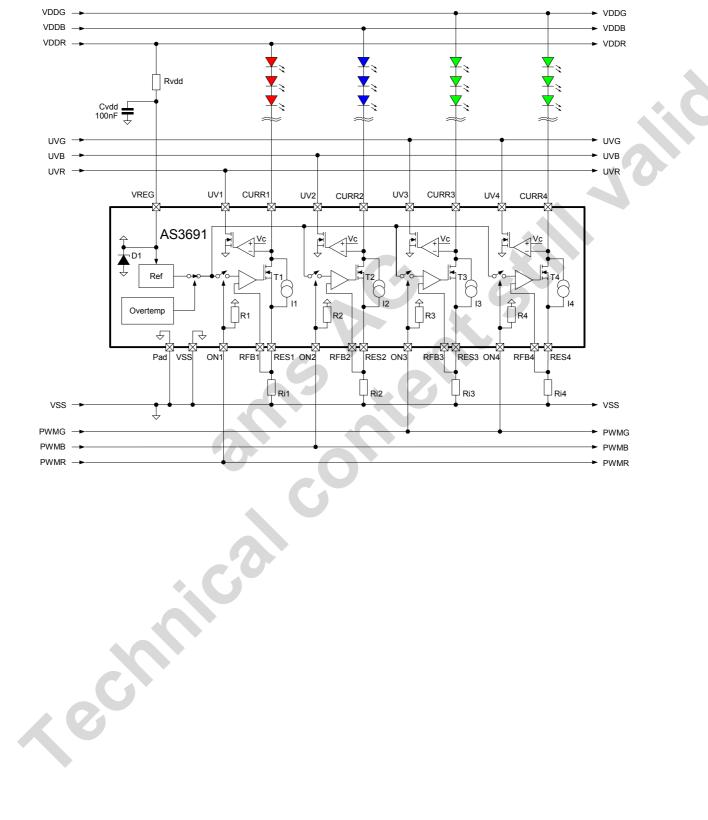

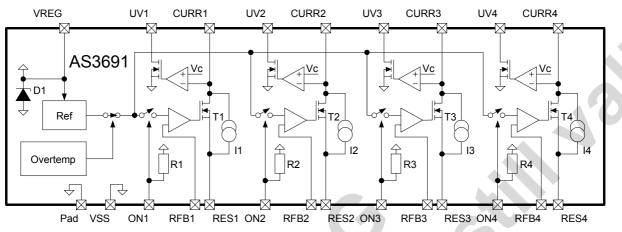

Figure 3 – Pin Usage

## 5.2 Pin Descriptions

Table 1 – Pin Type Descriptions

| Pin Type | Description       |

|----------|-------------------|

| AI/O     | Analog Pin        |

| AI       | Analog Input Pin  |

| AO       | Analog Output Pin |

| DI       | Digital Input     |

| S        | Supply Pin        |

Table 2 – Pin Descriptions

| Pin Number<br>QFN<br>Package | Pin Number<br>ePTSSOP<br>Package | Pin Name | Туре | Description                                                    |

|------------------------------|----------------------------------|----------|------|----------------------------------------------------------------|

| 1                            | 10                               | CURR1    | AI/O | Current Source 1 Output                                        |

| 2                            | 11                               | RFB1     | AI   | Connect to current set resistor R1 directly at resistor itself |

| 3                            | 12                               | nc       | nc   | Leave open                                                     |

| 4                            | 13                               | RFB4     | AI   | Connect to current set resistor R4 directly at resistor itself |

| 5 14                         |                                  | CURR4    | AI/O | Current Source 4 Output                                        |

| 6 15                         |                                  | RES4     | AI/O | Connect to current set resistor R4                             |

| Pin Number<br>QFN<br>Package | Pin Number<br>ePTSSOP<br>Package | Pin Name | Туре | Description                                                                                                                                                    |

|------------------------------|----------------------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                            | 16                               | ON4      | DI   | Current source CURR4 control; internal pullup<br>resistor to VREG (can be left open, if CURR4 is<br>always switched on)<br>High 100% Current<br>Low 5% Current |

| 8                            | 17                               | UV4      | AO   | Automatic supply regulation for CURR4; if not used, leave open                                                                                                 |

| 9                            | 18                               | TEST     | AI   | Digital Test input; Leave open or connect to VSS; internal pulldown to VSS                                                                                     |

| 10                           | 19                               | UV3      | AO   | Automatic supply regulation for CURR3; if not used, leave open                                                                                                 |

| 11                           | 20                               | ON3      | DI   | Current source CURR3 control; internal pullup<br>resistor to VREG (can be left open, if CURR3 is<br>always switched on)<br>High 100% Current<br>Low 5% Current |

| 12                           | 21                               | RES3     | AI/O | Connect to current set resistor R3                                                                                                                             |

| 13                           | 22                               | CURR3    | AI/O | Current Source 3 Output                                                                                                                                        |

| 14                           | 23                               | RFB3     | AI   | Connect to current set resistor R3 directly at resistor itself                                                                                                 |

| 15                           | 24                               | VREG     | S    | Shunt regulator supply; connect to Rvdd and Cvdd                                                                                                               |

| 16                           | 1                                | RFB2     | AI   | Connect to current set resistor R2 directly at resistor itself                                                                                                 |

| 17                           | 2                                | CURR2    | AI/O | Current Source 2 Output                                                                                                                                        |

| 18                           | 3                                | RES2     | AI/O | Connect to current set resistor R2                                                                                                                             |

| 19                           | 4                                | ON2      | DI   | Current source CURR2 control; internal pullup<br>resistor to VREG (can be left open, if CURR2 is<br>always switched on)<br>High 100% Current<br>Low 5% Current |

| 20                           | 5                                | UV2      | AO   | Automatic supply regulation for CURR2; if not used, leave open                                                                                                 |

| 21                           | 6                                | VSS      | S    | VSS Supply connection                                                                                                                                          |

| 22                           | 7                                | UV1      | AO   | Automatic supply regulation for CURR1; if not used, leave open                                                                                                 |

| 23                           | 8                                | ON1      | DI   | Current source CURR1 control; internal pullup<br>resistor to VREG (can be left open, if CURR1 is<br>always switched on)<br>High 100% Current<br>Low 5% Current |

| 24                           | 9                                | RES1     | AI/O | Connect to current set resistor R1                                                                                                                             |

| Pad                          | Pad                              | VSS      | S    | VSS Supply connection; add as many vias to ground plane as possible                                                                                            |

## 6 Characteristics

## 6.1 Absolute Maximum Ratings

Stresses beyond those listed in Table 1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 5 Electrical Characteristics is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3 – Absolute Maximum Ratings

| Symbol  | Parameter                            | Min   | Max           | Unit      | Note                                                               |

|---------|--------------------------------------|-------|---------------|-----------|--------------------------------------------------------------------|

| VDDMAX  | Supply for LEDs                      | -0.3  | >17           | V         | See notes <sup>1</sup>                                             |

| VINVREG | VREG Supply voltage                  | -0.3  | 7.0           | V         | Applicable for pin VREG                                            |

| Vin5v   | 5V Pins                              | -0.3  | VREG+<br>0.3V | V         | Applicable for 5V pins <sup>2</sup>                                |

| Vin15v  | 15V 15V Pins                         |       | 17            | V         | Applicable for CURR1, CURR2, CURR3 and CURR4                       |

| lin     | Input Pin Current                    | -25   | +25           | mA        | At 25°C, Norm: Jedec 17                                            |

| TSTRG   | Storage Temperature Range            | -55   | 125           | °C        |                                                                    |

|         | Humidity                             | 5     | 85            | %         | Non condensing                                                     |

| VESD    | Electrostatic Discharge              | -2000 | 2000          | V         | Norm: MIL 883 E Method 3015                                        |

| PT      | Total Power Dissipation              |       | 2.0           | W         | At 50°C, no airflow for QFN24 on two layer FR4-Cu PCB <sup>3</sup> |

| Pderate | PT Derating Factor                   |       | 23            | mW/<br>°C | See notes <sup>3</sup>                                             |

| TBODY   | Body Temperature during<br>Soldering |       | 260           | °C        | according to IPC/JEDEC J-STD-<br>020C                              |

Notes:

1. As the AS3691 is not directly connected to this supply. Only the parameters VINVREG, VIN5V and VIN15V have to be guaranteed by the application

2. All pins except CURR1, CURR2, CURR3 and CURR4

3. Depending on actual PCB layout and especially number of vias below the exposed pad – see layout recommendations; can be improved e.g. with AI-PCB or airflow

# 6.2 Operating Conditions

Table 4 – Operating Conditions

| Symbol  | Parameter                  | Min | Тур  | Max            | Unit | Note                                                                                 |

|---------|----------------------------|-----|------|----------------|------|--------------------------------------------------------------------------------------|

| VDD     | Main Supply                |     |      | Not<br>Limited | V    | Supply is not directly connected to the AS3691 – see section 'Shunt Regulator'       |

| VDDTOL  | Supply (shunt regulated by |     |      | +20            | %    | Applies only for supply VREG is<br>connected via Rvdd                                |

| VREGINT |                            |     | 5.2  | 5.4            | V    | If internally (shunt-)regulated by D1                                                |

| VREGEXT |                            | 4.5 | 4.75 | 5.0            | V    | If externally supplied                                                               |

| IVREG   | Supply Current             |     |      | 2.5            | mA   | Excluding current through shunt<br>regulator (D1) – see section<br>'Shunt Regulator' |

| Тамв    | Ambient Temperature        | -20 | 25   | 85             | °C   |                                                                                      |

# 6.3 Electrical Characteristics

| Table 5 – Analog E | Electrical Characte | eristics |

|--------------------|---------------------|----------|

|--------------------|---------------------|----------|

| Symbol        | Parameter                                   | Min  | Тур | Max                | Unit | Note                                                                                                                                                          |

|---------------|---------------------------------------------|------|-----|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcurr         | Current Source CURR1 to                     | 0.9  |     | 15.0               | V    | at 400mA; total power dissipation<br>limit PT must not be exceeded                                                                                            |

|               | CURR4 Voltage Compliance                    | 0.41 |     | 15.0               | V    | at 100mA                                                                                                                                                      |

| Icurr         | Current Source Range                        | 10   |     | 400 <sup>(1)</sup> | mA   | ONx = high<br>ICURRx = 250mV / Rix (x=14)                                                                                                                     |

|               |                                             | -0.5 |     | +0.5               | %    | @25C T <sub>JUNCTION</sub> , excluding<br>variation of external resistors;<br>V(CURRx) <= 4.0V                                                                |

| ICURR,<br>TOL | Current Source Tolerance                    | -1.5 |     | +1.5               | %    | -20°C to +100°C <sup>(2)</sup> T <sub>JUNCTION</sub> ,<br>-20°C to +85°C T <sub>AMB</sub> , excluding<br>variation of external resistors;<br>V(CURRx) <= 4.0V |

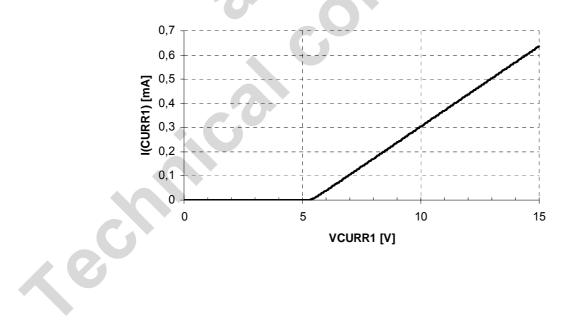

| Vc            | Automatic Supply Regulation compare voltage |      | 1.0 |                    | V    | See section 'Automatic Supply Regulation'                                                                                                                     |

| VC,GAIN       | Automatic Supply Regulation gain            |      | 2.0 |                    | mA/V | Voltage to current ratio; output current range typ 0 to 200uA                                                                                                 |

| 14.4          | Parallel Current                            |      |     | 1.0                | mA   | V(CURRx) <= 15V                                                                                                                                               |

| <b> </b> 1-4  |                                             |      |     | 0.1                | mA   | V(CURRx) <= 5.0V                                                                                                                                              |

| TOVTEMP       | Overtemperature Limit                       |      | 140 |                    | °C   | Maximum junction temperature                                                                                                                                  |

#### Notes:

- 1. To obtain higher currents connect more than one current source in parallel

- 2. Accuracy at +100°C guaranteed by design and verified by laboratory characterization

| Symbol | Parameter                | Min | Тур | Max  | Unit | Note                                                                                                                                                              |

|--------|--------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIH    | High Level Input voltage | 2.3 |     | VREG | V    |                                                                                                                                                                   |

| VIL    | Low Level Input voltage  | 0.0 |     | 0.9  | V    |                                                                                                                                                                   |

| Rpu    | Pullup resistor          |     | 70  |      | kΩ   | Internal pullup resistor R1 to R4 to VREG                                                                                                                         |

| fon    | Input Frequency Range    | 0   |     | 20   | kHz  | This defines the actual input<br>frequency seen on the input ON1<br>to ON4; the basic frequency to<br>generate the PWM signal is not<br>limited by this parameter |

| 6      | G                        |     |     |      |      |                                                                                                                                                                   |

Table 6 - Digital Input pins characteristics for pins ON1, ON2, ON3 and ON4

# 7 Typical Operation Characteristics

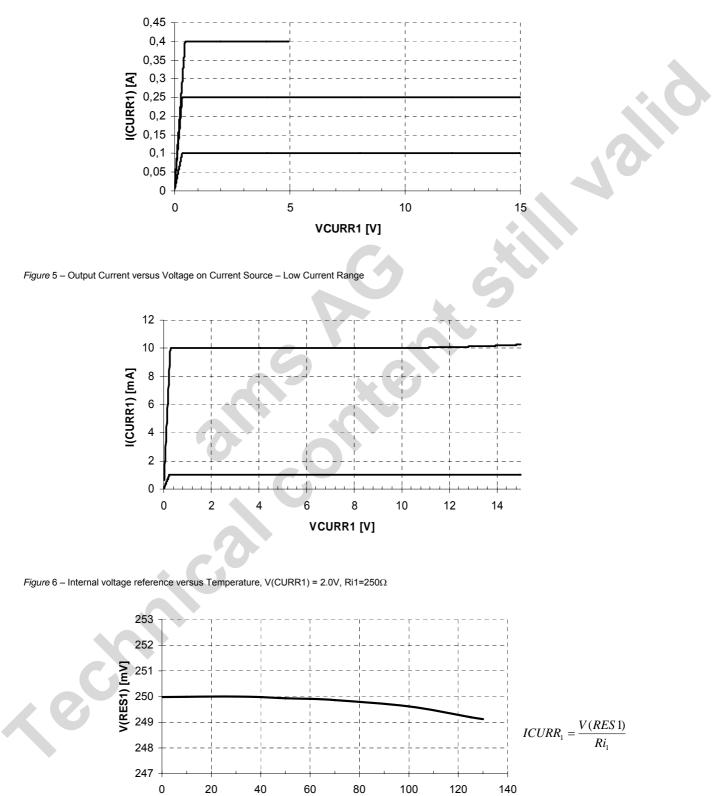

Figure 4 - Output Current versus Voltage on Current Source - High Current Range

Temperature [C]

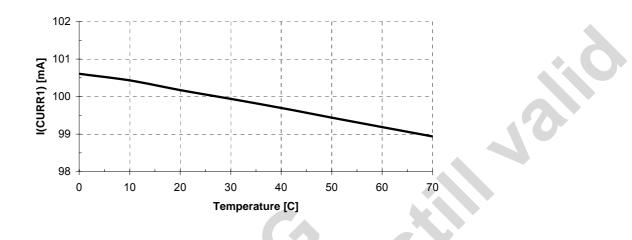

*Figure* 7 – Output Currnent versus Temperature, V(CURR1) = 2.0V, Ri1 = 2.5Ω (Note: temperature coefficient of Ri1 = -200ppm/°C)

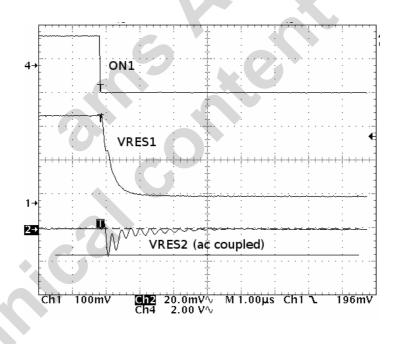

Figure 8 - Cross coupling of pwm on CURR1 to CURR2; I(CURR1) = 100mA to 4mA, I(CURR2) = 100mA; AS3691A

reci

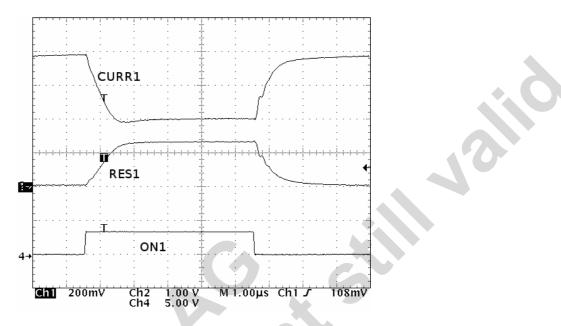

Figure 9 – PWM performance of Current Source CURR1, I(CURR1) changed between 400mA (ON1=1) and 20mA (ON1=0); AS3691A

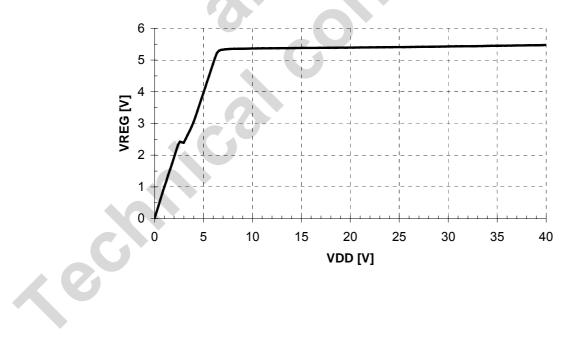

Figure 10 – Shunt Regulator Voltage VREG versus supply VDD with Rfb=1k $\Omega$

*austriamicro*systems

#### Datasheet

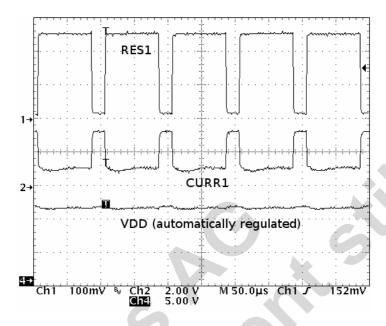

Figure 11 – Automatic Supply Regulation dynamic performance using DCDC converter in regulation loop (as in section 7.3)

R1 = 47kΩ, R2 = 10kΩ, R3 = 5kΩ, R4 = 500Ω, C1 = 1uF, I(CURR1) = 400mA/20mA (Ri1=0.625Ω)

3 OSRAM Golden Dragon in series as load between CURR1 and VDD

Input signal on pin ON1: PWM signal with f=10kHz, 80% duty cycle

Figure 12 – Parallel Current I1 to I4 (for measurement of I1 remove current set resistor R1)

## 8 Detailed Functional Description

The AS3691 includes four high precision current sources (sinks). Each current source is set by an external resistor. For internal power supply an internal shunt regulator is used. Optionally an additional 5V device can be supplied as well with this shunt regulator.

The current sources are individually controlled by four ON inputs. If the inputs ON are high or left open, then the current is set as follows:

$$ICURR_{1-4} = \frac{250mV}{Ri_{1-4}}$$

Setting the input ON to low the current is

$ICURR_{1-4} = \frac{10.0mV}{Ri_{1-4}}$  for part numbers starting with AS3691A

The current is not zero to avoid high voltage jumps on the LEDs and supplies and therefore reduce EMI.

$$ICURR_{1-4} = \frac{0.0mV}{Ri_{1-4}} + I_{1-4} = I_{1-4}$$

for part numbers starting with AS3691B; I1-4 is the parallel current (see above Figure 11)

## 8.1 Shunt Regulator

The supply of the AS3691 is generated from the high voltage supply. To obtain a 5V regulated supply, a series resistor Rvdd is used together with an internal zener diode (shunt regulator principle). An external capacitor Cvdd is used to filter the supply on the pin VREG.

The external resistor Rvdd has to be choosen according to the following formula:

$$Rvdd = \frac{VDD_{MIN} - VVREGINT_{MAX}}{IVREG_{MAX}}$$

$VDD_{MIN}$  is the minimum voltage of the supply, where Rvdd is connected

This ensures enough supply current (IVREGMAX) for the AS3691 under minimum supply voltage VDDMIN.

If a stable 5V supply within the operating conditions limits of VREGEXT is already existing in the system it is possible to supply the AS3691 directly. In this case remove the resistor Rvdd and connected this supply directly to VREG.

## 8.2 Overtemperature Protection

If the junction temperature inside the AS3691 rises above TOVTEMP, the current sources are switched off.

## 8.3 Automatic Supply Regulation

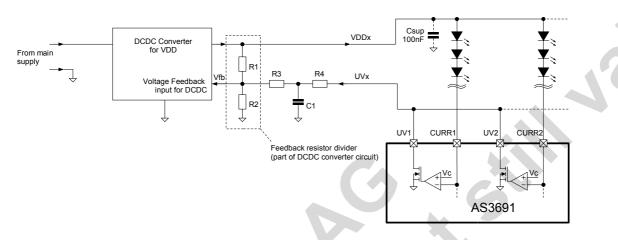

The purpose of the automatic supply regulation is to minimize the voltage supply to reduce the voltage across the current sources of the AS3691 (CURR1-CURR4 to VSS) and therefore reduce the power dissipation of the AS3691 and the complete system. The AS3691 automatically controls the minimum required supply voltage for the different led strings to support very power efficient systems for lighting using the following circuit (any off-the-shelf dcdc converter or Ido with adjustable output voltage can be used):

Figure 13 – Automatic Supply Regulation Circuit

The function of this circuit is as follows:

All channels, which are connected to the supply VDDx should have their respective UV pin connected together to UVx (see above Figure and Section 'Application Schematic'). If any of these current sources has a too low voltage, it gradually pulls the wire UVx low. (The analog gain between the current source CURRx and output UVx is defined by the parameter  $V_{C,GAIN}$ .)

Therefore the feedback pin Vfb of the dcdc converter is pulled low and the dcdc converter compensates this by increasing the voltage on VDDx to obtain the same feedback voltage as before.

To stabilize this regulation loop, the low pass filter build by C1 and R4 is used (this should be the dominant pole for the regulation loop).

The minimum output voltage VDDx<sub>min</sub> can be set accurately by the resistors R1 and R2. The maximum output voltage VDDx<sub>max</sub> is set by R1, R2, R3 and R4 (Vref is the internal voltage reference of the DCDC converter; usually Vref = Vfb):

$$VDDx_{MIN} = Vref \frac{R_1 + R_2}{R_2}$$

$$VDDx_{MAX} = Vref \frac{R_1 + R_2 || (R_3 + R_4)}{R_2 || (R_2 + R_4)}$$

Therefore even if a led string is broken (then UVx is forced to 0V) or some leds are shorted, the supply always stays within the limits VDDXMIN and VDDXMAX.

# 9 Application Information

**Typical Application Schematic**

For RGB leds (and a white color balancing circuit) use the following application schematic including automatic supply regulation (feedback paths UVR, UVG, UVB):

Figure 14 – Typical AS3691 System for RGB (back-)lighting; several AS3691 can be cascaded

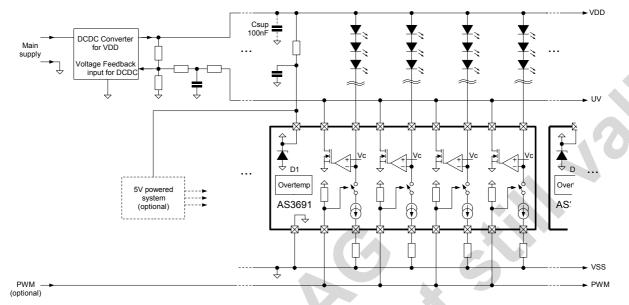

A typical AS3691 for single color leds can be done as follows using automatic supply regulation (feedback path UV):

Figure 15 – Typical AS3691 system for single color leds and supply regulation loop; serveral AS3691 can be cascaded

Note: Csup (100nF) is only required, if there are long wires (>0.3m) between the DCDC converter and the AS3691. The wire length between the Csup capacitor and the CURRx pin on AS3691 should not exceed 0.3m. If this cannot be guaranteed, add additional capacitors of 100nF to the pins CURRx.

### 9.1 Design Example

Assume a single color leds application (4 times 3 leds in series, each 100mA with Uf ranging from Uf<sub>min</sub>=3.2V to Uf<sub>max</sub> = 3.8V) with a fixed supply. First choose the external current set resistor with the following formula:

$$Ri_{1-4} = \frac{250mV}{ICURR_{1-4}}$$

So for a current of 100mA, use a resistor of  $2.5\Omega$ ; 1/8W rated resistors are suitable (even up to 400mA).

Then calculate the required voltage of the power supply. The minimum voltage on the current sink for guaranteed operation is 0.41V (VCURR @100mA) and the maximum forward voltage of the LEDs is assumed to be Ufmax = 3.8V. Therefore 3\*3.8V + 0.41V = 11.81V.

As this is the required minimum voltage of the power supply, add all the tolerances on top. Assumed +/-10% supply tolerance results in a power supply with nominal 13V (to have at least 11.81V in worst case). Using the following formula to calculate the external shunt resistor

$$Rvdd = \frac{VDD_{MIN} - VREGINT_{MAX}}{IVREG_{MAX}} = \frac{VDD_{MIN} - 5.4V}{2.5mA}$$

VDDMIN is power su

DMIN is the minimum voltage of the wer supply, where Rvdd is connected

obtains 2564 $\Omega$ . The nearest lower(!) available value is 2.4k $\Omega$ . For Cvdd use

$$Cvdd = 100nF$$

Csup (100nF) is only required, if there are long connections between the DCDC converter and the AS3691 (>0.3m). The wire length between the Csup capacitor and the CURRx pin on AS3691 should not exceed 0.3m. If this cannot be guaranteed, add additional capacitors of 100nF to the pins CURRx.

Then calculate the maximum power dissipation inside the AS3691. The worst case is maximum voltage supply (13V + 10%) together with LEDs with minimum forward voltage Ufmin :

For these conditions the maximum voltage on any current source (CURR1 to CURR4) is

$$VCURR_{MAX} = (1 + VDD_{TOL}) VDD - n U_{fmin}$$

Not using automatic supply regulation

In our example 14.3V - 9.6V = 4.7V. The maximum power dissipation inside the AS3691 is now (assuming 4 identical strings)

$$P_{MAX} = 4 \ VCURR_{MAX} \ ICURR$$

In our example 1.88W. As

$$T_{MAX} = \frac{PT - P_{MAX}}{P_{DERATE}} + 50^{\circ} C$$

For PT and PDERATE see Absolute Maximum Ratings

the system can be operated safely up to an ambient temperature of 55°C assuming worst case power supplies and worst case leds. Please note: If the internal junction temperature of the AS3691 rises too high, the AS3691 will switch off the current sources for protection (it will never damage the AS3691).

#### 9.1.1 Using Automatic Supply Regulation

For the identical system using the automatic supply regulation, the supply is regulated to minimize the power dissipation of the system. Therefore the tolerance of the VDD supply and also the variation in forward voltages of the LEDs can be ignored (only the difference in one lot of leds is still important, as the four strings are connected in parallel to the power supply). Assume a difference of  $\Delta Uf = 0.2V$  of forward voltage of the leds in one lot, then calculate the maximum voltage on the current source of the AS3691 (CURR1 to CURR4) with

$VCURR_{MAX} = n \Delta U_f + V_C$

Using automatic supply regulation AUf variation of LED forward voltage in one lot (for one application) Vc is internal set voltage (1.0V)

to be 1.6V. Using the identical formulas as above, PMAX now is 0.64W and TMAX is 110°C.

Therefore using automatic supply regulation, the ambient temperature can be up to 110°C under identical conditions.

### 9.2 Layout Recommendations

See austriamicrosystems 'AN3691 TECH Module Description' as a layout example for the AS3691.

Layout Checklist

- 1. Use the bottom layer as ground plane and minimize the number and the length of connections within this layer

- 2. Do as many vias as possible on the exposed pad (for thermal performance) to the ground plane

- 3. Connect RFBx and RESx together at the current set resistor Rix (see above recommended layout)

- 4. The ground connections of the current set resistors should be as close to the AS3691 as possible

- 5. The ground connection of the capacitor Cvdd should be as close as possible to the AS3691

- 6. Minimize Area build by 'Csup VSS connection Csup Supply Connection LEDs CURRx Csup VSS connection' (to minimize inductance in this path)

## **10 Package Drawings and Markings**

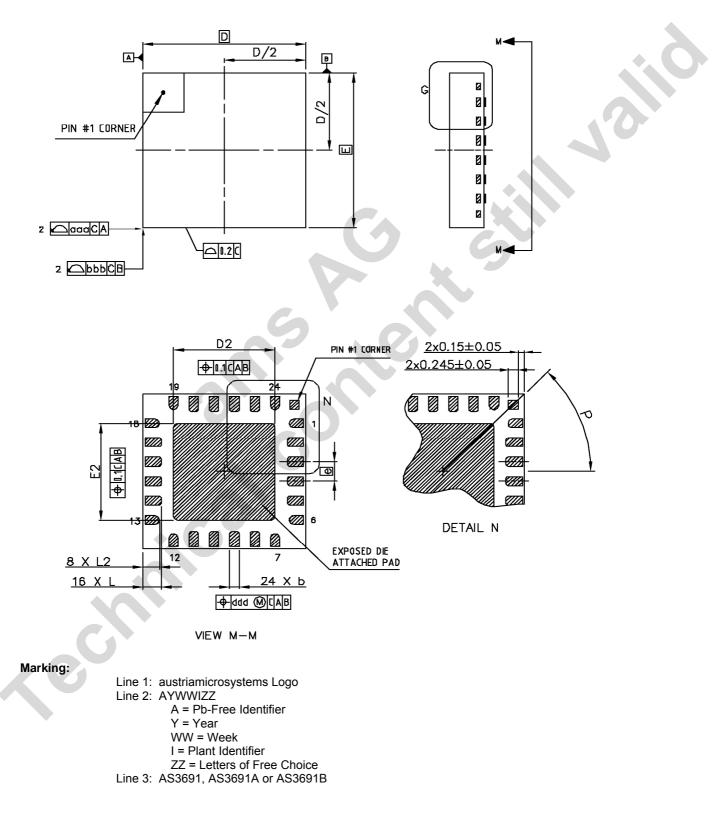

# 10.1 QFN 4x4 Package Drawings and Marking

Figure 16 – QFN 24 – 4x4mm

*austriamicro*systems

#### Datasheet

Figure 17 – QFN 24 – 4x4mm Detail Dimensions

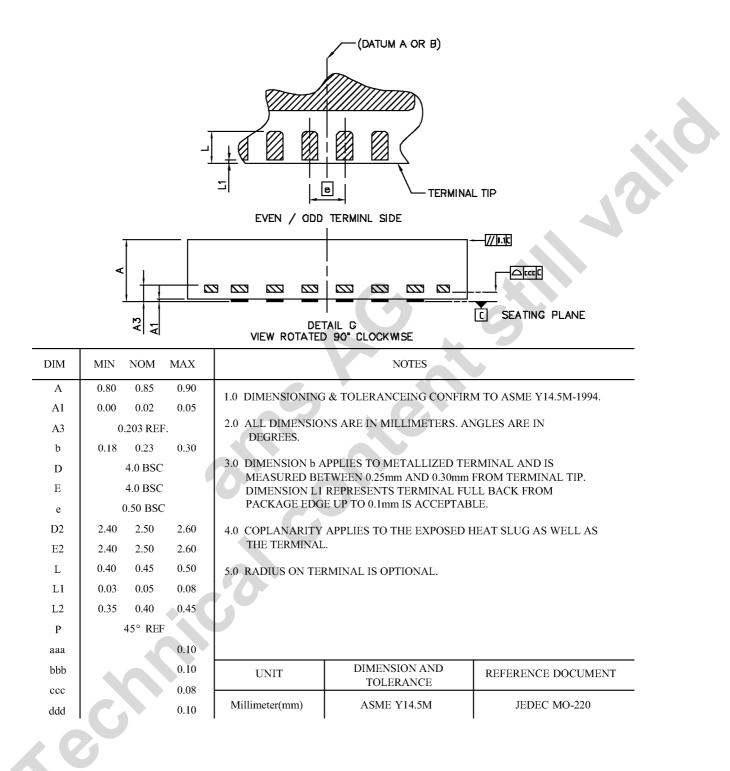

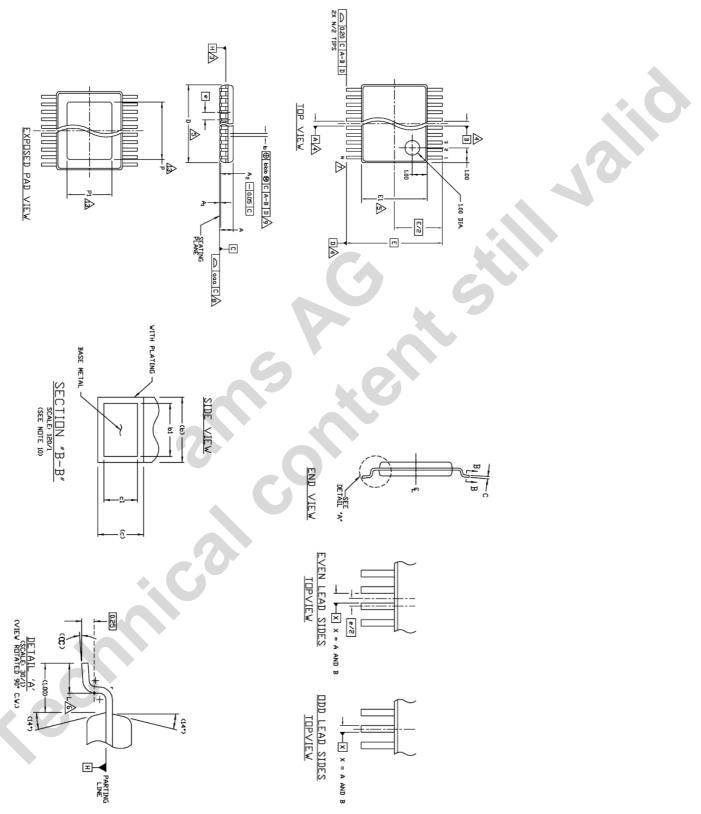

# 10.2 ePTSSOP Package Drawings and Marking

Figure 18 – ePTSSOP Package Drawing

Marking:

Line 1: austriamicrosystems Logo Line 2: AYWWIZZ A = Pb-Free Identifier Y = Year WW = Week I = Plant Identifier ZZ = Letters of Free Choice Line 3: AS3691, AS3691A or AS3691B

Figure 19 – ePTSSOP Package Drawing Detail Dimenstions

| s,        |                |        |      | INDTE I          |            | 5    |      |      |      |      |    |

|-----------|----------------|--------|------|------------------|------------|------|------|------|------|------|----|

| "s        | DI             | MENSID | NS   | ۳.,              | VARI-      |      | D    |      | P    | P1   | N  |

|           | MIN.           | NDM.   | MAX. | - <sup>-</sup> τ | ATIONS     | MIN. | NDM. | MAX. | MAX. | MAX. |    |

| Α         |                |        | 1.10 |                  | AA/AAT     | 2.90 | 3.00 | 3.10 | 1.59 | 3,2  | 8  |

| A,        | 0.05           |        | 0.15 |                  | AB-1/ABT-1 | 4.90 | 5.00 | 5.10 | 3.1  | 3.0  | 14 |

| Ag        | 0.85           | 0.90   | 0.95 |                  | AB/ABT     | 4.90 | 5.00 | 5.10 | 3.0  | 3.0  | 16 |

| ممم       |                | 0.076  |      |                  | AC/ACT     | 6.40 | 6.50 | 6.60 | 4.2  | 3.0  | 20 |

| b         | 0.19           | -      | 0.30 | 9                | AD/ADT     | 7.70 | 7.80 | 7.90 | 5.5  | 3,2  | 24 |

| b1        | 0.19           | 0.22   | 0.25 |                  | AE/AET     | 9.60 | 9.70 | 9,80 | 5.5  | 3.0  | 28 |

| bbb       |                | 0.10   |      |                  |            |      |      |      |      |      |    |

| c         | 0.09           | -      | 0.20 |                  |            |      |      |      |      |      |    |

| c1        | 0.09           | 0.127  | 0.16 |                  |            |      |      |      |      |      |    |

| D         | SEE VARIATIONS |        |      | 5                |            |      |      |      |      |      |    |

| <b>F1</b> | 4.30           | 4.40   | 4.50 | 5                |            |      |      |      |      |      |    |

NOTES:

e

E

Ν P

P

œ

0.50

SE

SEE

SEE

1. DIE THICKNESS ALLOWABLE IS 0.279±0.0127 (.0110±.0005 INCHES) 2. DIMENSIONING & TOLERANCES PER ASME. Y14.5M-1994.

0.70

- ▲ DATUM PLANE & LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE. ▲ DATUM A-B AND D TO BE DETERMINED WHERE CENTERLINE BETWEEN LEADS EXITS PLASTIC BODY AT DATUM PLANE H.

- BETWEEN LEADS EXITS PLASTIC BUDY AT DATUM PLANE H.

'D' & 'E1' ARE REFERENCE DATUM AND DD NOT INCLUDE MOLD FLASH OR

PROTRUSIONS, AND ARE MEASURED AT THE BOTTOM PARTING LINE. MOLD

FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15mm ON D AND 0.25mm

ON E PER SIDE.

DIMENSION IS THE LENGTH OF TERMINAL

FOR SOLDERING TO A SUBSTRATE.

A TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

0.65 BS 40 BS

0.60

VARIATIONS

VARIATIONS

VARIATIONS

- ▲ TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

▲ FORMED LEADS SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITHIN 0.076mm AT SEATING PLANE.

▲ THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.07mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND AN ADJACENT LEAD SHOULD BE 0.07mm FOR 0.65MM PITCH, 0.08MM FOR 0.50MM PITCH AND 0.07MM FOR 0.40MM PITCH, 0.08MM FOR 0.50MM PITCH AND 10 0.25 MM FROM THE LEAD TIP. 11. CONTROLLING DIMENSION MILLIMETERS.

12. THIS PART IS COMPLIANT WITH JEDEC SPECIFICATION MD-153 VARIATIONS AA/AAT, AB-1/ABT-1, AB/ABL, AC/ACT, AD/ADT, AE/AET BC-1/BCT-1, BD-1/BDT-1, BE/BT, CA/CAT & CD/CDT ADD MD-194 VARIATIONS AC/ACT & AF/AFT.

▲ DIMENSIONS 'P' AND 'PI' ARE THERMALLY ENHANCED VARIATIONS. VALUES SHOWN ARE MAXIMUM SIZE OF EXPOSED PAD FOR SPECIFIC DEVICE APPLICATION.

ALL DIMENSIONS IN MILLIMETERS

### 10.3 DIE Delivery

Please contact austriamicrosystems for die delivery.

## **11 Ordering Information**

Table 7 – Ordering Information

| Part Number                | Marking                                               | Package Type     | <b>Delivery Form</b>         | Description                                                                                                    |

|----------------------------|-------------------------------------------------------|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|

| AS3691A-ZQFP               | AS3691A <sup>1)</sup><br>-or-<br>AS3691 <sup>1)</sup> | QFN 24<br>4x4mm  | Tape and Reel<br>in Dry Pack | Package Size = 4x4x0.85mm,<br>Pitch = 0.5mm, Pb-Free;<br>10mV on VRES for ON=0                                 |

| AS3691A-ZQFT               | AS3691A                                               | QFN 24<br>4x4mm  | Trays<br>in Dry Pack         | Package Size = 4x4x0.85mm,<br>Pitch = 0.5mm, Pb-Free;<br>10mV on VRES for ON=0                                 |

| AS3691A-ZSDF <sup>2)</sup> | (AS3691A)                                             | Sorted<br>Wafers | Cut Dies on Foil             | Sorted Wafers;<br>10mV on VRES for ON=0                                                                        |

| AS3691B-ZQFP               | AS3691B                                               | QFN 24<br>4x4mm  | Tape and Reel<br>in Dry Pack | Package Size = 4x4x0.85mm,<br>Pitch = 0.5mm, Pb-Free;<br>0mV on VRES for ON=0                                  |

| AS3691B-ZSDF <sup>2)</sup> | (AS3691B)                                             | Sorted<br>Wafers | Cut Dies on Foil             | Sorted Wafers;<br>0mV on VRES for ON=0                                                                         |

| AS3691A-ZTSP <sup>2)</sup> | AS3691A                                               | ePTSSOP          | Tape and Reel<br>in Dry Pack | Enhanced Power TSSOP (with power pad),<br>Body Size=4.4mm<br>Pitch = 0.65mm, Pb-Free;<br>10mV on VRES for ON=0 |

| AS3691B-ZTSP AS3691        |                                                       | ePTSSOP          | Tape and Reel<br>in Dry Pack | Enhanced Power TSSOP (with power pad),<br>Body Size=4.4mm<br>Pitch = 0.65mm, Pb-Free;<br>0mV on VRES for ON=0  |

#### Note:

- 1) AS3691 with 10mV on VRES for ON=0 can be marked with 'AS3691' or 'AS3691A' (identical behavior)

- 2) Contact austriamicrosystems for availability

#### **Description:**

#### AS3691V-CPPD

- AS3691 Version, either A or B

AS3691A: 10mV on VRESx (x=1 to 4) if ONx = 0 (see '7 Detailed Functional Description')

AS3691B: 0mV on VRESx (x=1 to 4) if ONx = 0 (see '7 Detailed Functional Description')

- C ... Temperature range -20°C 85°C

- PP ... Package; QF for QFN, SD for sorted DIEs, TS for enhanced Power TSSOP

- D... Delivery From; P for Tape&Reel in Dry Pack, F for cut dies on foil, T for Trays in Dry Pack

## Copyright

Copyright © 1997-2007, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

## Diclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information.

This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or lifesustaining equipment are specifically not recommended without additional processing by

austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

## **Contact Information**

#### Headquarters

austriamicrosystems AG A-8141 Schloss Premstätten, Austria T. +43 (0) 3136 500 0 F. +43 (0) 3136 5692

For Sales Offices, Distributors and Representatives, please visit: http://www.austriamicrosystems.com/contact