ISL58115

# OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

**DATASHEET**

FN6671 Rev 1.00 July 29, 2013

Laser Diode Driver with APC Amplifier for Printers

The ISL58115 is a high-performance laser driver that provides controlled current to grounded laser diodes. A bias current is summed with the switched current at the IOUT output, allowing the user to optimize laser diode performance.

Output switched current flows when the LVDS signal DATA is high. The output current returns to the fixed-threshold value when DATA is low. Complete  $I_{OUT}$  shut-off is achieved by holding the CHPEN low, which will override all other control pins.

A fast settling APC amplifier connects directly to the monitor diode. The ISL58115 does not exhibit any time-dependent droop since the calibration gain is stored as a digital number.

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2) | PART<br>MARKING | PACKAGE<br>Tape & Reel<br>(Pb-free) | PKG.<br>DWG. # |

|-----------------------------|-----------------|-------------------------------------|----------------|

| ISL58115CRZ-T13             | 58115 CRZ       | 24 Ld QFN                           | L24.4x5B       |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### **Features**

- · Voltage-controlled Output Current Source

- Very Few External Components Needed

- Internal LVDS Termination Resistors

- 300MHz Switching

- Up to 110mA Output Current

- Rise Time < 500ps

- Fall Time < 500ps

- · APC Loop for Write Power Control

- · Fast Settling APC Amplifier

- Single +5V Supply (±10%)

- Disable Feature for Power-Up Protection and Conserving Power

- Zero Droop

- · Pb-Free (RoHS compliant)

# **Load Configuration**

• Common-cathode LD, Common-anode PD

# **Applications**

- · Laser Printer Applications

- Laser Diode Current Switching

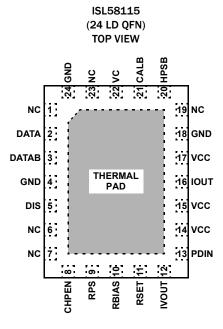

# **Pin Configuration**

# **Pin Descriptions**

| PIN<br>NAME    | PIN<br>NUMBER      | I/O | TYPE       | DESCRIPTION                                                                                                                                    |  |

|----------------|--------------------|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DATA           | 2                  | I   | LVDS       | Input data to control Laser Switching Control                                                                                                  |  |

| DATAB          | 3                  | I   | LVDS       | Input data to control Laser Switching Control                                                                                                  |  |

| GND            | 4, 18, 24          |     | Ground     | Ground                                                                                                                                         |  |

| DIS            | 5                  | I   | Digital    | Disable output current                                                                                                                         |  |

| NC             | 1, 6, 7, 19,<br>23 | I   | No connect | No connect                                                                                                                                     |  |

| CHPEN          | 8                  | I   | Digital    | Chip Enable; Pull High to Enable                                                                                                               |  |

| RPS            | 9                  | I   | Analog     | External resistor sets the Hsync detection power                                                                                               |  |

| RBIAS          | 10                 |     | Analog     | Resistors set bias threshold current. See "Applications Information" on page 7 for more detail                                                 |  |

| RSET           | 11                 | 0   | Analog     | Bandgap derived internal reference                                                                                                             |  |

| IVOUT          | 12                 | 0   | Analog     | Calibrate channel with an external trimpot to GND Adjust the IV amplifier gain                                                                 |  |

| PDIN           | 13                 | I   | Analog     | Photo Diode input to the IV amplifier                                                                                                          |  |

| vcc            | 14, 15, 17         |     | Power      | Supply Voltage                                                                                                                                 |  |

| IOUT           | 16                 | 0   | Analog     | Laser Current Output                                                                                                                           |  |

| HPSB           | 20                 | I   | TLL        | Hsync Power Select Enable; Active Low. During HPSB is low <u>AND</u> Hsync signal from photo detector is low, the output current is set by RPS |  |

| CALB           | 21                 | I   | TTL        | Samples the laser power for APC; Active Low                                                                                                    |  |

| vc             | 22                 | I   | Analog     | Voltage Controlling Laser Switching Current; OV to 2V input for 0% to 100% output                                                              |  |

| Thermal<br>Pad | -                  |     |            | Exposed Thermal Pad should be soldered to GND                                                                                                  |  |

NOTE: Pins with the same name are not necessary internally connected together. LDD pins must not be used for connecting together external components or features.

### Absolute Maximum Ratings (TA = +25°C)

| Voltages Applied to:                           |

|------------------------------------------------|

| V <sub>CC</sub> 0.5V to 6.0V                   |

| All Inputs                                     |

| I <sub>OUT</sub> 0.5V to V <sub>CC</sub>       |

| LVDS Max Current Inputs 5mA                    |

| ESD Rating                                     |

| Human Body Model (Tested per JESD22-A114F) 3kV |

| Charged Device Model (Tested per JESD22-C110D) |

| Machine Model (Tested per JESD22-A115B) 200V   |

| Latch Up (Tested per JESD78B)                  |

### **Recommended Operating Conditions**

| Thermal Resistance (Typical, Notes 3, 4)         | $\theta_{JA}(^{c}C/W)$ |

|--------------------------------------------------|------------------------|

| 24 Ld QFN                                        | 42                     |

| Operating Ambient Temperature Range              | . 0°C to +85°C         |

| Maximum Junction Temperature                     | +150°C                 |

| Storage Temperature Range6                       | 65°C to +150°C         |

| Pb-Free Reflow Profile                           | . see link below       |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 4. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

### Electrical Specifications $V_{CC}$ = 5.0V, DIS = Lo, $T_A$ = +25°C, $R_{SET}$ = 3.0k $\Omega$ , unless otherwise indicated.

| PARAMETER                | DESCRIPTION                        | CONDITIONS                     | MIN<br>(Note 5) | TYP | MAX<br>(Note 5) | UNIT |

|--------------------------|------------------------------------|--------------------------------|-----------------|-----|-----------------|------|

| V <sub>CC</sub>          | Supply Voltage                     |                                | 4.5             | 5.0 | 5.5             | V    |

| ISdis                    | Supply Current (Disabled)          | DIS = SLPEN = HPSB = Hi        |                 | 0.3 | 1.0             | mA   |

| IS2                      | Supply Current (Standby)           | DIS = Hi                       |                 | 22  | 31              | mA   |

| V <sub>LO</sub>          | Low Voltage Threshold              | All TTL inputs                 |                 |     | 1.2             | V    |

| V <sub>HI</sub>          | High Voltage Threshold             | All TTL inputs                 | 2.8             |     |                 | V    |

| I <sub>LO</sub>          | Input Low Current                  | All TTL inputs                 | -20             | -10 |                 | μΑ   |

| I <sub>HI</sub>          | Input High Current                 | All TTL inputs                 |                 |     | 1               | μΑ   |

| V <sub>SHUT</sub>        | VCC Shut Down Voltage              |                                |                 | 2.5 | 2.9             | V    |

| V <sub>LVDS</sub>        | LVDS Input Level                   | Differential, with Vcm = 1.25V |                 | 0.2 |                 | V    |

| V <sub>CMR</sub>         | LVDS Common Mode Voltage Range     | 300mV <sub>P-P</sub>           | 0.2             |     | 2.2             | V    |

| v <sub>c</sub>           | Control Voltage                    |                                | 0.3             |     | 2.6             | V    |

| R <sub>Termination</sub> | Internal LVDS Termination Resistor |                                |                 | 180 |                 | Ω    |

### $\textbf{Laser Amplifier Output} \qquad \text{$V_{CC} = 5.0$V$, DIS = Lo, $T_A = +25°C$, $R_{SET} = 3.0$k$\Omega$, unless otherwise indicated.}$

| PARAMETER                | DESCRIPTION                           | CONDITIONS                                               | MIN<br>(Note 5) | TYP | MAX<br>(Note 5) | UNIT |

|--------------------------|---------------------------------------|----------------------------------------------------------|-----------------|-----|-----------------|------|

| l <sub>OUT</sub>         | '                                     |                                                          | •               |     |                 | '    |

| IOUT <sub>SW-max</sub>   | Switched Output Current               | VC = 2.6V                                                | 75              | 81  |                 | mA   |

| IOUT <sub>BIAS-max</sub> | Bias Output Current                   | R <sub>BIAS</sub> = 1kΩ                                  | 20              | 35  |                 | mA   |

| l <sub>OFF</sub>         | Output Off Current                    | DIS pin set to HIGH                                      | -75             | 0   | +75             | μΑ   |

| FREQ <sub>OP</sub>       | Operating Frequency                   | I <sub>OUT</sub> = maximum switch current                | 200             |     |                 | MHz  |

| IOUT <sub>PSRR</sub>     | I <sub>OUT</sub> Supply Sensitivity   | I <sub>OUT</sub> = 20mA, V <sub>CC</sub> = 5V ±10%       |                 | 13  |                 | %/V  |

| t <sub>R-IOUT</sub>      | I <sub>OUT</sub> Rise Time            | 10% to 90%; typical LD for printer                       |                 | 0.5 |                 | ns   |

| t <sub>F-IOUT</sub>      | I <sub>OUT</sub> Fall Time            | 90% to 10%; typical LD for printer                       |                 | 0.7 |                 | ns   |

| OUTENx_t <sub>on</sub>   | I <sub>OUT</sub> on Propagation Delay | DATAx crossing to I <sub>OUT</sub> at 50% of final value |                 | 5   | 7               | ns   |

# **Laser Amplifier Output** $V_{CC} = 5.0V$ , DIS = Lo, $T_A = +25$ °C, $R_{SET} = 3.0$ kΩ, unless otherwise indicated.

| PARAMETER        | DESCRIPTION     | CONDITIONS | MIN<br>(Note 5) | TYP | MAX<br>(Note 5) | UNIT |   |

|------------------|-----------------|------------|-----------------|-----|-----------------|------|---|

| VC <sub>BW</sub> | Bandwidth of VC |            |                 | 14  |                 | MHz  | 1 |

## APC Electrical Specifications $V_{CC} = 5.0V$ , DIS = Lo, $T_A = +25$ °C, $R_{SET} = 3.0k\Omega$ , unless otherwise indicated.

| PARAMETER           | DESCRIPTION       | CONDITIONS                          | MIN<br>(Note 5) | ТҮР | MAX<br>(Note 5) | UNIT |

|---------------------|-------------------|-------------------------------------|-----------------|-----|-----------------|------|

| t <sub>APC-50</sub> | APC Response Time | OV to 2V step of VC                 |                 | 7.5 |                 | μs   |

| IVgain              | IV Amplifier Gain | External resistor RIV = $500\Omega$ |                 | 3.1 |                 | kΩ   |

#### NOTE:

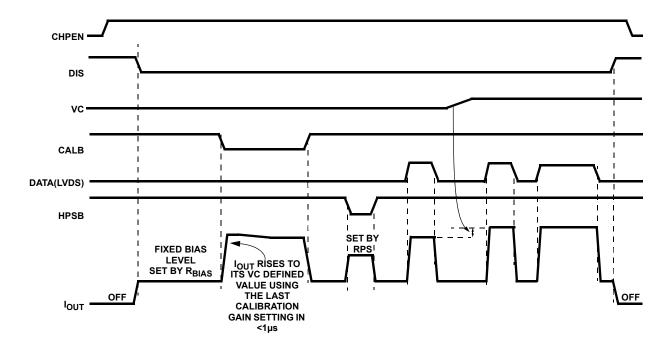

# **Timing Diagram**

<sup>5.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

# **I<sub>OUT</sub> Control**

| CHPEN        | DIS          | DATA       | CALB                   | HPSB                                  | louт                       | COMMENTS                                  |  |

|--------------|--------------|------------|------------------------|---------------------------------------|----------------------------|-------------------------------------------|--|

| POWER-DOW    | /N (SLEEP MO | DDE)       |                        |                                       |                            |                                           |  |

| 0            | х            | х          | х                      | х                                     | OFF                        | CHPEN is slow to enable                   |  |

| STANDBY (FU  | JLL STANDBY  | CURRENT, N | IO I <sub>OUTS</sub> ) | 1                                     |                            |                                           |  |

| 1            | 1            | х          | х                      | х                                     | OFF                        | Full standby current, no I <sub>OUT</sub> |  |

| NORMAL DR    | IVE          | *          | •                      | · · · · · · · · · · · · · · · · · · · | •                          |                                           |  |

| 1            | 0            | х          | 1                      | 1                                     | ON, BIAS ONLY              |                                           |  |

| 1            | 0            | х          | 0                      | 1                                     | ON, CAL to level set by VC |                                           |  |

| 1            | 0            | 1          | 1                      | 1                                     | ON                         |                                           |  |

| Hsync POWER  | ?            |            |                        |                                       |                            |                                           |  |

| 1            | 0            | х          | 1                      | 0                                     | Hsync power                | Output current defined by RPS             |  |

| INVALID LOGI | C COMBINATIO | )N         |                        |                                       | ,                          |                                           |  |

| 1            | 0            | х          | 1                      | х                                     | INVALID                    |                                           |  |

NOTE: DATA1 and DATA2: 1 implies DATA>DATAB, 0 implies DATA<DATAB

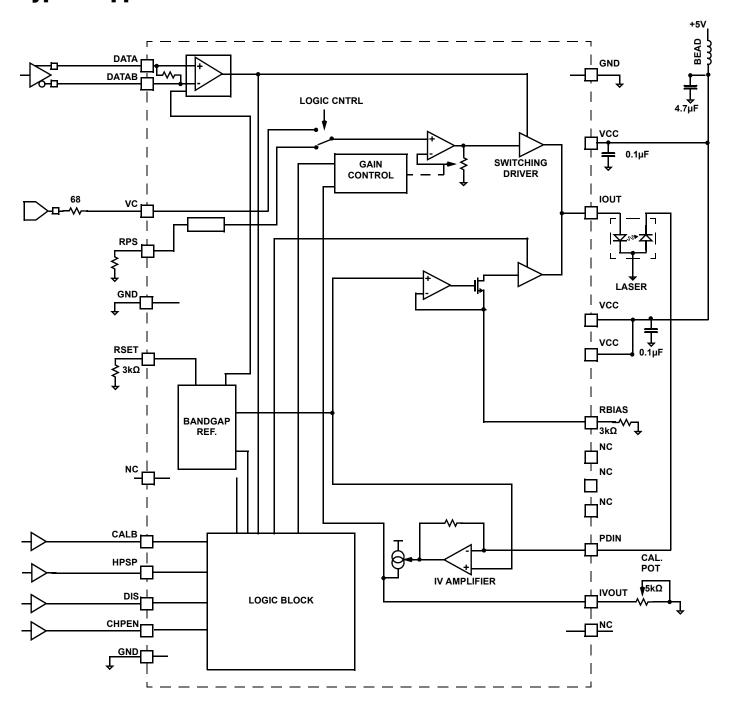

# **Typical Application**

Page 6 of 9

# **Applications Information**

#### **APC System Overview**

As the laser heats up (or ages) its output power declines relative to the applied current, so some form of power control is required. The laser is optically coupled to a photo-diode, so that the laser's optical output can be measured. Laser optical output power is controlled by comparing the externally applied control voltage with the voltage produced by the IV-amplifier which converts the photo-diode's output current into a voltage. Since the calibrated gain is stored as a digital number in a register, the ISL58115 exhibits none of the time-dependent droop that is seen in most printers' laser diode drivers. This is of particular importance during high dot/inch graphics modes where the line may be slowed down very significantly to allow 2400 dots per inch or even more.

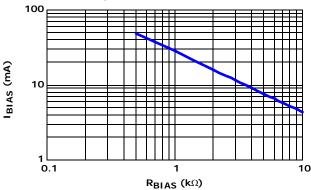

#### **Fixed-Threshold Laser Bias Control**

When a laser is driven from below threshold to well above threshold, it exhibits a few cycles of a damped oscillation. The amplitude of this oscillation is minimized when the laser is kept above threshold. The "fixed" bias mode is set by asserting a logic Low on the SLPEN pin. To set the laser bias threshold currents, I<sub>BIAS</sub>, connect external resistors from RBIAS pins to GND. Figure 1 shows value of R<sub>BIAS</sub> corresponding to desired bias current.

FIGURE 1. RBIAS VS BIAS CURRENT

### **Scaling External Resistors**

$R_{SET}$  is used to scale the switching output current. Switching output current,  $I_{SW}$ , is the function of VC and  $R_{SET}$ .

$$I_{SW} = I_{SW}Gain \times \left(\frac{VC}{R_{DAC}} - \frac{2}{R_{SET}}\right)$$

(EQ. 1)

Where  $I_{SW}Gain = \sim 17$ ,  $R_{DAC} = 400\Omega$ .

$R_{BIAS}$  sets bias threshold current. Figure 1 exhibits the relationship between  $I_{BIAS}$  and  $R_{BIAS}$ . The bias current is set as Equation 2:

$$I_{BIAS} = BiasChannelGain \times \frac{InternalVref}{R_{BIAS}}$$

(EQ. 2)

Where BiasChannelGain = ~40, InternalVref = 1.0V.

### **Controlling the Sampling**

The switching levels are sampled independently. This can be done during the "off-paper" period.

During calibration mode, the internal servo control will bring the laser diode output power level to match the voltage control level set by VC voltage.

### **Horizontal edge detection**

When HPSB is low, the output current is set by RPS. Asserting HPSB low overrides both channel data inputs. HPSB should not be asserted low during a calibration cycle. When HPSB is low, the desired output current  $I_{RPS}$  is governed by the following equation:

$$IRPS = 40 \times \frac{RPS}{CaIDAC} \times \frac{1.05V}{RSET}$$

(EQ. 3)

where the CalDAC setting (from the last write power calibration) ensures laser temperature and aging compensation. The CalDAC's units are ohms. Full scale is about  $380\Omega$  and CalDAC is defined as CalDAC =  $255/\text{code}*380\Omega$ .

The horizontal sync pulse is meant to be a power level that overrides VC calibration and sets the output current to a fixed level

### **Typical Application**

Upon the printer being powered up, the lasers should be calibrated. This would establish nominal light power outputs, typically a few milliwatts at the laser regardless of the ambient temperature and also any laser aging.

Once everything is ready for printing, the paper is in position and the mirror-motor is phase-locked then the print line(s) can be written. Before, or after, the beam is over the photo-sensitive drum, each laser can be re-calibrated. This continual recalibration will compensate for any temperature drift of the laser, especially at the initial warming up period.

Since the calibrated gain is stored as a digital number in a register, the ISL58115 exhibits no time-dependent droop. With no droop to degrade performance the only limitation now is the lasers' own temperature change along the line. This in turn can be compensated for to some extent by adding a data-dependent compensation signal to the analog VCx input pin. It may be found that in fast draft modes for example, that the laser temperature change is sufficiently small that many lines can be written before the laser(s) need to be re-calibrated. If the printed page has a low enough duty cycle, no re-calibration may be needed at all.

The ISL58115 has analog voltage inputs to allow the laser power level to be adjusted during the line. Typically this would be driven with a PWM, low bandwidth signal to compensate for the differing beam path length as the beam is swept from one side of the page to the other.

Undervoltage, overcurrent and over-temperature error conditions are ORed together and made available on the ERRB pin.

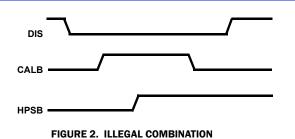

### **Note on Illegal Logic Combination**

In normal use, CALB going low (active) without DIS being low (active) would be meaningless. Likewise with HPSB going low (active). Therefore, a combination of these should be avoided at all times. If this combination is applied, the chip will not work properly. To exit this mode, either set CALB to Low or/and DIS to Hi.

### **Power Supply Decoupling**

Due to the high values of current being switched rapidly on and off, it is important to ensure that the power supply is well decoupled to ground. During switching, the  $V_{CC}$  undergoes severe current transients, thus every effort should be made to decouple the  $V_{CC}$  as close to the package as possible. Symptoms that could arise include poor rise/fall times, current overshoot, and poor settling response. It is recommended that VCC inputs should be bypassed with  $4.7\mu F//100nF//470pF$  to GND

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE          | REVISION | CHANGE                              |  |  |  |

|---------------|----------|-------------------------------------|--|--|--|

| July 29, 2013 | FN7659.1 | onversion to New Intersil Template. |  |  |  |

| June 15, 2010 | FN7659.0 | itial release.                      |  |  |  |

### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at www.intersil.com.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com/en/support/ask-an-expert.html">www.intersil.com/en/support/ask-an-expert.html</a>. Reliability reports are also available from our website at <a href="https://www.intersil.com/en/support/qualandreliability.html#reliability">https://www.intersil.com/en/support/qualandreliability.html#reliability</a>

© Copyright Intersil Americas LLC 2010-2013. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

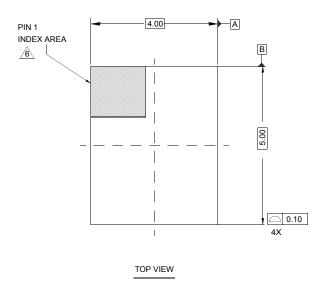

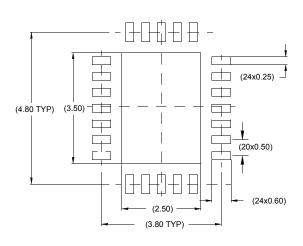

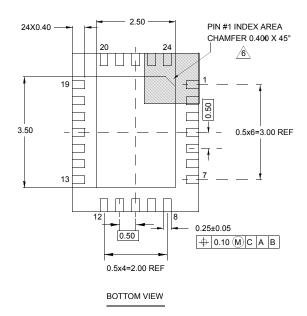

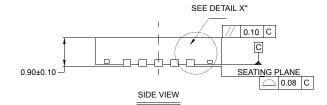

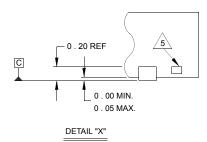

# **Package Outline Drawing**

### L24.4x5B

# 24 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 0, 10/06

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.20mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.