www.ti.com

SNAS073D – JUNE 1999 – REVISED MARCH 2013

# ADC08061/ADC08062 500 ns A/D Converter with S/H Function and Input Multiplexer

Check for Samples: ADC08061, ADC08062

### **FEATURES**

- 1 or 2 Input Channels

- No External Clock Required

- Analog Input Voltage Range from GND to V<sup>+</sup>

- Overflow Output for Cascading (ADC08061)

- ADC08061 Pin-Compatible with the ADC0820

### **APPLICATIONS**

- Mobile Telecommunications

- Hard Disk Drives

- Instrumentation

- High-Speed Data Acquisition Systems

### **KEY SPECIFICATIONS**

- Resolution 8 Bits

- Conversion Time 560 ns Max (WR-RD Mode)

- Full Power Bandwidth 300 kHz

- Throughput Rate 1.5 MHz

- Power Consumption 100 mW Max

- Total Unadjusted Error ±1/2 LSB and ±1 LSB

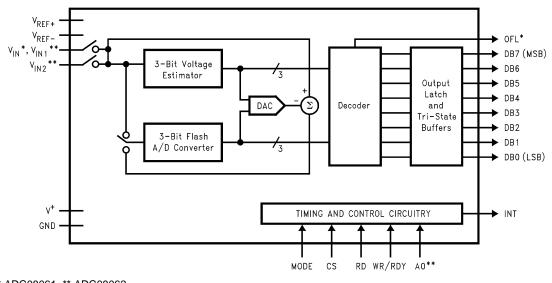

### **Block Diagram**

### DESCRIPTION

**NOTE:** These products are obsolete. This data sheet is provided for reference only.

Using a patented multi-step A/D conversion technique, the 8-bit ADC08061 and ADC08062 CMOS ADCs offer 500 ns (typ) conversion time, internal sample-and-hold (S/H), and dissipate only 125 mW of power. The ADC08062 has a two-channel multiplexer. The ADC08061/2 performs 8-bit conversions using a multistep flash approach.

Input track-and-hold circuitry eliminates the need for an external sample-and-hold. The ADC08061/2 performs accurate conversions of full-scale input signals that have a frequency range of DC to 300 kHz (full-power bandwidth) without need of an external S/H.

The digital interface has been designed to ease connection to microprocessors and allows the parts to be I/O or memory mapped.

\* ADC08061, \*\* ADC08062

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

TEXAS INSTRUMENTS

www.ti.com

SNAS073D-JUNE 1999-REVISED MARCH 2013

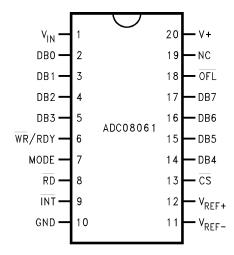

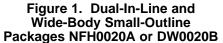

### **Connection Diagrams**

**PIN DESCRIPTIONS**

www.ti.com

#### SNAS073D - JUNE 1999-REVISED MARCH 2013

| V <sub>IN</sub> , V <sub>IN1-8</sub> | These are analog inputs. The input range is GND–50 mV $\leq$ V <sub>IN</sub> and the ADC08062 has a two-channel multiplexer (V <sub>IN1-2</sub> ).                                                                                                                                                                                                                                                          | $_{PUT} \leq V^{+} + 50 \text{ mV}$ . The ADC08061 has a single input (V <sub>IN</sub> )                            |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| DB0-DB7                              | TRI-STATE data outputs—bit 0 (LSB) through bit 7 (MSB).                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |  |  |  |

| WR /RDY                              | WR-RD Mode (Logic high applied to MODE pin)                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |  |  |  |

|                                      | $\overline{WR}$ : With $\overline{CS}$ low, the conversion is started on the falling edge of $\overline{WR}$ . The digital result will be strobed into the output latch at the end of conversion (see Figure 8, Figure 9, and Figure 10).                                                                                                                                                                   |                                                                                                                     |  |  |  |

|                                      | <b>RD</b> Mode (Logic low applied to MODE pin)                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |  |  |  |

|                                      | <b>RDY:</b> This is an open drain output (no internal pull-up device). at the end of conversion.                                                                                                                                                                                                                                                                                                            | RDY will go low after the falling edge of $\overline{\text{CS}}$ and return high                                    |  |  |  |

| MODE                                 | <b>Mode:</b> Mode ( <b>RD</b> or <b>WR-RD</b> ) selection input—This pin is pulled left unconnected.                                                                                                                                                                                                                                                                                                        | $d$ to a logic low through an internal 50 $\mu A$ current sink when                                                 |  |  |  |

|                                      | <b>RD</b> Mode is selected if the MODE pin is left unconnected or ex<br>by pulling RD low until output data appears.                                                                                                                                                                                                                                                                                        | ternally forced low. A complete conversion is accomplished                                                          |  |  |  |

|                                      | <b>WR-RD</b> Mode is selected when a high is applied to the MODE then using RD to access the data.                                                                                                                                                                                                                                                                                                          | pin. A conversion starts with the $\overline{WR}$ signal's rising edge and                                          |  |  |  |

| RD                                   | WR-RD Mode (logic high on the MODE pin) This is the active line TRI-STATE data outputs (DB0–DB7) will be activated when RD RD Mode (logic low on the MODE pin)<br>With CS low, a conversion starts on the falling edge of RD. Out Figure 7 and Figure 11).                                                                                                                                                  | goes low (Figure 8, Figure 9, and Figure 10).                                                                       |  |  |  |

| INT                                  | This is an active low output that indicates that a conversion is complete and the data is in the output latch. INT is reset by the rising edge of RD.                                                                                                                                                                                                                                                       |                                                                                                                     |  |  |  |

| GND                                  |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |  |  |  |

| $V_{REF-}, V_{REF+}$                 |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |  |  |  |

|                                      | For the ADC08062, an input voltage on any unselected input more than 100 mV will create errors in a selected channel that                                                                                                                                                                                                                                                                                   | that exceeds V <sup>+</sup> by more than 100 mV or is below GND by is operating within proper operating conditions. |  |  |  |

| CS                                   | This is the active low Chip Select input. A logic low signal appli-<br>the CS signal is ORed with RD and WR signals.                                                                                                                                                                                                                                                                                        | ed to this input pin enables the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ inputs. Internally,              |  |  |  |

| OFL                                  | Overflow Output. If the analog input is higher than $V_{REF+} - \frac{1}{2} LSB$ , $\overline{OFL}$ will be low at the end of conversion. It can be used when cascading two ADC08061s to achieve higher resolution (9 bits). This output is always active and does not go into TRI-STATE as DB0–DB7 do. When $\overline{OFL}$ is set, all data outputs remain high when the ADC08061's output data is read. |                                                                                                                     |  |  |  |

| NC                                   | No connection.                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |  |  |  |

| A0                                   | This logic input is used to select one of the ADC08062's input multiplexer channels. A channel is selected as shown in the following table.                                                                                                                                                                                                                                                                 |                                                                                                                     |  |  |  |

|                                      | ADC08062<br>A0                                                                                                                                                                                                                                                                                                                                                                                              | Channel                                                                                                             |  |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>IN1</sub>                                                                                                    |  |  |  |

|                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>IN2</sub>                                                                                                    |  |  |  |

| V*                                   | Positive power supply voltage input. Nominal operating supply $\mu$ F bead tantalum in parallel with a 0.1 ceramic capacitor. Lead                                                                                                                                                                                                                                                                          |                                                                                                                     |  |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

SNAS073D – JUNE 1999 – REVISED MARCH 2013

www.ti.com

STRUMENTS

### Absolute Maximum Ratings<sup>(1)(2)(3)</sup>

| V                                             |                                |                        |                                |

|-----------------------------------------------|--------------------------------|------------------------|--------------------------------|

| Supply Voltage (V <sup>+</sup> )              |                                |                        | 6V                             |

| Logic Control Inputs                          |                                |                        | -0.3V to V <sup>+</sup> + 0.3V |

| Voltage at Other Inputs and Outputs           |                                |                        | -0.3V to V <sup>+</sup> + 0.3V |

| Input Current at Any Pin <sup>(4)</sup>       |                                |                        | 5 mA                           |

| Package Input Current <sup>(4)</sup>          |                                |                        | 20 mA                          |

| Power Dissipation <sup>(5)</sup> All Packages |                                |                        | 875 mW                         |

| Storage Temperature                           | -65°C to +150°C                |                        |                                |

|                                               | J Package (Soldering, 10 sec.) |                        | +300°C                         |

| Lood Tomperature                              | N Package (Soldering, 10 sec.) |                        | +260°C                         |

| Lead Temperature                              |                                | (Vapor Phase, 60 sec.) | +215°C                         |

|                                               | WM Package                     | (Infrared, 15 sec.)    | +220°C                         |

| ESD Susceptibility <sup>(6)</sup>             |                                |                        | 2 kV                           |

(1) All voltages are measured with respect to the GND pin, unless otherwise specified.

(2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supply voltage (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sup>+</sup>), the absolute value of the current at that pin should be limited to 5 mA or less. The 20 mA package input current specification limits the number of pins that can exceed the power supply boundaries with a 5 mA current limit to four.

- (5) The power dissipation of this device under normal operation should never exceed 875 mW (Quiescent Power Dissipation + the loads on the digital outputs). Caution should be taken not to exceed absolute maximum power rating when the device is operating in a severe fault condition (e.g., when any input or output exceeds the power supply). The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub> (maximum junction temperature), θ<sub>JA</sub> (package junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is PD<sub>max</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower. See T<sub>JMAX</sub> and θ<sub>JA</sub> Details for the various packages and versions of the ADC08061/2.

- (6) Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

### **Operating Ratings**<sup>(1)(2)</sup>

| Temperature Range ( $T_{MIN} \le T_A \le T_{MAX}$ ) | $-40^{\circ}C \le T_{A} \le 85^{\circ}C$   |

|-----------------------------------------------------|--------------------------------------------|

| Supply Voltage, (V <sup>+</sup> )                   | +4.5V to +5.5V                             |

| Pos. Reference Voltage, V <sub>REF+</sub>           | (V <sub>REF-</sub> + 1V) to V <sup>+</sup> |

| Neg. Reference Voltage, V <sub>REF-</sub>           | GND to (V <sub>REF+</sub> - 1V)            |

| Input Voltage Range                                 | V <sub>REF-</sub> to V <sub>REF+</sub>     |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

(2) All voltages are measured with respect to the GND pin, unless otherwise specified.

#### www.ti.com

#### **Converter Characteristics**

The following specifications apply for  $\overline{RD}$  Mode, V<sup>+</sup> = 5V, V<sub>REF+</sub> = 5V, and V<sub>REF-</sub> = GND unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>;** all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C.

| Symbol            | Parameter                             | Conditions                                                            | Typical <sup>(1)</sup> | Limits <sup>(2)</sup> | Units<br>(Limit) |

|-------------------|---------------------------------------|-----------------------------------------------------------------------|------------------------|-----------------------|------------------|

| INU               |                                       | ADC08061/2BIN                                                         |                        | ±1/2                  | LSB (max)        |

| INL               | Integral Non Linearity                | ADC08061/2CIWM                                                        |                        | ±1                    | LSB (max)        |

| TUE               | Total Unadjusted Error <sup>(3)</sup> | ADC08061/2BIN                                                         |                        | ±1/2                  | LSB (max)        |

| IUE               | Total Unadjusted Error                | ADC08061/2CIWM                                                        |                        | ±1                    | LSB (max)        |

|                   | Missing Codes                         |                                                                       |                        | 0                     | Bits (max)       |

|                   | Defense a land Decision               |                                                                       | 700                    | 500                   | Ω(min)           |

|                   | Reference Input Resistance            |                                                                       | 700                    | 1250                  | Ω (max)          |

| N/                |                                       |                                                                       |                        | V <sub>REF-</sub>     | V (min)          |

| V <sub>REF+</sub> | Positive Reference Input Voltage      |                                                                       |                        | V*                    | V (max)          |

| N/                | Negative Reference Input Voltage      |                                                                       |                        | GND                   | V (min)          |

| V <sub>REF-</sub> |                                       |                                                                       |                        | V <sub>REF+</sub>     | V (max)          |

|                   | Analog Input Voltage                  | See <sup>(4)</sup>                                                    |                        | GND - 0.1             | V (min)          |

| V <sub>IN</sub>   |                                       | See                                                                   |                        | V <sup>+</sup> + 0.1  | V (max)          |

|                   |                                       | On Channel Input = 5V, Off Channel Input = $0V^{(5)}$                 | -0.4                   | -20                   | µA (max)         |

|                   | On Channel Input Current              | On Channel Input = 0V, Off Channel Input = $5V^{(5)}$                 | -0.4                   | -20                   | µA (max)         |

| PSS               | Power Supply Sensitivity              | V <sup>+</sup> = 5V ±5%, V <sub>REF</sub> = 4.75V<br>All Codes Tested | ±1/16                  | ±1/2                  | LSB (max)        |

|                   | Effective Bits                        |                                                                       | 7.8                    |                       | Bits             |

|                   | Full-Power Bandwidth                  |                                                                       | 300                    |                       | kHz              |

| THD               | Total Harmonic Distortion             |                                                                       | 0.5                    |                       | %                |

| S/N               | Signal-to-Noise Ratio                 |                                                                       | 50                     |                       | dB               |

| IMD               | Intermodulation Distortion            |                                                                       | 50                     |                       | dB               |

(1) Typical figures are at 25°C and represent most likely parametric norm.

(2) Limits are specified to TI's AOQL (Average Output Quality Level).

(3) Total unadjusted error includes offset, full-scale, and linearity errors.

(4) Two on-chip diodes are tied to each analog input and are reversed biased during normal operation. One is connected to V<sup>+</sup> and the other is connected to GND. They will become forward biased and conduct when an analog input voltage is equal to or greater than one diode drop above V<sup>+</sup> or below GND. Therefore, caution should be exercised when testing with V<sup>+</sup> = 4.5V. Analog inputs with magnitudes equal to 5V can cause an input diode to conduct, especially at elevated temperatures. This can create conversion errors for analog signals near full-scale. The specification allows 50 mV forward bias on either diode; e.g., the output code will be correct as long as the analog input signal does not exceed the supply voltage by more than 50 mV. Exceeding this range on an unselected channel will corrupt the reading of a selected channel. An absolute analog input signal voltage range of 0V ≤ V<sub>IN</sub> ≤ 5V can be achieved by ensuring that the minimum supply voltage applied to V<sup>+</sup> is 4.950V over temperature variations, initial tolerance, and loading.

(5) Off-channel leakage current is measured after the on-channel selection.

SNAS073D-JUNE 1999-REVISED MARCH 2013

www.ti.com

### **AC Electrical Characteristics**

The following specifications apply for  $V^+ = 5V$ ,  $t_r = t_f = 10$  ns,  $V_{REF+} = 5V$ ,  $V_{REF-} = 0V$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol            | Parameter                                                                                                   | Condition                                                                              | Typical <sup>(1)</sup> | Limits <sup>(2)</sup> | Units<br>(Limit) |

|-------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|-----------------------|------------------|

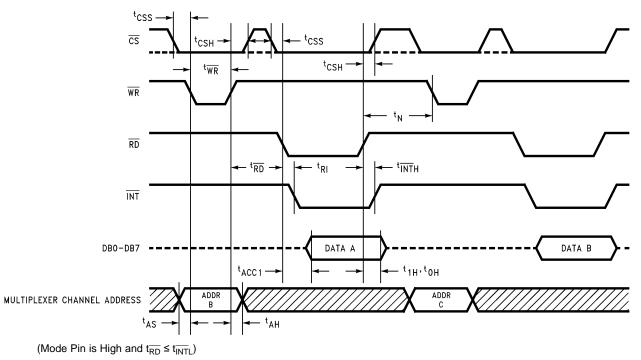

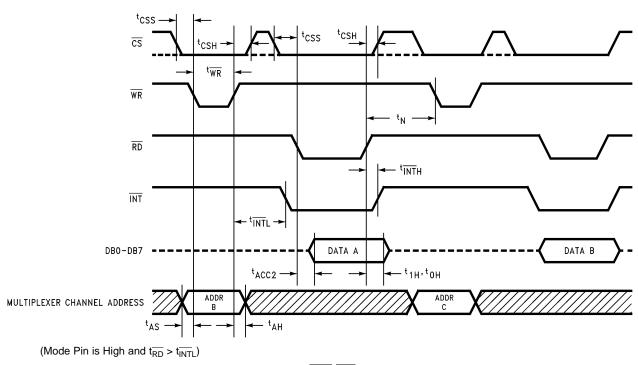

| t <sub>WR</sub>   | Write Time                                                                                                  | Mode Pin to V <sup>+</sup> ;<br>(Figure 8, Figure 9, and Figure 10)                    | 100                    | 100                   | ns (min)         |

| t <sub>RD</sub>   | Read Time (Time from Falling Edge of WR to Falling Edge of RD )                                             | Mode Pin to V <sup>+</sup> ; (Figure 8)                                                | 350                    | 350                   | ns (min)         |

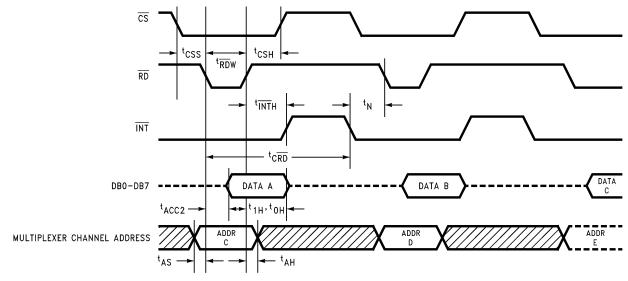

| t <sub>RDW</sub>  | RD Width                                                                                                    | Mode Pin to GND; (Figure 11)                                                           | 200                    | 250                   | ns (min)         |

| RDW               |                                                                                                             |                                                                                        | 400                    | 400                   | ns (max)         |

| t <sub>CONV</sub> | $\overline{WR} - \overline{RD}$ Mode Conversion Time ( $t_{\overline{WR}} + t_{\overline{RD}} + t_{ACC1}$ ) | Mode Pin to V <sup>+</sup> ; (Figure 8)                                                | 500                    | 560                   | ns (max)         |

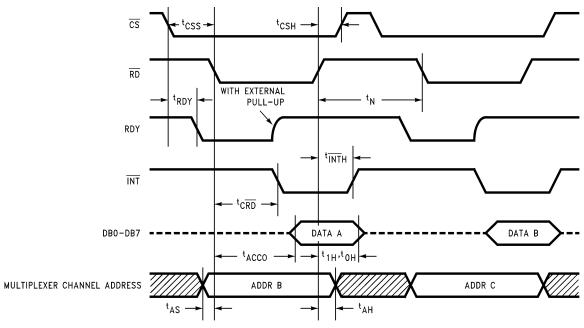

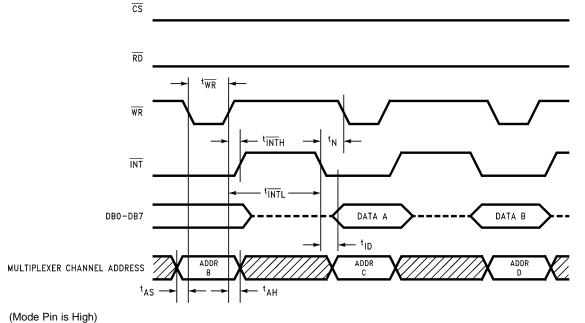

| t <sub>CRD</sub>  | RD Mode Conversion Time                                                                                     | Mode Pin to GND; (Figure 7)                                                            | 655                    | 900                   | ns (max)         |

| t <sub>ACCO</sub> | Access Time (Delay from Falling Edge of RD to Output Valid)                                                 | $C_L \le 100 \text{ pF}$ Mode Pin to GND;<br>(Figure 7)                                | 640                    | 900                   | ns (max)         |

|                   | Access Time (Delay from Falling Edge                                                                        | Mode Pin to V <sup>+</sup> , $t_{\overline{RD}} \le t_{\overline{INTL}}$<br>(Figure 8) |                        |                       |                  |

| t <sub>ACC1</sub> | of RD to Output Valid)                                                                                      | C <sub>L</sub> = 10 pF                                                                 | 45                     | 110                   | ns (max)         |

|                   |                                                                                                             | C <sub>L</sub> ≤ 100 pF                                                                | 50                     |                       | ns               |

|                   | Access Time (Delay from Falling Edge                                                                        | t <sub>RD</sub> > t <sub>INTL</sub> ; (Figure 9 and<br>Figure 10)                      |                        |                       |                  |

| t <sub>ACC2</sub> | of RD to Output Valid)                                                                                      | C <sub>L</sub> ≤ 10 pF                                                                 | 25                     | 55                    | ns (max)         |

|                   |                                                                                                             | C <sub>L</sub> = 100 pF                                                                | 30                     |                       |                  |

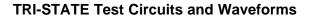

| t <sub>OH</sub>   | TRI-STATE Control (Delay from Rising Edge of RD to HI-Z State)                                              | $R_L = 3 \text{ k}\Omega, C_L = 10 \text{ pF}$                                         | 30                     | 60                    | ns (max)         |

| t <sub>1H</sub>   | TRI-STA <u>TE</u> Control (Delay from Rising Edge of RD to HI-Z State)                                      | $R_L = 3 \text{ k}\Omega, C_L = 10 \text{ pF}$                                         | 30                     | 60                    | ns (max)         |

| t <sub>INTL</sub> | Delay from Rising Edg <u>e of</u><br>WR to Falling Edge of INT                                              | (Figure 9 and Figure 10)<br>Mode Pin = V <sup>+</sup> , $C_L = 50 \text{ pF}$          | 520                    | 690                   | ns (max)         |

| t <sub>INTH</sub> | Delay from Rising Edge of RD to Rising Edge of INT                                                          | $C_L$ = 50 pF; (Figure 7, Figure 8,<br>Figure 9, and Figure 10)2b, and 4 )             | 50                     | 95                    | ns (max)         |

| t <sub>INTH</sub> | Delay from Rising Edge of WR to Rising Edge of INT                                                          | C <sub>L</sub> = 50 pF; (Figure 10)                                                    | 45                     | 95                    | ns (max)         |

| t <sub>RDY</sub>  | Delay from CS to RDY                                                                                        | Mode Pin = 0V, $C_L$ = 50 pF, $R_L$ = 3 k $\Omega$ (Figure 7)                          | 25                     | 45                    | ns (max)         |

| t <sub>ID</sub>   | Delay from INT to Output Valid                                                                              | $R_L = 3 k\Omega$ , $C_L = 100 pF$ ;<br>(Figure 10)                                    | 0                      | 15                    | ns (max)         |

| t <sub>RI</sub>   | Delay from RD to INT                                                                                        | Mode Pin = V <sup>+</sup> , $t_{RD} \le t_{INTL}$ ;<br>(Figure 9)                      | 60                     | 115                   | ns (max)         |

| t <sub>N</sub>    | Time between End of $\overline{\text{RD}}$ and Start of New Conversion                                      | (Figure 7, Figure 8, Figure 9,<br>Figure 10, and Figure 11)                            | 50                     | 50                    | ns (min)         |

| t <sub>AH</sub>   | Channel Address Hold Time                                                                                   | (Figure 7, Figure 8, Figure 9,<br>Figure 10, and Figure 11)                            | 10                     | 60                    | ns (min)         |

| t <sub>AS</sub>   | Channel Address Setup Time                                                                                  | (Figure 7, Figure 8, Figure 9, Figure 10, and Figure 11)                               | 0                      | 0                     | ns (max)         |

| t <sub>CSS</sub>  | CS Setup Time                                                                                               | (Figure 7, Figure 8, Figure 9, Figure 10, and Figure 11)                               | 0                      | 0                     | ns (max)         |

| t <sub>CSH</sub>  | CS Hold Time                                                                                                | (Figure 7, Figure 8, Figure 9,<br>Figure 10, and Figure 11)                            | 0                      | 0                     | ns (min)         |

| C <sub>VIN</sub>  | Analog Input Capacitance                                                                                    |                                                                                        | 25                     |                       | pF               |

| C <sub>OUT</sub>  | Logic Output Capacitance                                                                                    |                                                                                        | 5                      |                       | pF               |

| C <sub>IN</sub>   | Logic Input Capacitance                                                                                     |                                                                                        | 5                      |                       | pF               |

(1) Typical figures are at 25°C and represent most likely parametric norm.

(2) Limits are specified to TI's AOQL (Average Output Quality Level).

www.ti.com

### **DC Electrical Characteristics**

The following specifications apply for  $V^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol          | Parameter                | Conditions                                                                          | Typical <sup>(1)</sup> | Limits <sup>(2)</sup> | Units<br>(Limit) |

|-----------------|--------------------------|-------------------------------------------------------------------------------------|------------------------|-----------------------|------------------|

|                 |                          | V <sup>+</sup> = 5.5V                                                               |                        |                       |                  |

|                 |                          | Mode Pin                                                                            |                        | 3.5                   | V (min)          |

| V <sub>IH</sub> | Logic "1" Input Voltage  | ADC08062 CS, WR, RD, A0 Pins                                                        |                        | 2.2                   | V (min)          |

|                 |                          | ADC08061 CS, WR, RD Pins                                                            |                        | 2.0                   | V (min)          |

|                 |                          | $V^{+} = 4.5V$                                                                      |                        |                       |                  |

| ,               |                          | Mode Pin                                                                            |                        | 1.5                   | V (max)          |

| / <sub>IL</sub> | Logic "0" Input Voltage  | ADC08062 CS, WR, RD, A0 Pins                                                        |                        | 0.7                   | V (max)          |

|                 |                          | ADC08061 CS, WR, RD Pins                                                            |                        | 0.8                   | V (max)          |

|                 |                          | V <sub>IH</sub> = 5V                                                                |                        |                       |                  |

|                 |                          | CS, RD, A0 Pins                                                                     | 0.005                  | 1                     | μA (max)         |

| IH              | Logic "1" Input Current  | WR Pin                                                                              | 0.1                    | 3                     | μA (max)         |

|                 |                          | Mode Pin                                                                            | 50                     | 200                   | μA (max)         |

|                 | Logic "0" Input Current  | $V_{IL} = 0V$                                                                       |                        |                       |                  |

| IL              |                          | CS, RD, WR, A0 Pins                                                                 | -0.005                 |                       | µA (max)         |

|                 |                          | Mode Pin                                                                            |                        | -2                    |                  |

|                 |                          | V <sup>+</sup> = 4.75V                                                              |                        |                       |                  |

|                 |                          | I <sub>OUT</sub> = -360 μA                                                          |                        |                       |                  |

| √ <sub>он</sub> | Logic "1" Output Voltage | DB0–DB7, OFL, INT                                                                   |                        | 2.4                   | V (min)          |

|                 |                          | I <sub>OUT</sub> = -10 μA                                                           |                        |                       |                  |

|                 |                          | DB0–DB7, OFL, INT                                                                   |                        | 4.5                   | V (min)          |

| V <sub>OL</sub> | Logic "0" Output Voltage | V <sup>+</sup> = 4.75V <u>, I<sub>OUT</sub> = 1</u> .6 mA<br>DB0–DB7, OFL, INT, RDY |                        | 0.4                   | V (max)          |

|                 | TRI-STATE Output Current | $V_{OUT} = 5.0V$                                                                    | 0.4                    | 3                     | µA (max)         |

|                 |                          | DB0–DB7, RDY                                                                        | 0.1                    |                       |                  |

| 0               |                          | V <sub>OUT</sub> = 0V                                                               |                        | •                     |                  |

|                 |                          | DB0–DB7, RDY                                                                        | -0.1                   | -3                    | µA (max)         |

| SOURCE          | Output Source Current    | V <sub>OUT</sub> = 0V<br>DB0–DB7, OFL, INT                                          | -26                    | -6                    | mA (min)         |

| SINK            | Output Sink Current      | V <sub>OUT</sub> = 5V<br>DB0–DB7, OFL, INT, RDY                                     | 24                     | 7                     | mA (min)         |

| с               | Supply Current           | $\overline{CS} = \overline{WR} = \overline{RD} = 0$                                 | 11.5                   | 20                    | mA (max)         |

Typical figures are at 25°C and represent most likely parametric norm.

Limits are specified to TI's AOQL (Average Output Quality Level).

### $T_{JMAX}$ and $\theta_{JA}$ Details

| Part Number    | T <sub>JMAX</sub> | θ <sub>JA</sub> |

|----------------|-------------------|-----------------|

| ADC08061/2BIN  | 105               | 51              |

| ADC08061/2CIWM | 105               | 85              |

SNAS073D – JUNE 1999 – REVISED MARCH 2013

www.ti.com

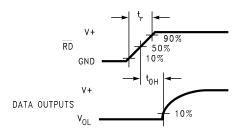

Figure 4.  $t_{1H}$ ,  $C_L = 10 \text{ pF}$

Figure 5. t<sub>oH</sub>

t<sub>r</sub> = 10 ns

Figure 6.  $t_{0H}$ ,  $C_L = 10 \text{ pF}$

# Timing Diagrams

www.ti.com

(Mode Pin is Low)

Figure 8. WR-RD Mode

Texas Instruments

SNAS073D – JUNE 1999 – REVISED MARCH 2013

www.ti.com

Reduced Interface System Connection ( $\overline{CS} = \overline{RD} = 0$ )

Figure 10. WR-RD Mode

SNAS073D - JUNE 1999-REVISED MARCH 2013

(Mode Pin is Low and  $\overline{t_{\text{RDW}}}$  must be between 200 ns and 400 ns)

Figure 11. RD Mode (Pipeline Operation)

800

750

700

650

600

550

0.5

0.4

0.3

0.2

0.1

0

1.5

1.4

1.3

1.2

1.1

1.0 -100

VOLTS (V)

0

1

2

$V^{+} = 4.5V$

0

-50

OFFSET ERROR (LSB)

-100

$V^{+} = 5$ .

=5.0

0

= 4

-50

TIME (ns)

www.ti.com

SNAS073D-JUNE 1999-REVISED MARCH 2013

t<sub>CRD</sub> vs. Temperature **Linearity Error** vs. Reference Voltage 0.6 V<sup>+</sup>=5V  $T_A = 25 °C$ 0.5 LINEARITY ERROR (LSB) 0.4 0.3 0.2 0.1 0 150 5 50 100 0 1 2 3 4 AMBIENT TEMPERATURE (°C) REFERENCE VOLTAGE (V) Figure 12. Figure 13. Supply Current vs. Temperature Offset Error vs. **Reference Voltage** 16 . V<sup>+</sup>=5∨ V+=5.5V  $T_{\Delta} = 25 °C$ 14 SUPPLY CURRENT (mA) v =5 12 V 4.5V 10 8 6 5 3 4 -100 -50 0 50 100 150 REFERENCE VOLTAGE (V) TEMPERATURE (°C) Figure 14. Figure 15. Logic Threshold vs. Temperature **Output Current** vs. Temperature 40  $V^{+} = 5V$ 30 I<sub>SINK</sub> OUTPUT CURRENT (mA) 20 V<sup>+</sup>=5.5V  $V^{+} = 5.0V$ 10 0 -10 -20 SOURCE -30 -40 50 100 150 -100 -50 0 50 100 150 TEMPERATURE (°C) TEMPERATURE (°C) Figure 16. Figure 17.

### **Typical Performance Characteristics**

SNAS073D - JUNE 1999-REVISED MARCH 2013

### **APPLICATION INFORMATION**

### FUNCTIONAL DESCRIPTION

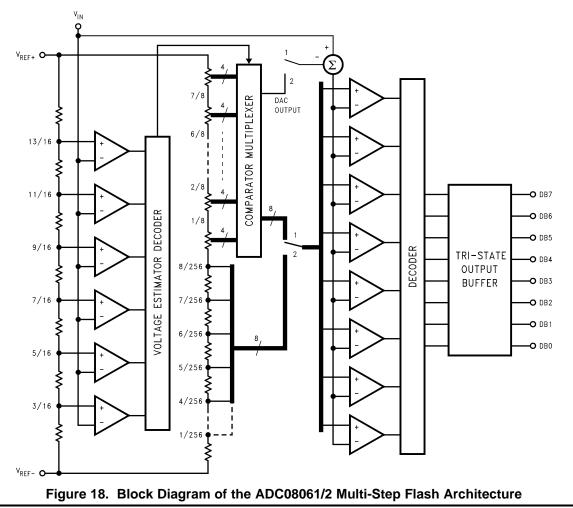

The ADC08061 and ADC08062 perform 8-bit analog-to-digital conversions using a multi-step flash technique. The first flash generates the five most significant bits (MSBs) and the second flash generates the three least significant bits (LSBs). Figure 18 shows the major functional blocks of the ADC08061/2's multi-step flash converter. It consists of an over-encoded 2½-bit Voltage Estimator, an internal DAC with two different voltage spans, a 3-bit half-flash converter and a comparator multiplexer.

The resistor string near the center of the block diagram in Figure 18 forms the internal main DAC. Each of the eight resistors at the bottom of the string is equal to 1/256 of the total string resistance. These resistors form the LSB Ladder and have a voltage drop of 1/256 of the total reference voltage ( $V_{REF+} - V_{REF-}$ ) across them. The remaining resistors make up the MSB Ladder. They are made up of eight groups of four resistors connected in series. Each MSB Ladder section has  $\frac{1}{8}$  of the total reference voltage across it. Within a given MSB Ladder section, each of the MSB resistors has 8/256, or 1/32 of the total reference voltage across it. Tap points are found between all of the resistors in both the MSB and LSB Ladders. Through the Comparator Multiplexer these tap points can be connected, in groups of eight, to the eight comparators shown at the right of Figure 18. This function provides the necessary reference voltages to the comparators during each flash conversion.

The six comparators, seven-resistor string (estimator DAC), and Estimator Decoder at the left of Figure 18 form the Voltage Estimator. The estimator DAC connected between  $V_{REF+}$  and  $V_{REF-}$  generates the reference voltages for the six Voltage Estimator comparators. These comparators perform a very low resolution A/D conversion to obtain an "estimate" of the input voltage. This estimate is then used to control the Comparator Multiplexer, connecting the appropriate MSB Ladder section to the eight flash comparators. Only 14 comparators, six in the Voltage Estimator and eight in the flash converter, are needed to achieve the full eight-bit resolution, instead of 32 comparators that would be needed by traditional half-flash methods.

#### SNAS073D – JUNE 1999 – REVISED MARCH 2013

A conversion begins with the Voltage Estimator comparing the analog input signal against the six tap voltages on the estimator DAC. The estimator decoder then selects one of the groups of tap points along the MSB Ladder. These eight tap points are then connected to the eight flash comparators. For example, if the analog input signal applied to  $V_{IN}$  is between 0 and 3/16 of  $V_{REF}$  ( $V_{REF} = V_{REF+} - V_{REF-}$ ), the estimator decoder instructs the comparator multiplexer to select the eight tap points between 8/256 and 2/8 of  $V_{REF}$  and connects them to the eight flash comparators. The first flash conversion is now performed, producing the five MSBs of data.

The remaining three LSBs are generated next using the same eight comparators that were used for the first flash conversion. As determined by the results of the MSB flash, a voltage from the MSB Ladder equivalent to the magnitude of the five MSBs is subtracted from the analog input voltage as the upper switch is moved from position one to position two. The resulting remainder voltage is applied to the eight flash comparators and, with the lower switch in position two, compared with the eight tap points from the LSB Ladder.

By using the same eight comparators for both flash conversions, the number of comparators needed by the multi-step converter is significantly reduced when compared to standard half-flash techniques.

Voltage Estimator errors as large as 1/16 of V<sub>REF</sub> (16 LSBs) will be corrected since the flash comparators are connected to ladder voltages that extend beyond the range specified by the Voltage Estimator. For example, if 7/16 V<sub>REF</sub> < V<sub>IN</sub> < 9/16 V<sub>REF</sub> the Voltage Estimator's comparators tied to the tap points below 9/16 V<sub>REF</sub> will output "1"s (000111). This is decoded by the estimator decoder to "10". The eight flash comparators will be placed at the MSB Ladder tap points between  $\frac{3}{8}$  V<sub>REF</sub> and  $\frac{5}{8}$  V<sub>REF</sub>. The overlap of 1/16 V<sub>REF</sub> on each side of the Voltage Estimator's span will automatically correct an error of up to 16 LSBs (16 LSBs = 312.5 mV for V<sub>REF</sub> = 5V). If the first flash conversion determines that the input voltage is between  $\frac{3}{8}$  V<sub>REF</sub> and  $\frac{4}{8}$  V<sub>REF</sub> - LSB/2, the Voltage Estimator's output code will be corrected by subtracting "1". This results in a corrected value of "01". If the first flash conversion determines that the input voltage is between  $\frac{8}{16}$  V<sub>REF</sub> - LSB/2 and  $\frac{5}{8}$  V<sub>REF</sub>, the Voltage Estimator's output code remains unchanged.

After correction, the 2-bit data from both the Voltage Estimator and the first flash conversion are decoded to produce the five MSBs. Decoding is similar to that of a 5-bit flash converter since there are 32 tap points on the MSB Ladder. However, 31 comparators are not needed since the Voltage Estimator places the eight comparators along the MSB Ladder where reference tap voltages are present that fall above and below the magnitude of  $V_{IN}$ . Comparators are not needed outside this selected range. If a comparator's output is a "0", all comparators above it will also have outputs of "0" and if a comparator's output is a "1", all comparators below it will also have outputs of "1".

### DIGITAL INTERFACE

The ADC08061/2 has two basic interface modes which are selected by connecting the **MODE** pin to a logic high or low.

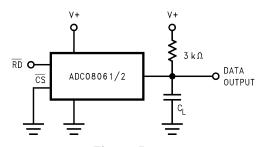

### **RD** Mode

With a logic low applied to the **MODE** <u>pin</u>, the converter is set to **Read** mode. In this configuration (see Figure 7), a complete version is done by pulling RD low, and holding low, until the conversion is complete and output data appears. This typically takes 655 ns. The INT (interrupt) line goes low at the end of conversion. A typical delay of 50 ns is needed between the rising edge of RD (after the end of a conversion) and the start of the next conversion (by pulling RD low). The RDY output goes low after the falling edge of CS and goes high at the end-of-conversion. It can be used to signal a processor that the converter is busy or serve as a system Transfer Acknowledge signal. For the ADC08062 the data generated by the first conversion cycle after power-up is from an unknown channel.

### **RD** Mode Pipelined Operation

Applications that require shorter RD pulse widths than those used in the **Read** mode as described above can be achieved by setting RD's width between 200 ns–400 ns (Figure 11). RD pulse widths outside this range will create conversion linearity errors. These errors are caused by exercising internal interface logic circuitry using CS and/or RD during a conversion.

When  $\overline{RD}$  goes low, a conversion is initiated and the data from the previous conversion is available on the DB0–DB7 outputs. Reading D0–D7 for the first two times after power-up produces random data. The data will be valid during the third  $\overline{RD}$  pulse that occurs after the first conversion.

#### www.ti.com

### WR-RD (WR then RD) Mode

The <u>AD</u>C08061/2 is in the **WR-RD** mode with the **MODE** pin tied high. A conversion starts on the falling edge of the WR signal. There are two options for reading the <u>output</u> data which relate to interface timing. If an interruptdriven scheme is desired, the user can wait for the INT output to go low before reading the conversion result (see Figure 9). Typically, INT will go low 520 ns, maximum, after WR 's rising edge. However, if a shorter conversion time is desired, the processor need not wait for INT and can exercise a read after only 350 ns (see Figure 8). If RD is pulled low before INT goes low, INT will immediately go low and data will appear at the outputs. This is the fastest operating mode ( $t_{RD} \le t_{INTL}$ ) with a conversion time, including data access time, of 560 ns. Allowing 100 ns for reading the conversion data and the delay between conversions gives a total throughput time of 660 ns (throughput rate of 1.5 MHz).

# WR-RD Mode with Reduced Interface System Connection

$\overline{CS}$  and  $\overline{RD}$  can be tied low, using only  $\overline{WR}$  to control the start of conversion for applications that require reduced digital interface while operating in the  $\overline{WR}$ - $\overline{RD}$  mode (Figure 10). Data will be valid approximately 705 ns following WR 's rising edge.

### Multiplexer Addressing

The ADC08062 has 2 multiplexer inputs. These are selected using the A0 multiplexer channel selection input. Table 1 shows the input code needed to select a given channel. The multiplexer address is latched when received but the multiplexer channel is updated after the completion of the current conversion.

|          | -                |

|----------|------------------|

| ADC08062 | Channel          |

| A0       |                  |

| 0        | V <sub>IN1</sub> |

| 1        | V <sub>IN2</sub> |

Table 1. Multiplexer Addressing

The multiplexer address data must be valid at the time of RD's falling edge, remain valid during the conversion, and can go high after RD goes high when operating in the **Read Mode**.

The multiplexer address data should be valid at or before the time of  $\overline{WR}$ 's falling edge, remain valid while  $\overline{WR}$  is low, and go invalid after  $\overline{WR}$  goes high when operating in the  $\overline{WR}$ -RD Mode.

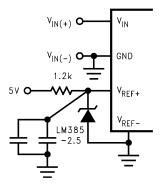

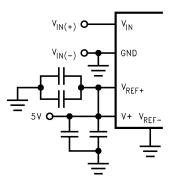

### **REFERENCE INPUTS**

The two V<sub>REF</sub> inputs of the ADC08061/2 are fully differential and define the zero to full-scale input range of the A to D converter. This allows the designer to vary the span of the analog input since this range will be equivalent to the voltage difference between V<sub>REF+</sub> and V<sub>REF-</sub>. Transducers with minimum output voltages above GND can also be compensated by connecting V<sub>REF</sub> to a voltage that is equal to this minimum voltage. By reducing V<sub>REF</sub> (V<sub>REF</sub> = V<sub>REF+</sub> - V<sub>REF-</sub>) to less than 5V, the sensitivity of the converter can be increased (i.e., if V<sub>REF</sub> = 2.5V, then 1 LSB = 9.8 mV). The ADC08061/2's reference arrangement also facilitates ratiometric operation and in many cases the ADC08061/2's power supply can be used for transducer power as well as the V<sub>REF</sub> source. Ratiometric operation is achieved by connecting V<sub>REF-</sub> to GND and connecting V<sub>REF+</sub> and a transducer's power supply input to V<sup>+</sup>. The ADC08061/2's linearity degrades when V<sub>REF+</sub> - |V<sub>REF-</sub>| is less than 2.0V.

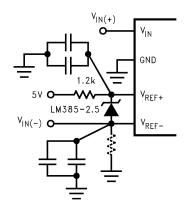

The voltage at  $V_{REF-}$  sets the input level that produces a digital output of all zeros. Though  $V_{IN}$  is not itself differential, the reference design affords nearly differential-input capability for some measurement applications. Figure 19 shows one possible differential configuration.

It should be noted that, while the two  $V_{REF}$  inputs are fully differential, the digital output will be zero for any analog input voltage if  $V_{REF-} \ge V_{REF+}$ .

www.ti.com

SNAS073D – JUNE 1999 – REVISED MARCH 2013

### ANALOG INPUT AND SOURCE IMPEDANCE

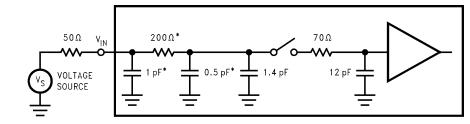

The ADC08061/2's analog input circuitry includes an analog switch with an "on" resistance of  $70\Omega$  and capacitance of 1.4 pF and 12 pF (see Figure 19). The switch is closed during the A/D's input signal acquisition time (while WR is low when using the WR -RD Mode). A small transient current flows into the input pin each time the switch closes. A transient voltage, whose magnitude can increase as the source impedance increases, may be present at the input. So long as the source impedance is less than  $500\Omega$ , the input voltage transient will not cause errors and need not be filtered.

Large source impedances can slow the charging of the sampling capacitors and degrade conversion accuracy. Therefore, only signal sources with output impedances less than  $500\Omega$  should be used if rated accuracy is to be achieved at the minimum sample time (100 ns maximum). A signal source with a high output impedance should have its output buffered with an operational amplifier. Any ringing or voltage shifts at the op amp's output during the sampling period can result in conversion errors.

Correct conversion results will be obtained for input voltages greater than GND - 100 mV and less than V<sup>+</sup> + 100 mV. Do not allow the signal source to drive the analog input pin more than 300 mV higher than V<sup>+</sup>, or more than 300 mV lower than GND. The current flowing through any analog input pin should be limited to 5 mA or less to avoid permanent damage to the IC if an analog input pin is forced beyond these voltages. The sum of all the overdrive currents into all pins must be less than 20 mA. Some sort of protection scheme should be used when the input signal is expected to extend more than 300 mV beyond the power supply limits. A simple protection network using resistors and diodes is shown in Figure 23.

### INHERENT SAMPLE-AND-HOLD

An important benefit of the ADC08061/2's input architecture is the inherent sample-and-hold (S/H) and its ability to measure relatively high speed signals without the help of an external S/H. In a non-sampling converter, regardless of its speed, the input must remain stable to at least ½ LSB throughout the conversion process if full accuracy is to be maintained. Consequently, for many high speed signals, this signal must be externally sampled and held stationary during the conversion.

The ADC08<u>061</u> and ADC08<u>062</u> are suitable for DSP-based systems because of the direct control of the S/H through the WR signal. The WR input signal allows the A/D to be synchronized to a DSP system's sampling rate or to other ADC08061 and ADC08062s.

\*Represents a multiplexer channel in the ADC08062.

### Figure 19. ADC08061 and ADC08062 Equivalent Input Circuit Model

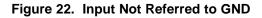

Note : Bypass capacitors consist of a 0.1  $\mu F$  ceramic in parallel with a 10  $\mu F$  bead tantalum.

# Figure 20. External Reference 2.5V Full-Scale (Standard Application)

Figure 21. Power Supply as Reference

\* Signal source driving  $V_{IN}(-)$  must be capable of sinking 5 mA.

TEXAS INSTRUMENTS

SNAS073D – JUNE 1999 – REVISED MARCH 2013

www.ti.com

Note the multiple bypass capacitors on the reference and power supply pins.  $V_{REF-}$  should be bypass to analog ground using multiple capacitors if it is not grounded (see LAYOUT, GROUNDS, AND BYPASSING).  $V_{IN1}$  is shown with an optional input protection network.

#### Figure 23. Typical Connection

The ADC08061 can perform accurate conversions of full-scale input signals at frequencies from DC to more than 300 kHz (full power bandwidth) without the need of an external sample-and-hold (S/H).

### LAYOUT, GROUNDS, AND BYPASSING

In order to ensure fast, accurate conversions from the ADC08061/2, it is necessary to use appropriate circuit board layout techniques. Ideally, the analog-to-digital converter's ground reference should be low impedance and free of noise from other parts of the system. Digital circuits can produce a great deal of noise on their ground returns and, therefore, should have their own separate ground lines. Best performance is obtained using separate ground planes for the digital and analog parts of the system.

The analog inputs should be isolated from noisy signal traces to avoid having spurious signals couple to the input. Any external component (e.g., an input filter capacitor) connected across the inputs should be returned to a very clean ground point. Incorrectly grounding the ADC08061/2 will result in reduced conversion accuracy.

The V<sup>+</sup> supply pin, V<sub>REF+</sub>, and V<sub>REF-</sub> (if not grounded) should be bypassed with a parallel combination of a 0.1  $\mu$ F ceramic capacitor and a 10  $\mu$ F tantalum capacitor placed as close as possible to the supply pin using short circuit board traces. See Figure 22 and Figure 23.

Copyright © 1999–2013, Texas Instruments Incorporated

SNAS073D - JUNE 1999-REVISED MARCH 2013

### **REVISION HISTORY**

| Changes from Revision C (March 2013) to Revision D |                                                    |      |

|----------------------------------------------------|----------------------------------------------------|------|

| •                                                  | Changed layout of National Data Sheet to TI format | . 18 |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated