**CDCE6214**

SNAS811 - JULY 2020

# CDCE6214 Ultra-Low Power Clock Generator With One PLL, Four Differential Outputs, Two Inputs, and Internal EEPROM

### **Features**

- Configurable high performance, low-power, frac-N PLL with RMS jitter with spurs (12 kHz - 20 MHz,  $F_{out} > 100 \text{ MHz}) \text{ as:}$

- Integer mode:

- Differential output: 350 fs typical, 600 fs maximum

- LVCMOS output: 1.05 ps typical, 1.5 ps maximum

- Fractional mode:

- Differential output: 1.7 ps typical, 2.1 ps maximum

- LVCMOS output: 2.0 ps typical, 4.0 ps maximum

- Supports PCIe Gen1/2/3/4 with SSC and Gen 1/2/3/4/5 without SSC

- 2.335-GHz to 2.625-GHz internal VCO

- Typical power consumption: 65 mA for 4-output channel, 23 mA for 1-output channel.

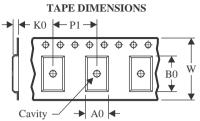

- Universal clock input, two reference inputs for redundancy

- Differential AC-coupled or LVCMOS: 10 MHz to 200 MHz

- Crystal: 10 MHz to 50 MHz

- Flexible output clock distribution

- 4 channel dividers: Up to 5 unique output frequencies from 24 kHz to 328.125 MHz

- Combination of LVDS-like, LP-HCSL or LVCMOS outputs on OUT0 - OUT4 pins

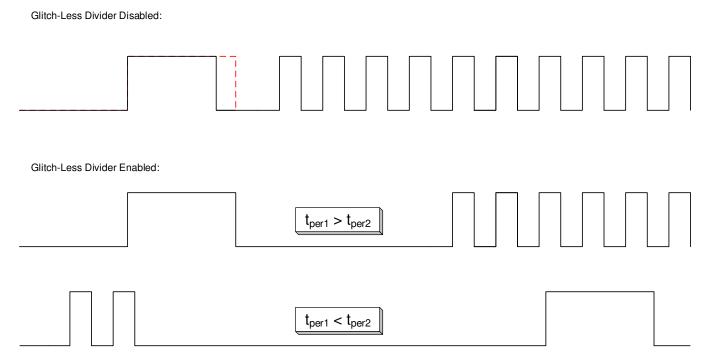

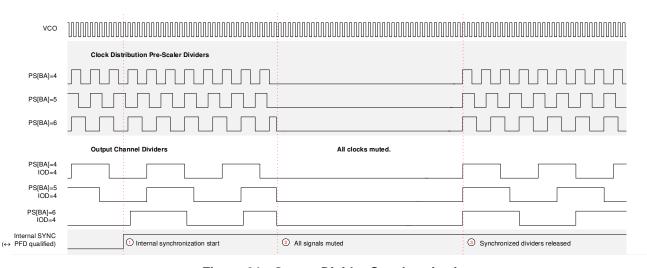

- Glitchless output divider switching and output channel synchronization

- Individual output enable through GPIO and register

- Frequency margining options

- DCO mode: frequency increment/decrement with 10ppb or less step-size

- Fully-integrated, configurable loop bandwidth: 100 kHz to 1.6 MHz

- Single or mixed supply for level translation: 1.8 V/2.5 V/3.3 V

- Configurable GPIOs and flexible configuration options

- I<sup>2</sup>C-compatible interface: up to 400 kHz

- Integrated EEPROM with two pages and external select pin. In-situ programming allowed.

- Supports  $100-\Omega$  systems

- Low electromagnetic emissions

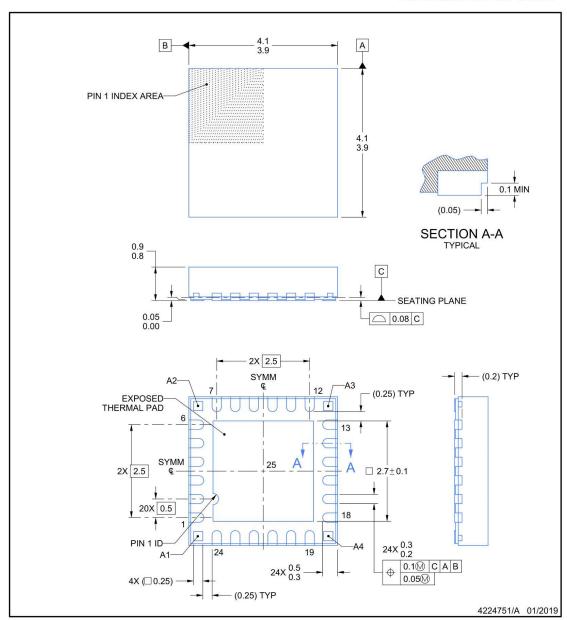

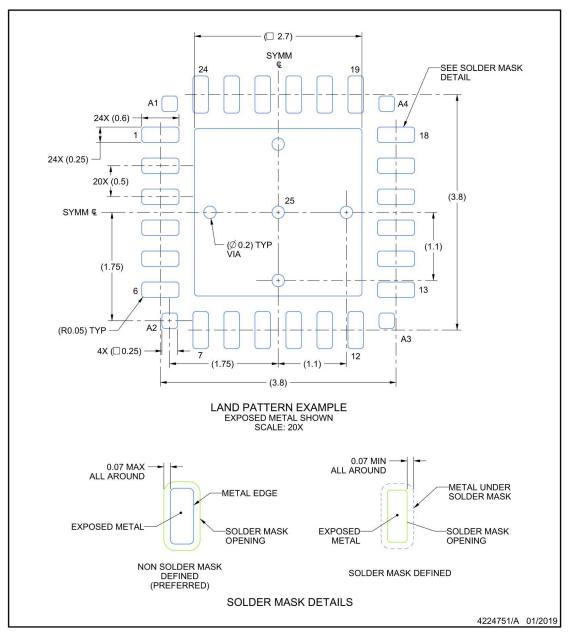

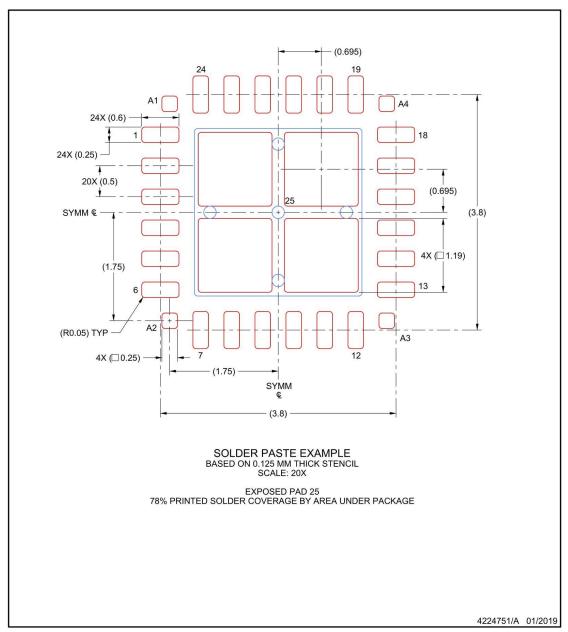

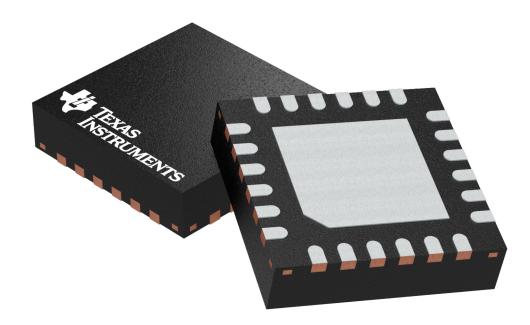

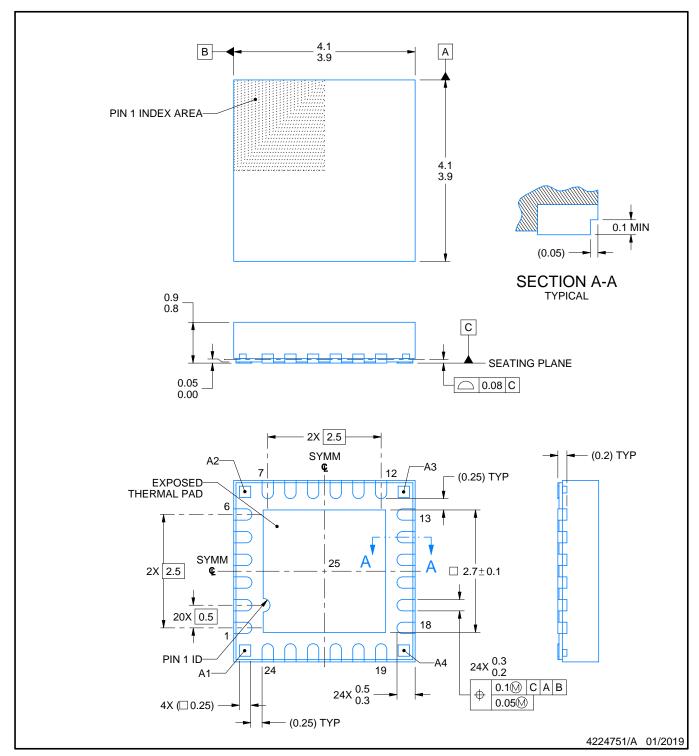

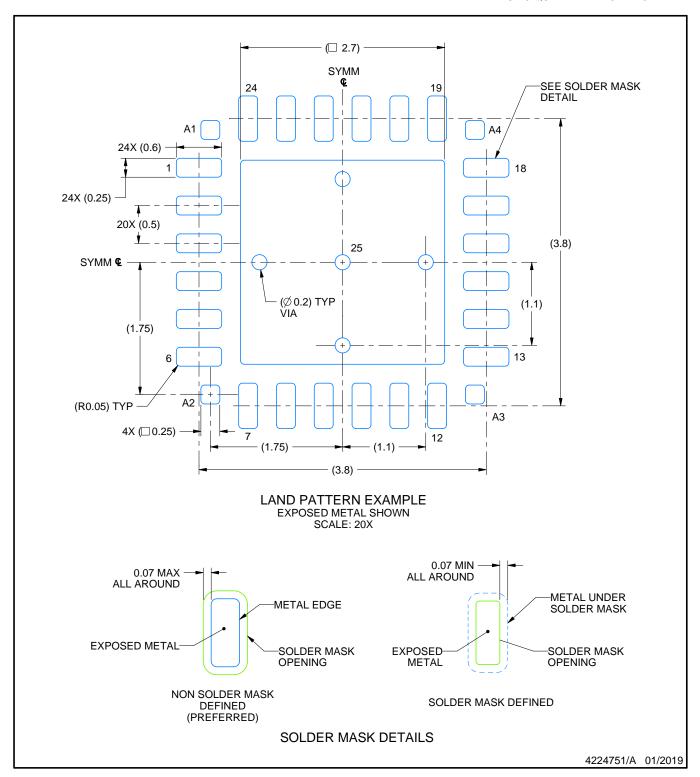

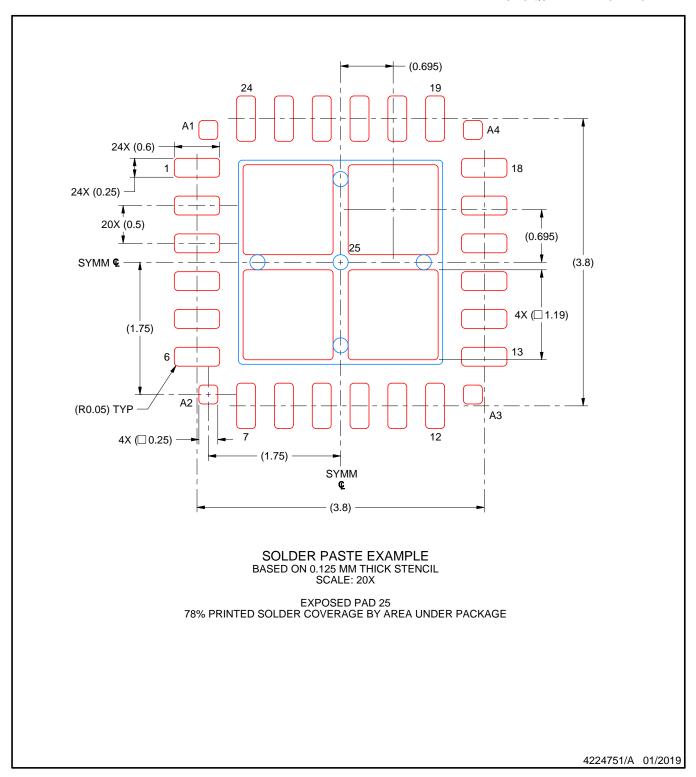

- Small footprint: 24-pin VQFN (4 mm × 4 mm)

# 2 Applications

- PCIe Gen 1 Gen 5 clocking

- Data Center & Enterprise Computing, PC & Notebook

- Enterprise Machine Multi-Function Printer

- Test & Measurement, Handheld Equipment

# 3 Description

The CDCE6214 is a four-channel, ultra-low power, medium grade jitter, clock generator that can generate five independent clock outputs selectable between various modes of drivers. The input source could be a single-ended or differential input clock source, or a crystal. The CDCE6214 features a frac-N PLL to synthesize unrelated base frequency from any input frequency. The CDCE6214 can be configured through the I<sup>2</sup>C interface. In the absence of the serial interface, the GPIO pins can be used in Pin Mode to configure the product into distinctive configurations.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| CDCE6214    | VQFN (24) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

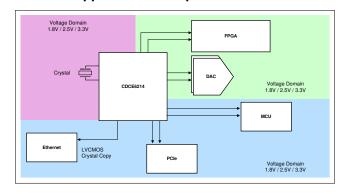

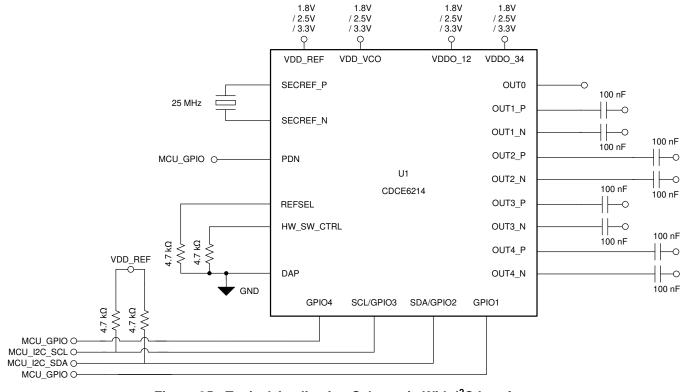

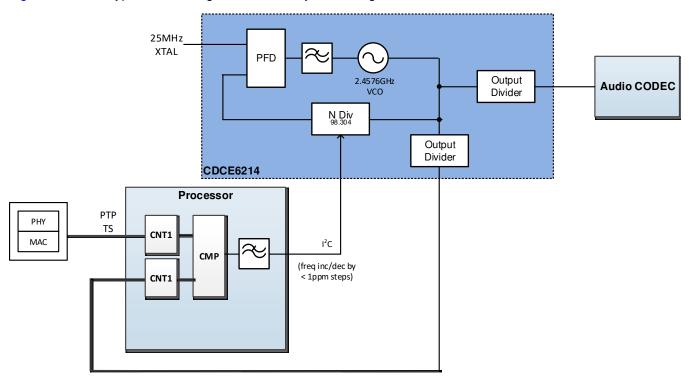

#### **Application Example CDCE6214**

# **Table of Contents**

| 1 | Features 1                                                             |    | 7.25 Typical Characteristics                      | 12     |

|---|------------------------------------------------------------------------|----|---------------------------------------------------|--------|

| 2 | Applications 1                                                         | 8  | Parameter Measurement Information                 | 14     |

| 3 | Description 1                                                          |    | 8.1 Reference Inputs                              | 14     |

| 4 | Revision History2                                                      |    | 8.2 Outputs                                       | 14     |

| 5 | Description (cont.)                                                    |    | 8.3 Serial Interface                              | 15     |

| 6 | Pin Configuration and Functions                                        |    | 8.4 PSNR Test                                     | 15     |

| 7 | Specifications5                                                        |    | 8.5 Clock Interfacing and Termination             | 16     |

| • | 7.1 Absolute Maximum Ratings                                           | 9  | Detailed Description                              | 18     |

|   | 7.2 ESD Ratings                                                        |    | 9.1 Overview                                      | 18     |

|   | 7.3 Recommended Operating Conditions                                   |    | 9.2 Functional Block Diagram                      | 18     |

|   | 7.4 Thermal Information                                                |    | 9.3 Feature Description                           | 18     |

|   | 7.5 EEPROM Characteristics 6                                           |    | 9.4 Device Functional Modes                       | 30     |

|   | 7.6 Reference Input, Single-Ended Characteristics 6                    |    | 9.5 Programming                                   | 30     |

|   | 7.7 Reference Input, Differential Characteristics 6                    | 10 | Application and Implementation                    | 38     |

|   | 7.8 Reference Input, Crystal Mode Characteristics 6                    |    | 10.1 Application Information                      | 38     |

|   | 7.9 General-Purpose Input Characteristics                              |    | 10.2 Typical Application                          | 39     |

|   | 7.10 Triple Level Input Characteristics                                | 11 | Power Supply Recommendations                      | 40     |

|   | 7.11 Logic Output Characteristics                                      |    | 11.1 Power-Up Sequence                            | 40     |

|   | 7.12 Phase Locked Loop Characteristics                                 |    | 11.2 Decoupling                                   | 40     |

|   | 7.13 Closed-Loop Output Jitter Characteristics                         | 12 | Layout                                            | 41     |

|   | 7.14 Input and Output Isolation                                        |    | 12.1 Layout Guidelines                            | 41     |

|   | 7.15 Buffer Mode Characteristics                                       |    | 12.2 Layout Examples                              | 41     |

|   | 7.16 PCIe Spread Spectrum Generator 8                                  | 13 | Device and Documentation Support                  | 43     |

|   | 7.17 LVCMOS Output Characteristics                                     |    | 13.1 Device Support                               |        |

|   | 7.18 LP-HCSL Output Characteristics9                                   |    | 13.2 Receiving Notification of Documentation Upda | tes 43 |

|   | 7.19 LVDS Output Characteristics                                       |    | 13.3 Support Resources                            |        |

|   | 7.20 Output Synchronization Characteristics 10                         |    | 13.4 Trademarks                                   | 43     |

|   | 7.21 Power-On Reset Characteristics                                    |    | 13.5 Electrostatic Discharge Caution              | 43     |

|   | 7.22 I <sup>2</sup> C-Compatible Serial Interface Characteristics 10   |    | 13.6 Glossary                                     | 43     |

|   | 7.23 Timing Requirements, I <sup>2</sup> C-Compatible Serial Interface | 14 | Mechanical, Packaging, and Orderable Information  | 43     |

|   | 7.24 Power Supply Characteristics                                      |    |                                                   |        |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| July 2020 | *        | Initial release. |

Submit Documentation Feedback

www.ti.com SNAS811 – JULY 2020

# 5 Description (cont.)

On-chip EEPROM can be used to change the configuration, which is pre-selectable through the pins. The device provides frequency margining options with glitch-free operation to support system design verification tests (DVT) and Ethernet Audio-Video Bridging (eAVB). Fine frequency margining is available on any output channel by steering the fractional feedback divider in DCO mode.

Internal power conditioning provides excellent power supply ripple rejection (PSRR), reducing the cost and complexity of the power delivery network. The analog and digital core blocks operate from either a 1.8-V, 2.5-V, or 3.3-V ±5% supply, and output blocks operate from a 1.8-V, 2.5-V, or 3.3-V ±5% supply.

The CDCE6214 enables high-performance clock trees from a single reference at ultra-low power with a small footprint. The factory- and user-programmable EEPROM features make the CDCE6214 an easy-to-use, instant-on clocking device with a low power consumption.

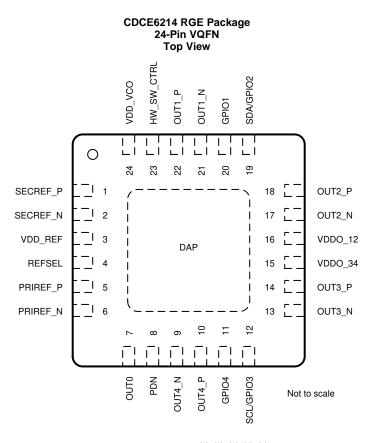

# 6 Pin Configuration and Functions

Pin Functions (1) (2) (3) (4) (5)

| PIN NAME NO.                    |    | 1/0 | DESCRIPTION                                                                                                                                                                                              |

|---------------------------------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |    | I/O | DESCRIPTION                                                                                                                                                                                              |

| POWER                           |    |     |                                                                                                                                                                                                          |

| DAP                             | _  | G   | Die Attach Pad. The DAP is an electrical connection and provides a thermal dissipation path. For proper electrical and thermal performance of the device, the DAP must be connected to PCB ground plane. |

| VDD_REF 3 P 1.8 V/2.5 V/3.3 V F |    | Р   | 1.8 V/2.5 V/3.3 V Power Supply for Reference Input and Digital.                                                                                                                                          |

| VDD_VCO                         | 24 | Р   | 1.8 V/2.5 V/3.3 V Power Supply for PLL/VCO.                                                                                                                                                              |

- (1) G = Ground, P = Power

- (2) I = Input, I/O = Input/Output, O = Output

- (3) I, R<sub>PUPD</sub> = Input with Resistive Pull-up and Pull-down

- 4) I, R<sub>PU</sub> = Input with Resistive Pull=up

- (5) I/O, R<sub>PU</sub> = Input/Output with resistive pull-up

Copyright © 2020, Texas Instruments Incorporated

# Pin Functions (1) (2) (3) (4) (5) (continued)

| PI             | N            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------|--------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NO.          | 1/0                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VDDO_12        | 16           | Р                    | 1.8 V/2.5 V/3.3 V Power Supply for OUT1 and OUT2 channels                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| VDDO_34        | 15           | Р                    | 1.8 V/2.5 V/3.3 V Power Supply for OUT0, OUT3, and OUT4 channels                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| INPUT BLOCK    | •            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| HW_SW_CT<br>RL | 23           | I, R <sub>PUPD</sub> | Manual selection pin for EEPROM pages (3-state). Weak Pullup/Pulldown. R <sub>PU</sub> = 50 k $\Omega$ . R <sub>PD</sub> = 50 k $\Omega$ .                                                                                                                                                                                                                                                                                                 |  |  |

| PRIREF_P       | 5            | I                    | Primary reference clock. Accepts a differential or single-ended input. Input pins need AC-                                                                                                                                                                                                                                                                                                                                                 |  |  |

| PRIREF_N       | 6            | 1                    | coupling capacitors and internally biased in differential mode. For LVCMOS, input should be provided on PRIREF_P and the non-driven input pin should be pulled down to ground. Internal biasing for differential mode is disabled in single-ended mode.                                                                                                                                                                                    |  |  |

| REFSEL         | 4            | I, R <sub>PUPD</sub> | Manual selection pin of reference input (3-state). Weak Pullup/Pulldown. R <sub>PU</sub> = 50 k $\Omega$ . R <sub>PD</sub> = 50 k $\Omega$ .                                                                                                                                                                                                                                                                                               |  |  |

| SECREF_P       | 1            | I                    | Secondary reference clock. Accepts a differential or single-ended input or XTAL. Input pins                                                                                                                                                                                                                                                                                                                                                |  |  |

| SECREF_N       | 2            | I                    | need AC-coupling capacitors and internally biased in differential mode. For XTAL input, connect crystal between SECREF_P and SECREF_N pin. SECREF_P is XOUT, SECRE is XIN. This device do not need any power limiting resistor on XOUT. For LVCMOS input input should be provided on SECREF_P, and the non-driven input pin should be pulled to ground. Internal biasing for differential mode is disabled in single-ended and XTAL model. |  |  |

| OUTPUT BLOCK   |              |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OUT0           | 7            | 0                    | LVCMOS Output 0. Reference Input can be bypassed into this output. Output slew-ra configurable on all LVCMOS outputs.                                                                                                                                                                                                                                                                                                                      |  |  |

| OUT1_P         | 22           | 0                    | LVDS-like/LP-HCSL/LVCMOS Output Pair 1. Programmable driver with LVDS-like/LP-HCSL                                                                                                                                                                                                                                                                                                                                                         |  |  |

| OUT1_N         | 21           | 0                    | or 2x LVCMOS outputs.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| OUT2_P         | 18           | 0                    | LVDS-like/LP-HCSL Output Pair 2. Programmable driver with LVDS-like/LP-HCSL outputs.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| OUT2_N         | 17           | 0                    | EVD3-like/E1 -1103E Output 1 all 2. 1 Togrammable univer with EVD3-like/E1 -1103E outputs.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| OUT3_P         | 14           | 0                    | LVDS-like/LP-HCSL Output Pair 3. Programmable driver with LVDS-like/LP-HCSL outputs.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| OUT3_N         | 13           | 0                    | EVD3-like/E1 -1103E Output 1 all 3.1 Togrammable univer with EVD3-like/E1 -1103E outputs.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| OUT4_P         | 10           | 0                    | LVDS-like/LP-HCSL/LVCMOS Output Pair 4. Programmable driver with LVDS-like/LP-HCSL                                                                                                                                                                                                                                                                                                                                                         |  |  |

| OUT4_N         | 9            | 0                    | or 2x LVCMOS outputs.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| DIGITAL CON    | TROL / INTER | FACES                |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| GPIO1          | 20           | I/O, R <sub>PU</sub> | STATUS output or GPIO1 input. Weak pullup resistor when configured as Input. $R_{PU}$ = 50 $k\Omega$ . Pullup resistor disabled in output mode.                                                                                                                                                                                                                                                                                            |  |  |

| GPIO4          | 11           | I/O, R <sub>PU</sub> | STATUS output or GPIO4 input. Weak pullup resistor when configured as Input. $R_{PU}$ = 50 $k\Omega$ . Pullup resistor disabled in output mode.                                                                                                                                                                                                                                                                                            |  |  |

| PDN            | 8            | I, R <sub>PU</sub>   | Device Power-down/RESET (active low) or SYNCN. Weak pullup resistor. $R_{PU}$ = 50 k $\Omega$ . Pullup resistor disabled in output mode.                                                                                                                                                                                                                                                                                                   |  |  |

| SDA/GPIO2      | 19           | I/O                  | I <sup>2</sup> C Serial Data (bidirectional, open-drain) or GPIO2 input. Requires an external pullup resistor to VDD_REF in I <sup>2</sup> C mode. I <sup>2</sup> C slave address is initialized from on-chip EEPROM. Fail-safe Input.                                                                                                                                                                                                     |  |  |

| SCL/GPIO3      | 12           | I                    | I <sup>2</sup> C Serial Clock or GPIO3 input. Requires an external pullup resistor to VDD_REF in I <sup>2</sup> C mode. Fail-safe Input.                                                                                                                                                                                                                                                                                                   |  |  |

# 7 Specifications

www.ti.com

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                     |                      | MIN  | MAX                         | UNIT |

|-------------------------------------------------------------------------------------|----------------------|------|-----------------------------|------|

| VDD_REF, VDD_VCO, VDDO_12, VDDO_34                                                  | Supply Voltage       | -0.3 | 3.63                        | V    |

| PRIREF_P, PRIREF_N, SECREF_P, SECREF_N                                              | Input Voltage        | -0.3 | VDD_REF + 0.3               | V    |

| GPIO1, SDA/GPIO2, SCL/GPIO3, GPIO4, REFSEL, HW_SW_CTRL, PDN                         | Input Voltage        | -0.3 | VDD_REF + 0.3               | V    |

| OUT0, OUT1_P, OUT1_N, OUT2_P, OUT2_N, OUT3_P, OUT3_N, OUT4_P, OUT4_N <sup>(2)</sup> | Output Voltage       | -0.3 | VDDO_X <sup>(2)</sup> + 0.3 | V    |

| T <sub>J</sub>                                                                      | Junction Temperature |      | 125                         | °C   |

| T <sub>stg</sub>                                                                    | Storage temperature  | -65  | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) VDDO\_X refers to the output supply for a specific output channel, where X denotes the channel index.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | 2000  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 750   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                                                            | MIN  | NOM           | MAX   | UNIT |

|---------------------|------------------------------------------------------------|------|---------------|-------|------|

| VDD_VCO             | Core supply voltage                                        | 1.71 | 1.8, 2.5, 3.3 | 3.465 | V    |

| VDDO_12,<br>VDDO_34 | Output supply voltage                                      | 1.71 | 1.8, 2.5, 3.3 | 3.465 | V    |

| VDD_REF             | Reference supply voltage                                   | 1.71 | 1.8, 2.5, 3.3 | 3.465 | V    |

| T <sub>A</sub>      | Ambient temperature                                        | -40  |               | 105   | °C   |

| T <sub>J</sub>      | Junction temperature                                       | -40  |               | 125   | °C   |

| T <sub>LOCK</sub>   | Continuous lock over temperature (without VCO calibration) |      |               | 145   | °C   |

| t <sub>RAMP</sub>   | Maximum supply voltage ramp time <sup>(1)</sup>            | 0.1  |               | 30    | ms   |

<sup>(1)</sup> VDD pin should monotonically reach 95% of its final value within supply ramp time. All VDD pins were tied together for this evaluation. For non-monotonic or slower power supply ramp, it is recommended to pull-down PDN pin until VDD pins have reached 95% of its final value. PDN pin has a 50 kΩ pullup resistor. When PDN pin cannot be actively controlled, TI recommends to add a capacitor to GND on PDN pin to delay the release of reset.

### 7.4 Thermal Information

|                        |                                              | CDCE6214-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN)  | UNIT |

|                        |                                              | 24 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.5        | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 32.5        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.2        | °C/W |

| $R_{\theta JC(bot)}$   | Junction-to-case (bottom) thermal resistance | 2.0         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.4         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.2        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

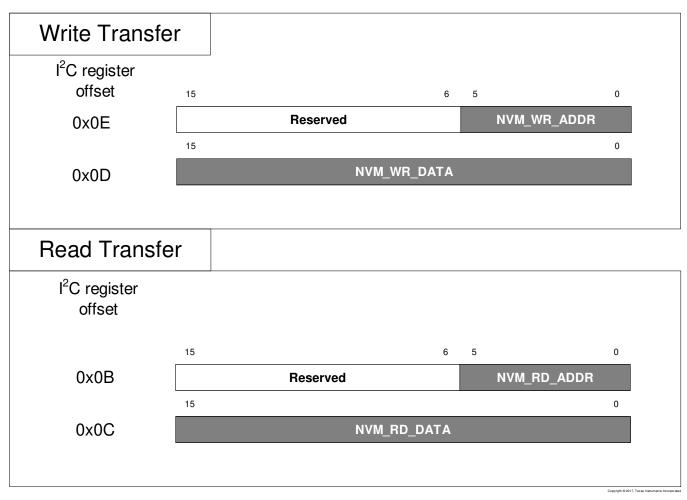

### 7.5 EEPROM Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                    | PARAMETER                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT   |

|--------------------|---------------------------|-----------------|-----|-----|-----|--------|

| n <sub>EEcyc</sub> | EEPROM programming cycles | each word       | 10  |     |     | cycles |

| t <sub>EEret</sub> | EEPROM data retention     |                 | 10  |     |     | years  |

## 7.6 Reference Input, Single-Ended Characteristics

VDD VCO, VDDO 12, VDDO 34, VDD REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub> $\Delta$ </sub> = -40°C to 105°C

|                         | PARAMETER             | TEST CONDITIONS     | MIN              | TYP MAX          | UNIT |

|-------------------------|-----------------------|---------------------|------------------|------------------|------|

| f <sub>IN_Ref</sub>     | Reference frequency   |                     | 10               | 200              | MHz  |

| $V_{IH}$                | Input high voltage    | LVCMOS Input Buffer | 0.8 ×<br>VDD_REF |                  | V    |

| V <sub>IL</sub>         | Input low voltage     | LVCMOS Input Buffer |                  | 0.2 ×<br>VDD_REF | V    |

| dV <sub>IN</sub> /dT    | Input slew rate       | 20% - 80%           | 1                |                  | V/ns |

| IDC                     | Input duty cycle      |                     | 40               | 60               | %    |

| I <sub>IN_LEAKAGE</sub> | Input leakage current |                     | -100             | 100              | μA   |

| C <sub>IN_REF</sub>     | Input capacitance     | at 25°C             |                  | 5                | pF   |

# 7.7 Reference Input, Differential Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and  $T_{\Delta}$  = -40°C to 105°C

|                         | ,                                                  | = 0,0, =.0 . = 0,0, 0.0 | = 0 / 0 Gill Gill I A |     | ~ ~ |      |

|-------------------------|----------------------------------------------------|-------------------------|-----------------------|-----|-----|------|

|                         | PARAMETER                                          | TEST CONDITIONS         | MIN                   | TYP | MAX | UNIT |

| f <sub>IN_Ref</sub>     | Reference frequency                                |                         | 10                    |     | 200 | MHz  |

| $V_{\text{IN\_DIFF}}$   | Differential input voltage swing, peak-to-<br>peak | VDD_REF = 2.5 V/3.3 V   | 0.4                   |     | 1.6 | V    |

| V <sub>IN_DIFF</sub>    | Differential input voltage swing, peak-to-<br>peak | VDD_REF = 1.8 V         | 0.4                   |     | 1.0 | V    |

| dV <sub>IN</sub> /dT    | Input slew rate                                    | 20% - 80%               | 1                     |     |     | V/ns |

| IDC                     | Input duty cycle                                   |                         | 40                    |     | 60  | %    |

| I <sub>IN_LEAKAGE</sub> | Input leakage current                              |                         | -100                  |     | 100 | μA   |

| C <sub>IN_REF</sub>     | Input capacitance                                  | at 25°C                 |                       | 5   |     | pF   |

### 7.8 Reference Input, Crystal Mode Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C<sup>(1)</sup>

|                       | PARAMETER                            | TEST CONDITIONS                                               | MIN | TYP MAX | UNIT |

|-----------------------|--------------------------------------|---------------------------------------------------------------|-----|---------|------|

| f <sub>IN_Xtal</sub>  | Crystal frequency                    | Fundamental mode                                              | 10  | 50      | MHz  |

| Z <sub>ESR</sub>      | Crystal equivalent series resistance | f <sub>XTAL</sub> = 10 MHz to 16 MHz                          |     | 60      | Ω    |

| Z <sub>ESR</sub>      | Crystal equivalent series resistance | f <sub>XTAL</sub> = 16 MHz to 30 MHz                          |     | 50      | Ω    |

| Z <sub>ESR</sub>      | Crystal equivalent series resistance | f <sub>XTAL</sub> = 30 MHz to 50 MHz                          |     | 30      | Ω    |

| C <sub>L</sub>        | Crystal load capacitance             | Using on-chip load capacitance. A supported Crystal is within | 5   | 12.8    | pF   |

| P <sub>XTAL</sub>     | Crystal tolerated drive power        | A supported crystal tolerates up to                           |     | 200     | μW   |

| C <sub>XIN_LOAD</sub> | On-Chip load capacitance             | Programmable in typ. 200 fF steps                             | 3   | 9.1     | pF   |

<sup>(1)</sup> For detailed application report on configuring the XTAL Input, please refer to SNAA331: CDCI6214 and CDCE6214-Q1 design with crystal input.

# 7.9 General-Purpose Input Characteristics

VDD VCO, VDDO 12, VDDO 34, VDD REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

| VBB_VBB, VBBB_12, VBBB_61, VBB_1421 = 116 V 1676, 216 V 1676, 616 V 1676 and VA = 16 G 16 G G |                          |                                           |                  |                  |      |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|------------------|------------------|------|--|--|--|

| PARAMETER                                                                                     |                          | TEST CONDITIONS                           |                  | TYP MAX          | UNIT |  |  |  |

| V <sub>IH</sub>                                                                               | Input high voltage       |                                           | 0.8 ×<br>VDD_REF |                  | V    |  |  |  |

| V <sub>IL</sub>                                                                               | Input low voltage        |                                           |                  | 0.2 ×<br>VDD_REF | ٧    |  |  |  |

| I <sub>IH</sub>                                                                               | Input high level current | V <sub>IH</sub> = VDD_REF, GPIO[1:4], PDN | -5               | 5                | μΑ   |  |  |  |

# **General-Purpose Input Characteristics (continued)**

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                         | PARAMETER                         | TEST CONDITIONS                              | MIN  | TYP | MAX | UNIT |

|-------------------------|-----------------------------------|----------------------------------------------|------|-----|-----|------|

| I <sub>IL</sub>         | Input low level current           | V <sub>IL</sub> = GND, GPIO[2:3]             | -5   |     | 5   | μA   |

| I <sub>IL</sub>         | Input low level current           | V <sub>IL</sub> = GND, GPIO[1], GPIO[4], PDN | -100 |     | 100 | μA   |

| dV <sub>IN</sub> /dT    | Input slew rate                   | 20% - 80%                                    | 0.5  |     |     | V/ns |

| T <sub>PULSE_WIDT</sub> | Pulse width for correct operation |                                              | 10   |     |     | ns   |

| R <sub>PU</sub>         | Pullup Resistance                 | Pins PDN, GPIO[1], GPIO[4]                   | 30   | 55  | 80  | kΩ   |

| C <sub>IN</sub>         | Pin Capacitance                   |                                              |      |     | 10  | pF   |

### 7.10 Triple Level Input Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

| PARAMETER       |                          | TEST CONDITIONS           | MIN               | TYP              | MAX               | UNIT |

|-----------------|--------------------------|---------------------------|-------------------|------------------|-------------------|------|

| V <sub>IH</sub> | Input high voltage       |                           | 0.8 x<br>VDD_REF  |                  |                   | V    |

| V <sub>IM</sub> | Input mid voltage        | Float pin                 | 0.41 ×<br>VDD_REF | 0.5 ×<br>VDD_REF | 0.58 x<br>VDD_REF | V    |

| V <sub>IL</sub> | Input low voltage        |                           |                   |                  | 0.2 x<br>VDD_REF  | V    |

| I <sub>IH</sub> | Input high level current | V <sub>IH</sub> = VDD_REF | 20                | 50               | 100               | μA   |

| I <sub>IL</sub> | Input low level current  | V <sub>IL</sub> = GND     | -100              | -50              | -20               | μΑ   |

## 7.11 Logic Output Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|     | PARAMETER           | TEST CONDITIONS | MIN              | TYP | MAX           | UNIT |

|-----|---------------------|-----------------|------------------|-----|---------------|------|

| VOH | Output high voltage |                 | 0.8 ×<br>VDD_REF |     |               | V    |

| VOL | Output low voltage  |                 |                  | VDD | 0.2 x<br>_REF | V    |

### 7.12 Phase Locked Loop Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                        | PARAMETER                                                      | TEST CONDITIONS                 | MIN  | TYP | MAX  | UNIT  |

|------------------------|----------------------------------------------------------------|---------------------------------|------|-----|------|-------|

| f <sub>PFD</sub>       | Phase Detector Frequency                                       | Integer and Fractional PLL mode | 1    |     | 100  | MHz   |

| f <sub>VCO</sub>       | Voltage Controlled Oscillator Frequency                        |                                 | 2335 |     | 2625 | MHz   |

| f <sub>BW</sub>        | Configurable closed-loop PLL Bandwidth                         | REF = 25 MHz                    | 100  |     | 1600 | kHz   |

| K <sub>VCO</sub>       | Voltage-Controlled Oscillator Gain                             | f <sub>VCO</sub> = 2.4 GHz      |      | 140 |      | MHz/V |

| K <sub>VCO</sub>       | Voltage-Controlled Oscillator Gain                             | f <sub>VCO</sub> = 2.5 GHz      |      | 175 |      | MHz/V |

| ΔT <sub>CL</sub>       | Allowable Temperature Drift for Continuous Lock <sup>(1)</sup> | dT/dt ≤ 20 K / min              |      |     | 145  | °C    |

| f <sub>MAX-ERROR</sub> | Maximum frequency error with frac-N PLL                        |                                 |      |     | 0.1  | ppm   |

<sup>(1)</sup> The maximum allowable temperature drift for continuous lock: how far the temperature can drift in either direction from the value it was at the time, when the On-Chip VCO was calibrated while the PLL stays in lock throughout the temperature drift. The internal VCO calibration takes place: at device start-up, when the device is reset using the RESET pin and when REGISTER bit is changed. This implies the device will work over the entire frequency range, but if the temperature drifts more than the 'maximum allowable temperature drift for continuous lock', then it is necessary to re-calibrate the VCO, using the appropriate REGISTER bit, to ensure the PLL stays in lock. Regardless of what temperature the part was initially calibrated at, the temperature can never drift outside the ambient temperature range of -40° C to 105° C.

### 7.13 Closed-Loop Output Jitter Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                    | PARAMETER        | TEST CONDITIONS                                                                                            | MIN | TYP | MAX | UNIT |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>RJ_CL</sub> | RMS Phase Jitter | RMS jitter with spurs from 12 kHz to 20 MHz , Input Crystal = 25 MHz, Differential OUTx > 100 MHz, int-PLL |     | 350 | 600 | fs   |

# INSTRUMENTS

### **Closed-Loop Output Jitter Characteristics (continued)**

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                           | PARAMETER                       | TEST CONDITIONS                                                                                                                   | MIN | TYP  | MAX  | UNIT |

|---------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| t <sub>RJ_CL</sub>        | RMS Phase Jitter <sup>(1)</sup> | RMS jitter with spurs from 12 kHz to 20 MHz, Input Crystal = 25 MHz, Differential OUTx > 100 MHz, frac-PLL                        |     | 1600 | 2100 | fs   |

| t <sub>RJ_CL</sub> , PCIE | RMS Phase Jitter                | PCIe Gen 3 Filter applied, XIN = Crystal<br>25 MHz, OUTx = 100 MHz, frac-N PLL<br>with and without SSC, LP-HCSL or LVDS<br>output |     | 475  | 1000 | fs   |

### 7.14 Input and Output Isolation

VDD VCO, VDDO 12, VDDO 34, VDD REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and  $T_{A}$  = -40°C to 105°C

|                        | PARAMETER                 | TEST CONDITIONS                                                                                     | MIN | TYP | MAX | UNIT |

|------------------------|---------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>ISOLATION</sub> | Reference input isolation | Crosstalk between reference inputs,<br>PRIREF = 27MHz LVCMOS, SECREF =<br>25MHz XTAL                |     | -64 |     | dB   |

| P <sub>ISOLATION</sub> | Reference input isolation | Crosstalk between reference inputs,<br>PRIREF = 100MHz LVDS, SECREF =<br>25MHz LVCMOS               |     | -72 |     | dB   |

| P <sub>ISOLATION</sub> | Clock output isolation    | Crosstalk between clock outputs, OUT1 = 100MHz LP-HCSL, OUT2 = 156.25MHz LVDS, PFD = 25MHz, int-PLL |     | -65 |     | dB   |

| P <sub>ISOLATION</sub> | Clock output isolation    | Crosstalk between clock outputs, OUT1 = 156.25MHz LVDS, OUT0 = 25MHz LVCMOS                         |     | -42 |     | dB   |

### 7.15 Buffer Mode Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                                     | PARAMETER                                        | TEST CONDITIONS                                                                                       | MIN  | TYP | MAX | UNIT |

|-------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| t <sub>RJ_ADD</sub>                 | Additive RMS Phase Jitter, System Level          | int. Range from 10 kHz to 20 MHz , REF = HCSL 100 MHz with 0.5 V/ns, OUTx = 100 MHz LP-HCSL           |      |     | 350 | fs   |

| t <sub>PROP</sub> ,<br>LVCMOS       | Input-to-output propagation delay                | REF = LVCMOS 25 MHz, OUTx = 25<br>MHz LVCMOS                                                          |      | 1   |     | ns   |

| t <sub>PROP</sub> ,<br>Differential | Input-to-output propagation delay <sup>(1)</sup> | REF = AC-LVDS 100 MHz, OUTx = 100 MHz. Measured on OUT0                                               |      | 2.3 |     | ns   |

| t <sub>PROP</sub> -<br>VARIATION    | Input-to-output delay variation in ZDB mode      | ZDB mode, LVCMOS input = LVCMOS<br>output = 25 MHz, PLL BW = 300 kHz to<br>900 kHz across temperature | -400 |     | 400 | ps   |

<sup>(1)</sup> OUT1/OUT4 and OUT2/OUT3 are matched pair-wise. OUT1/OUT4 has LVCMOS buffer while OUT2/OUT3 do not have LVCMOS buffer. There is an additional skew 150 ps- 250 ps between OUT1/OUT4 and OUT2/OUT3.

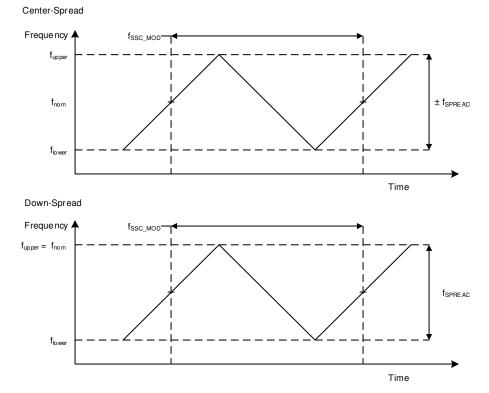

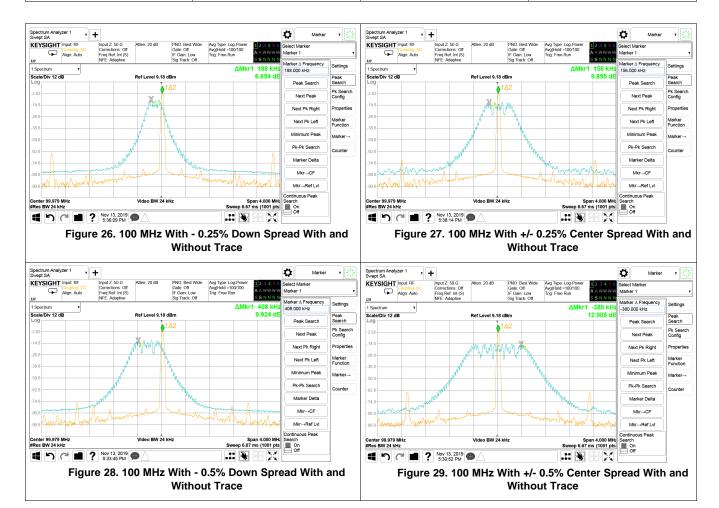

### 7.16 PCIe Spread Spectrum Generator

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                          | PARAMETER                               | TEST CONDITIONS                                            | MIN  | TYP  | MAX | UNIT |

|--------------------------|-----------------------------------------|------------------------------------------------------------|------|------|-----|------|

| f <sub>SSC-RATE</sub>    | SSC modulation rate                     | OUTx = 100 MHz                                             | 30   | 31.5 | 33  | kHz  |

| P <sub>AMPL-RED</sub>    | SSC amplitude reduction                 | OUTx = 100 MHz, -0.25% Down spread                         |      | 6.8  |     | dB   |

| P <sub>AMPL-RED</sub>    | SSC amplitude reduction                 | OUTx = 100 MHz, -0.50% Down spread                         |      | 9.9  |     | dB   |

| f <sub>SSC-STEP</sub>    | Down and Center spread SSC step size    | OUTx = 100 MHz                                             |      | 0.25 |     | %    |

| t <sub>SSC_FREQ_DE</sub> | Down spread minimum/maximum deviation   | OUTx = 100 MHz. F <sub>PFD</sub> = 25 MHz, 50 MHz, 100 MHz | -0.5 |      | 0   | %    |

| t <sub>SSC_FREQ_DE</sub> | Center spread minimum/maximum deviation | OUTx = 100 MHz. F <sub>PFD</sub> = 25 MHz, 50 MHz, 100 MHz | -0.5 |      | 0.5 | %    |

www.ti.com

# 7.17 LVCMOS Output Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                        | PARAMETER                            | TEST CONDITIONS                                                 | MIN             | TYP   | MAX             | UNIT |

|------------------------|--------------------------------------|-----------------------------------------------------------------|-----------------|-------|-----------------|------|

| f <sub>O_LVCMOS</sub>  | Output frequency                     | 2 pF to GND, normal mode                                        | 0.024           |       | 200             | MHz  |

| V <sub>OH_LVCMOS</sub> | Output high voltage                  | I <sub>OH</sub> = 1 mA, VDDO_x is corresponding supply voltage. | 0.8 ×<br>VDDO_x |       |                 | V    |

| V <sub>OL_LVCMOS</sub> | Output low voltage                   | I <sub>OL</sub> = 1 mA, VDDO_x is corresponding supply voltage. |                 |       | 0.2 x<br>VDDO_x | V    |

| I <sub>OH</sub>        | Output high current                  | Vout = 0.8 × VDDO_x, VDDO_x = 1.8 V                             |                 | -6    |                 | mA   |

| I <sub>OH</sub>        | Output high current                  | Vout = 0.8 × VDDO_x, VDDO_x = 2.5 V                             |                 | -8.5  |                 | mA   |

| I <sub>OH</sub>        | Output high current                  | Vout = 0.8 × VDDO_x, VDDO_x = 3.3 V                             |                 | -11.2 |                 | mA   |

| I <sub>OL</sub>        | Output low current                   | Vout = 0.2 × VDDO_x, VDDO_x = 1.8 V                             |                 | 6     |                 | mA   |

| I <sub>OL</sub>        | Output low current                   | Vout = 0.2 × VDDO_x, VDDO_x = 2.5 V                             |                 | 8.5   |                 | mA   |

| I <sub>OL</sub>        | Output low current                   | Vout = 0.2 × VDDO_x, VDDO_x = 3.3 V                             |                 | 11.2  |                 | mA   |

| T <sub>RISE-FALL</sub> | Output rise/fall time                | 20/80%, C <sub>L</sub> = 5 pF, normal mode                      | 300             | 500   | 700             | ps   |

| T <sub>RISE-FALL</sub> | Output rise/fall time                | 20/80%, $C_L$ = 5 pF, slow mode, measured on OUT0               |                 | 1000  |                 | ps   |

| T <sub>SKEW</sub>      | Output-to-output skew <sup>(1)</sup> | LVCMOS-to-LVCMOS outputs, same divide value                     |                 | 100   |                 | ps   |

| T <sub>SKEW</sub>      | Output-to-output skew <sup>(1)</sup> | LVCMOS-to-Differential outputs, same divide value               |                 | 400   |                 | ps   |

| ODC                    | Output duty cycle                    | Not in PLL bypass mode                                          | 45              |       | 55              | %    |

| R <sub>ON_LVCMOS</sub> | Output impedance                     | Normal mode                                                     | 45              | 60    | 75              | Ω    |

| R <sub>ON_LVCMOS</sub> | Output impedance                     | Slow mode                                                       | 50              | 65    | 85              | Ω    |

<sup>(1)</sup> OUT1/OUT4 and OUT2/OUT3 are matched pair-wise. OUT1/OUT4 has LVCMOS buffer while OUT2/OUT3 do not have LVCMOS buffer. OUT1/OUT4 is matched within T<sub>OUT-SKEW</sub>. OUT2/OUT3 is matched within T<sub>OUT-SKEW</sub>.

## 7.18 LP-HCSL Output Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                       | PARAMETER                                    | TEST CONDITIONS                                                                             | MIN   | TYP | MAX     | UNIT |

|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------|-------|-----|---------|------|

| f <sub>O_HCSL</sub>   | Output frequency                             |                                                                                             | 0.024 |     | 328.125 | MHz  |

| V <sub>OH</sub>       | Output high voltage <sup>(1)</sup>           |                                                                                             | 660   |     | 850     | mV   |

| V <sub>OL</sub>       | Output low voltage                           |                                                                                             | -150  |     | 150     | mV   |

| Z <sub>DIFF</sub>     | Differential Output Impedance <sup>(1)</sup> |                                                                                             | 90    | 100 | 110     | Ω    |

| V <sub>CROSS</sub>    | Absolute crossing point                      | 12-in, 100 $\Omega$ ±10% diff. trace with 2 pF±5%/pin in FR4.                               | 250   |     | 550     | mV   |

| $\Delta V_{CROSS}$    | Relative crossing point variation            | with respect to average crossing point                                                      |       |     | 140     | mV   |

| dV/dt                 | Slew rate for rising and falling edge        | differential, at V <sub>CROSS</sub> +/-150 mV, f <sub>O_HCSL</sub> =100 MHz <sup>(2)</sup>  | 1     |     | 4       | V/ns |

| ΔdV/dt                | Slew rate matching                           | single-ended, at V <sub>CROSS</sub> +/-75 mV, f <sub>O_HCSL</sub> =100 MHz <sup>(2)</sup>   |       |     | 20      | %    |

| Vrb                   | Output ringback voltage                      | Measured on differential output at 100 MHz and specifies minimum voltage from zero crossing | -100  |     | 100     | mV   |

| Tstable               | Time elapsed until ringback                  | Minimum time until ringback is allowed                                                      | 500   |     |         | ps   |

| ODC                   | Output duty cycle                            | Not in PLL bypass mode                                                                      | 45    |     | 55      | %    |

| T <sub>OUT-SKEW</sub> | Output skew <sup>(3)</sup>                   | Same divide value, LP-HCSL to LP-HCSL                                                       |       | 100 |         | ps   |

<sup>(1)</sup> Differential Output characteristic is trimmed in factory and trim settings are stored in EEPROM. Parameter not valid in Fall-back mode.

<sup>(2)</sup> PCIe test load slew rate

<sup>(3)</sup> OUT1/OUT4 and OUT2/OUT3 are matched pair-wise. OUT1/OUT4 has LVCMOS buffer while OUT2/OUT3 do not have LVCMOS buffer. OUT1/OUT4 is matched within T<sub>OUT-SKEW</sub>. OUT2/OUT3 is matched within T<sub>OUT-SKEW</sub>. There is an additional skew 150 ps- 250 ps between OUT1/OUT4 and OUT2/OUT3.

# 7.19 LVDS Output Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                       | PARAMETER                                  | TEST CONDITIONS                                            | MIN   | TYP  | MAX     | UNIT |

|-----------------------|--------------------------------------------|------------------------------------------------------------|-------|------|---------|------|

| f <sub>O_PRG_AC</sub> | Output frequency                           |                                                            | 0.024 |      | 328.125 | MHz  |

| V <sub>CM</sub>       | Output common mode <sup>(1)</sup>          | VDDO_X = 2.5 V, 3.3 V                                      | 1.025 | 1.2  | 1.375   | V    |

| $V_{CM}$              | Output common mode <sup>(1)</sup>          | VDDO_X = 1.8 V                                             | 0.85  | 0.95 | 1.05    | V    |

| V <sub>OD</sub>       | Differential output voltage <sup>(1)</sup> | VDDO_X = 1.8 V (F <sub>out</sub> < 200 MHz), 2.5 V, 3.3 V. | 0.25  | 0.30 | 0.45    | V    |

| V <sub>OD</sub>       | Differential output voltage <sup>(1)</sup> | VDDO_X = 1.8 V & F <sub>out</sub> > 200 MHz                | 0.22  | 0.30 | 0.45    | V    |

| t <sub>RF</sub>       | Output rise/fall times                     | LVDS (20% to 80%)                                          | 450   | 650  | 900     | ps   |

| ODC                   | Output duty cycle                          | Not in PLL bypass mode                                     | 45    |      | 55      | %    |

| T <sub>OUT-SKEW</sub> | Output skew <sup>(2)</sup>                 | Same divide value, LVDS to LVDS output                     |       | 100  |         | ps   |

- (1) Output Common Mode voltage and Differential output swing is dependent upon register settings DIFFBUF\_IBIAS\_TRIM, LVDS\_CMTRIM\_DEC and LVDS\_CMTRIM\_INC. Parameters defined for DIFFBUF\_IBIAS\_TRIM=6h, LVDS\_CMTRIM\_DEC=0h and LVDS\_CMTRIM\_INC=0h. Output Common Mode tested at DC.

- (2) OUT1/OUT4 and OUT2/OUT3 are matched pair-wise. OUT1/OUT4 has LVCMOS buffer while OUT2/OUT3 do not have LVCMOS buffer. OUT1/OUT4 is matched within T<sub>OUT-SKEW</sub>. OUT2/OUT3 is matched within T<sub>OUT-SKEW</sub>. There is an additional skew 150 ps- 250 ps between OUT1/OUT4 and OUT2/OUT3.

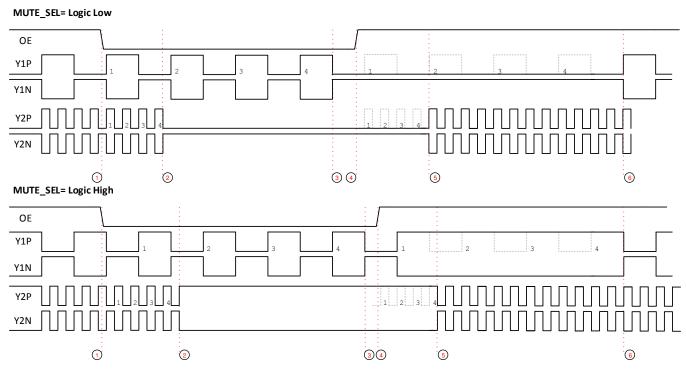

### 7.20 Output Synchronization Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and  $T_A = -40$ °C to 105°C

|                       | PARAMETER                                    | TEST CONDITIONS                                                     | MIN TYP MAX |  | MAX | UNIT |

|-----------------------|----------------------------------------------|---------------------------------------------------------------------|-------------|--|-----|------|

| t <sub>SU_SYNC</sub>  | Setup time SYNC pulse                        | with respect to PLL reference rising edge at 100 MHz with R=1       | 3           |  |     | ns   |

| t <sub>H_SYNC</sub>   | Hold time SYNC pulse                         | with respect to PLL reference rising edge at 100 MHz with R=1       |             |  | 3   | ns   |

| t <sub>PWH_SYNC</sub> | High pulse width for SYNC                    | With R = 1, at least 2 PFD periods + 24 feedback pre-scaler periods | 60          |  |     | ns   |

| t <sub>PWL_SYNC</sub> | Low pulse width for SYNC                     | With R = 1, at least 1 PFD period                                   | 6           |  |     | ns   |

| t <sub>EN</sub>       | Individual output enable time <sup>(1)</sup> | tri-state to first valid rising edge                                |             |  | 4   | nCK  |

| t <sub>DIS</sub>      | Individual output disable time (1)           | last valid falling edge to tri-state                                |             |  | 4   | nCK  |

<sup>(1)</sup> Output clock cycles of respective output channel. Global output enable handled by digital logic, additional propagation will be added.

### 7.21 Power-On Reset Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and  $T_{\Delta}$  = -40°C to 105°C

| _                      | , = , = , =                          |                                                                                                                                 |       |     |       |      |

|------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                        | PARAMETER                            | TEST CONDITIONS                                                                                                                 | MIN   | TYP | MAX   | UNIT |

| V <sub>THRESHOLD</sub> | POR threshold voltage <sup>(1)</sup> |                                                                                                                                 | 0.875 |     | 1.275 | V    |

| t <sub>STARTUP</sub>   | Start-up time                        | Start-up time after VDD reaches 95% to the time outputs are toggling with correct frequency (input = crystal or external clock) |       | 9   |       | ms   |

| t <sub>VDD</sub>       | Power supply ramp time (2)           | timing requirement for any VDD pin while PDN=LOW                                                                                | 0.1   |     | 30    | ms   |

- (1) POR threshold voltage is the power supply voltage at which the internal reset is deasserted. It is qualified internally with PDN.

- (2) VDD pin should monotonically reach 95% of its final value within supply ramp time. Parameters specified by characterization. All VDD pins were tied together for this evaluation. For non-monotonic or slower power supply ramp, it is recommended to pull-down PDN pin until VDD pins have reached 95% of its final value. PDN pin has a 50 kΩ pullup resistor. When PDN pin cannot be actively controlled, TI recommends to add a capacitor to GND on PDN pin to delay the release of reset.

### 7.22 I<sup>2</sup>C-Compatible Serial Interface Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

| PARAMETER       |                           | TEST CONDITIONS | MIN              | TYP MAX          | UNIT |

|-----------------|---------------------------|-----------------|------------------|------------------|------|

| V <sub>IH</sub> | Input Voltage, Logic High |                 | 0.7 x<br>VDD_REF |                  | V    |

| V <sub>IL</sub> | Input Voltage, Logic Low  |                 |                  | 0.3 ×<br>VDD_REF | V    |

| I <sub>IH</sub> | Input Leakage Current     | VDD_REF ± 10%   | -5               | 5                | μΑ   |

Product Folder Links: CDCE6214

RUMENTS

SNAS811 - JULY 2020

### I<sup>2</sup>C-Compatible Serial Interface Characteristics (continued)

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

| PARAMETER        |                          | TEST CONDITIONS             | MIN | TYP | MAX | UNIT |

|------------------|--------------------------|-----------------------------|-----|-----|-----|------|

| V <sub>OL</sub>  | Low Level Output Voltage | at 3 mA sink current        |     |     | 0.4 | V    |

| C <sub>IN</sub>  | Input Capacitance        |                             |     |     | 10  | pF   |

| C <sub>OUT</sub> | Output Capacitance       | max bus capacitance per pin |     |     | 400 | pF   |

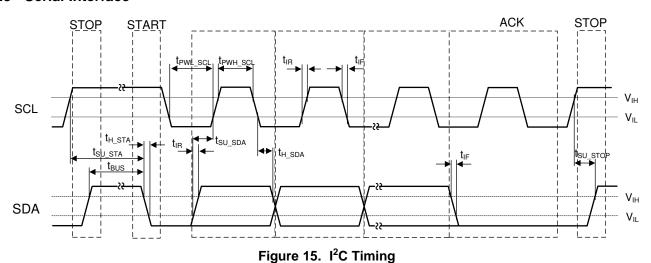

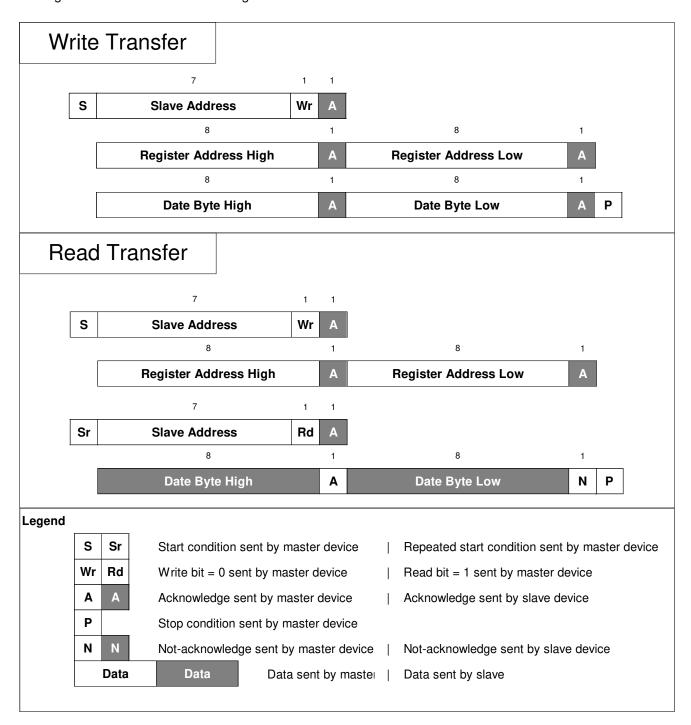

# 7.23 Timing Requirements, I<sup>2</sup>C-Compatible Serial Interface

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V + 5%\_2.5 V + 5%\_3.3 V + 5%\_and T<sub>0</sub> = -40°C to 105°C

|                      | PARAMETER                          | TEST CONDITIONS                                                                                   | MIN              | TYP | MAX  | UNIT              |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------|------------------|-----|------|-------------------|

| t <sub>PW_G</sub>    | Pulse Width of Suppressed Glitches |                                                                                                   |                  |     | 50   | ns                |

| f <sub>SCL</sub>     | SCL Clock Frequency                | Standard                                                                                          |                  | 100 |      | kHz               |

| f <sub>SCL</sub>     | SCL Clock Frequency                | Fast-mode                                                                                         |                  | 400 |      | kHz               |

| t <sub>SU_STA</sub>  | Setup Time Start Condition         | SCL=V <sub>IH</sub> before SDA=V <sub>IL</sub>                                                    |                  | 0.6 |      | μs                |

| t <sub>H_STA</sub>   | Hold Time Start Condition          | SCL=V <sub>IL</sub> after SCL=V <sub>IL</sub> After this time, the first clock edge is generated. |                  | 0.6 |      | μs                |

| t <sub>SU_SDA</sub>  | Setup Time Data                    | SDA valid after SCL=V <sub>IL</sub> , f <sub>SCL</sub> =100 kHz                                   | 250              |     |      | ns                |

| t <sub>SU_SDA</sub>  | Setup Time Data                    | SDA valid after SCL=V <sub>IL</sub> , f <sub>SCL</sub> =400 kHz                                   | 100              |     |      | ns                |

| t <sub>H_SDA</sub>   | Hold Time Data <sup>(1)</sup>      | SDA valid before SCL=V <sub>IH</sub>                                                              | 0 <sup>(2)</sup> |     |      | <sup>(3)</sup> µs |

| t <sub>VD_SDA</sub>  | Valid Data or Acknowledge Time     | f <sub>SCL</sub> =100 kHz <sup>(3)</sup>                                                          |                  |     | 3.45 | μs                |

| t <sub>VD_SDA</sub>  | Valid Data or Acknowledge Time     | f <sub>SCL</sub> =400 kHz <sup>(2)</sup>                                                          |                  |     | 0.9  | μs                |

| t <sub>PWH_SCL</sub> | Pulse Width High, SCL              | f <sub>SCL</sub> =100 kHz                                                                         | 4.0              |     |      | μs                |

| t <sub>PWH_SCL</sub> | Pulse Width High, SCL              | f <sub>SCL</sub> =400 kHz                                                                         | 0.6              |     |      | μs                |

| t <sub>PWL_SCL</sub> | Pulse Width Low, SCL               | f <sub>SCL</sub> =100 kHz                                                                         | 4.7              |     |      | μs                |

| t <sub>PWL_SCL</sub> | Pulse Width Low, SCL               | f <sub>SCL</sub> =400 kHz                                                                         | 1.3              |     |      | μs                |

| t <sub>IR</sub>      | Input Rise Time                    |                                                                                                   |                  |     | 300  | ns                |

| t <sub>IF</sub>      | Input Fall Time                    |                                                                                                   |                  |     | 300  | ns                |

| t <sub>OF</sub>      | Output Fall Time                   | 10 pF ≤ C <sub>OUT</sub> ≤ 400 pF                                                                 |                  |     | 250  | ns                |

| t <sub>SU_STOP</sub> | Setup Time Stop Condition          |                                                                                                   |                  | 0.6 |      | μs                |

| t <sub>BUS</sub>     | Bus-Free Time                      | Time between a Stop and a Start condition                                                         |                  | 1.3 |      | μs                |

- $t_{H\_SDA}$  is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge. A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the  $V_{IH(min)}$  of the SCL signal) to bridge

### 7.24 Power Supply Characteristics

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                     | PARAMETER                    | TEST CONDITIONS                                                                              | MIN TYP | MAX | UNIT |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------|---------|-----|------|

| I <sub>DD_REF</sub> | VDD_REF supply current       | 25 MHz XTAL, DBL ON                                                                          | 8       |     | mA   |

| I <sub>DD_VCO</sub> | VCO and PLL current          | $f_{VCO}$ =2400 MHz, PSA = PSB = 4 and N-divider = 48                                        | 14      |     | mA   |

| I <sub>DD_OUT</sub> | Output Channel Current       | IOD=6, LP-HCSL, 100MHz on OUT3 and OUT4, 25MHz on OUT0                                       | 22      |     | mA   |

| I <sub>DD_OUT</sub> | Output Channel Current       | IOD = 6, LP-HCSL, 100 MHz on OUT1 and OUT2                                                   | 17.5    |     | mA   |

| I <sub>DD_PDN</sub> | Power down current           | using reset pin / bits                                                                       | 2.8     | 5   | mA   |

| I <sub>DD_TYP</sub> | Typical current              | 4 x 100 MHz LVDS case using crystal input and doubler, SSC off                               | 50      | 70  | mA   |

| I <sub>DD_TYP</sub> | Typical current              | 4 x 100 MHz LP-HCSL case using crystal input and doubler, SSC off                            | 65      | 90  | mA   |

| L <sub>PSNR</sub>   | Power supply noise rejection | OUTx = 100 MHz differential, on one of VDDx injected sine wave at f <sub>INJ</sub> = 100 kHz | -61     |     | dB   |

the undefined region of the falling edge of SCL. The maximum  $t_{H\_SDA}$  could be 3.45  $\mu$ s and 0.9  $\mu$ s for Standard-mode and Fast-mode, but must be less than the maximum of  $t_{VD\_SDA}$  by a transition time. This maximum must only be met if the device does not stretch the LOW period ( $t_{PWL\_SCL}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the setup time before it releases the clock.

## **Power Supply Characteristics (continued)**

VDD\_VCO, VDDO\_12, VDDO\_34, VDD\_REF = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5% and T<sub>A</sub> = -40°C to 105°C

|                   | PARAMETER                    | TEST CONDITIONS                                                                            | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| L <sub>PSNR</sub> | Power supply noise rejection | OUTx = 100 MHz differential, on one of VDDx injected sine wave at f <sub>INJ</sub> = 1 MHz |     | -57 |     | dB   |

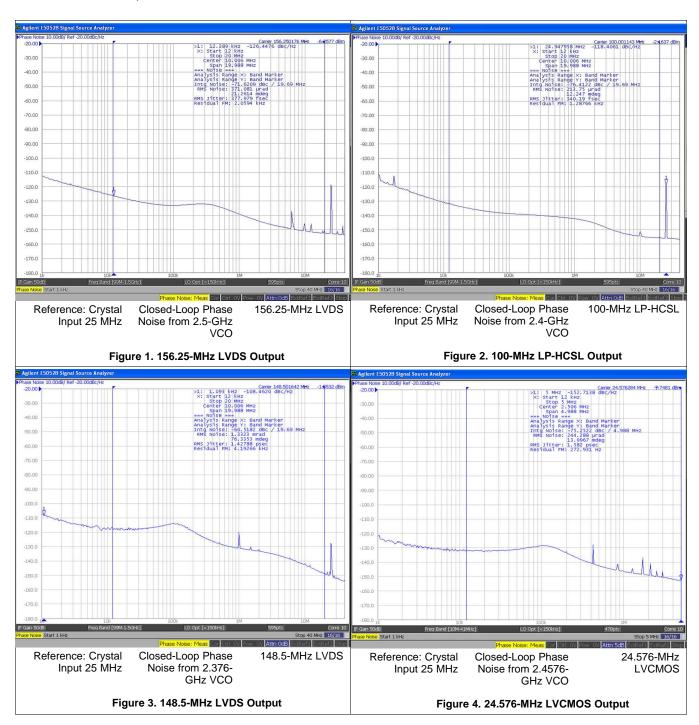

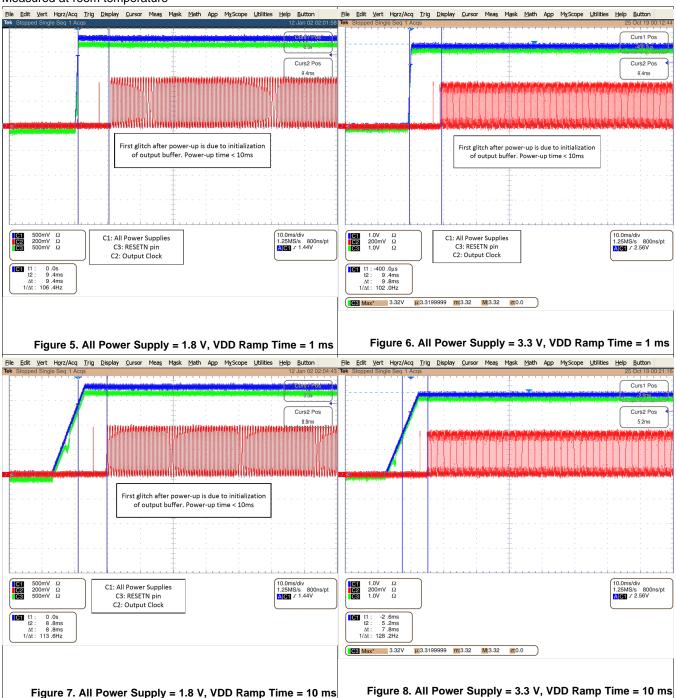

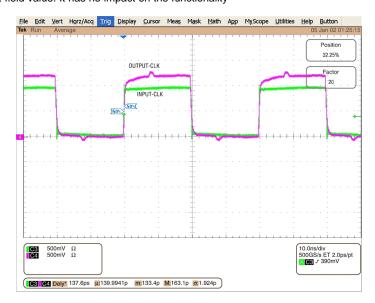

## 7.25 Typical Characteristics

Measured at room temperature

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

www.ti.com

# **Typical Characteristics (continued)**

Measured at room temperature

# TEXAS INSTRUMENTS

## **8 Parameter Measurement Information**

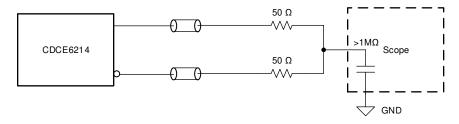

# 8.1 Reference Inputs

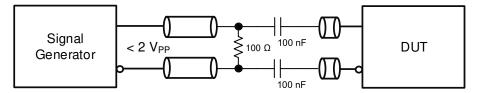

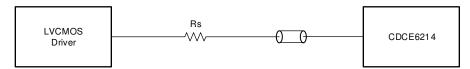

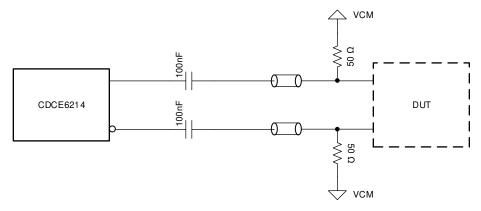

Figure 9. Differential AC-Coupled Input

## 8.2 Outputs

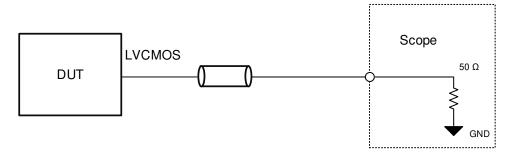

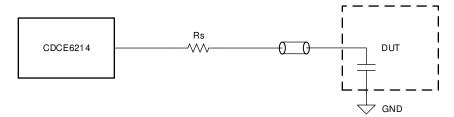

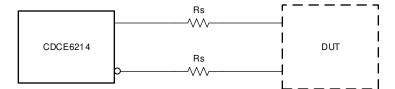

Figure 10. LVCMOS Output Test Configuration

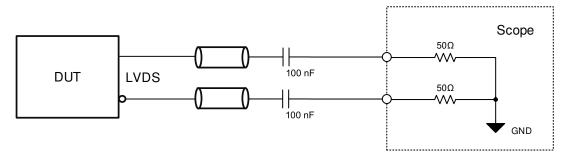

Figure 11. LVDS Output Test Configuration, AC-Coupled

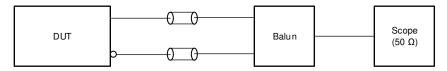

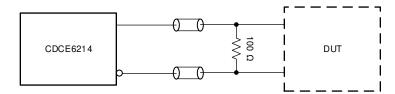

Figure 12. LP-HCSL Test Configuration, DC-Coupled

Figure 13. LVDS Common Mode Voltage, DC-Coupled

www.ti.com

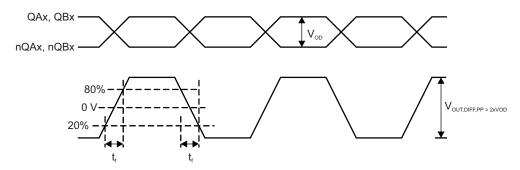

# **Outputs (continued)**

Figure 14. Differential Output Voltage and Rise/Fall Time

## 8.3 Serial Interface

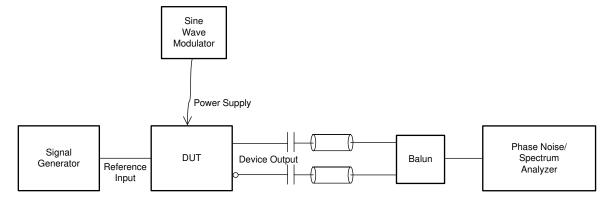

## 8.4 PSNR Test

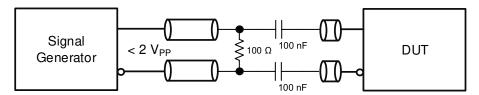

Figure 16. PSNR Test Configuration

Copyright © 2020, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

# 8.5 Clock Interfacing and Termination

## 8.5.1 Reference Input

Figure 17. Single-Ended LVCMOS to Reference

Figure 18. Differential Input to Reference

## 8.5.2 Outputs

Figure 19. LVCMOS Output

Figure 20. LVDS Output - DC-Coupled. Place 100 $\Omega$  close to the DUT

Figure 21. LVDS Output - AC-Coupled

Product Folder Links: CDCE6214

16

www.ti.com

# **Clock Interfacing and Termination (continued)**

Figure 22. LP-HCSL Output

# TEXAS INSTRUMENTS

### 9 Detailed Description

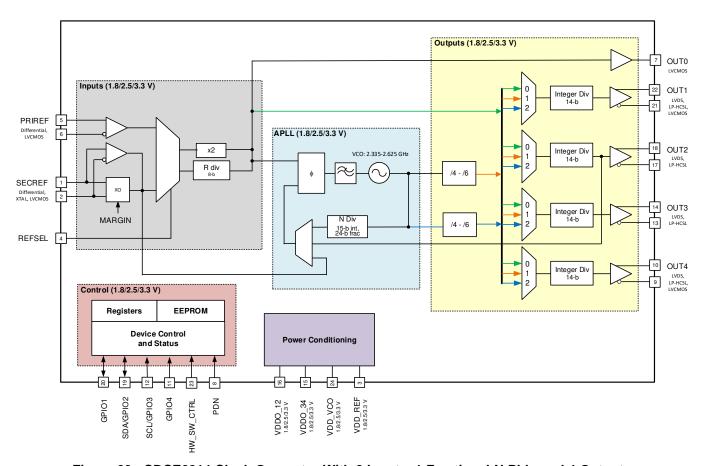

#### 9.1 Overview

The CDCE6214 clock generator is a Phase-Locked Loop (PLL) with integrated voltage controlled Oscillator (VCO) and integrated loop filter with selectable input reference. Input reference supports XTAL, Differential and single-ended LVCMOS inputs. The PLL consists of Frac-N PLL with integrated VCO range of 2335MHz - 2625MHz. The output of the VCO is connected to the clock distribution network, which includes multiple frequency dividers and multiplexers. The output of these network is connected to four output channels with configurable differential and single ended buffers. There are 4 power supply pins which can be independently configured to 1.8V/2.5V/3.3V. CDCE6214 can be configured using the I<sup>2</sup>C serial interface or built-in EEPROM at power up. This device supports various modes such as Digitally Controlled Oscillator (DCO) through GPIO/I2C and Internal/external Zero Delay mode.

### 9.2 Functional Block Diagram

Figure 23. CDCE6214 Clock Generator With 2 Inputs, 1 Fractional-N PLL, and 4 Outputs

## 9.3 Feature Description

The following sections describe the individual blocks of the CDCE6214 ultra low power clock generator.

www.ti.com

# **Feature Description (continued)**

#### 9.3.1 Reference Block

A reference clock to the PLL is fed to pins 1 (SECREF\_P) and 2 (SECREF\_N) or to pins 5 (PRIREF\_P) and 6 (PRIREF\_N). There are multiple input stages to accommodate various clock references. Pins 1 and 2 can be used to connect a XTAL across it or provide an external single-ended LVCMOS clock or a differential clock. These modes are selectable through register programming. When differential mode is selected, appropriated biasing is applied to the pin. In case of differential mode, external AC-coupling capacitor is needed. When XTAL or LVCMOS mode is selected, biasing circuitry is disengaged. Pins 5 and 6 can be used to provide an external single-ended LVCMOS clock or a differential clock.

The reference MUX selects the reference clock for the PLL. Setting REFSEL pin = L selects SECREF input, while setting REFSEL pin = H selects PRIREF Input. Alternatively, this can be configured through the register settings.

| REGISTER BIT ADDRESS | REGISTER BIT FIELD NAME | VALUE    | DESCRIPTION                                                                   |

|----------------------|-------------------------|----------|-------------------------------------------------------------------------------|

| R2[1:0]              | REFSEL_SW               | 0h or 1h | Input Reference Mux controlled through Pin 4 (REFSEL)                         |

|                      | (Default: 0h)           | 2h       | Pin1/Pin 2 SECREF Input<br>selected. This is independent of<br>Pin 4 status.  |

|                      |                         | 3h       | Pin 5/Pin 6 PRIREF Input<br>selected. This is independent of<br>Pin 4 status. |

| R24[1:0]             | IP_SECREF_BUF_SEL       | 0h       | XO enabled. Valid for SECREF pins.                                            |

|                      | (Default: 0h)           | 1h       | LVCMOS Buffer enabled. Valid for SECREF pins.                                 |

|                      |                         | 2h or 3h | Differential Buffer enabled. Valid for SECREF pins.                           |

| R24[15]              | IP_PRIREF_BUF_SEL       | 0h       | LVCMOS Buffer enabled. Valid for PRIREF pins.                                 |

|                      | (Default: 0h)           | 1h       | Differential Buffer enabled. Valid for PRIREF pins.                           |

**Table 1. Reference Input Selection**

A reference divider or a clock-doubler can be engaged to further multiply (2x) or divide the reference clock to the PLL. IP RDIV[7:0] can be used to set the value of the divider. Setting this to 00h would enable the doubler.

The output clock from the reference block can be bypassed to the OUT0 and other output channels. The bypassed clock is selectable between the Input clock or PFD clock. More details available in Table 9.