# **Dual N-Channel NexFET™ Power MOSFET**

Check for Samples: CSD86311W1723

### **FEATURES**

- Dual N-Ch MOSFETs

- Common Source Configuration

- Small Footprint 1.7 mm x 2.3 mm

- Ultra Low Q<sub>q</sub> and Q<sub>qd</sub>

- Pb Free

- RoHS Compliant

- Halogen Free

## **APPLICATIONS**

- Battery Management

- Battery Protection

- DC-DC Converters

#### DESCRIPTION

The device has been designed to deliver the lowest on resistance and gate charge in the smallest outline possible with thermal characteristics in an ultra low profile. Low on resistance and gate charge coupled with the small footprint and low profile make the device ideal for battery operated space constrained application in load management as well as DC-DC converter applications

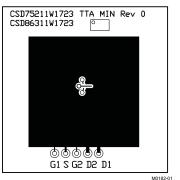

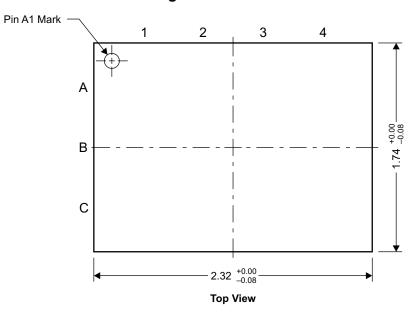

**Top View**

R<sub>DS(on)</sub> vs V<sub>GS</sub>

#### **PRODUCT SUMMARY**

| $V_{DS}$            | Drain to Source Voltage 25    |                         |     |    |

|---------------------|-------------------------------|-------------------------|-----|----|

| $Q_g$               | Gate Charge Total (4.5V)      | 3.1                     | 3.1 |    |

| $Q_{gd}$            | Gate Charge Gate to Drain     | 0.33                    |     | nC |

|                     |                               | $V_{GS} = 2.5V$         | 37  | mΩ |

| R <sub>DS(on)</sub> | Drain to Source On Resistance | $V_{GS} = 4.5V$         | 31  | mΩ |

|                     |                               | V <sub>GS</sub> = 8V 29 |     | mΩ |

| $V_{GS(th)}$        | Threshold Voltage             | 1                       |     | V  |

#### **ORDERING INFORMATION**

| Device        | Package                                   | Media       | Qty  | Ship             |

|---------------|-------------------------------------------|-------------|------|------------------|

| CSD86311W1723 | 1.7-mm × 2.3-mm<br>Wafer Level<br>Package | 7-inch reel | 3000 | Tape and<br>Reel |

#### **ABSOLUTE MAXIMUM RATINGS**

| T <sub>A</sub> = 2                   | 5°C unless otherwise stated                         | VALUE      | UNIT |

|--------------------------------------|-----------------------------------------------------|------------|------|

| V <sub>DS</sub>                      | Drain to Source Voltage                             | 25         | V    |

| $V_{GS}$                             | Gate to Source Voltage                              | +10 / -8   | V    |

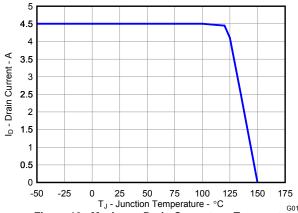

|                                      | Continuous Drain Current (1) (2)(3)                 | 4.5        | ^    |

| I <sub>D</sub>                       | Pulsed Drain Current (1) (2)(3)                     | 4.5        | Α    |

|                                      | Continuous Gate Clamp Current (4)                   | 6          | ^    |

| I <sub>G</sub>                       | Pulsed Gate Clamp Current (4)                       | 6          | Α    |

| P <sub>D</sub>                       | Power Dissipation (1)                               | 1.5        | W    |

| T <sub>J</sub> ,<br>T <sub>STG</sub> | Operating Junction and Storage<br>Temperature Range | -55 to 150 | °C   |

- (1) May be limited by Max source current

- (2) Based on Min Cu footprint

- (3) Per MOSFET

- (4) Total for device

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<u>SLPS251 – MAY 2010</u> www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

|                     | PARAMETER                        | TEST CONDITIONS                                  | MIN TYP     | MAX  | UNIT |

|---------------------|----------------------------------|--------------------------------------------------|-------------|------|------|

| Static Cl           | haracteristics                   |                                                  | <del></del> | -    |      |

| BV <sub>DSS</sub>   | Drain to Source Voltage          | $V_{GS} = 0V, I_D = 250\mu A$                    | 25          |      | V    |

| I <sub>DSS</sub>    | Drain to Source Leakage Current  | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 20V      |             | 1    | μΑ   |

| I <sub>GSS</sub>    | Gate to Source Leakage Current   | $V_{DS} = 0V, V_{GS} = +10 / -8V$                |             | ±100 | nA   |

| V <sub>GS(th)</sub> | Gate to Source Threshold Voltage | $V_{DS} = V_{GS}, I_D = 250 \mu A$               | 0.85 1      | 1.4  | ٧    |

|                     |                                  | V <sub>GS</sub> = 2.5V, I <sub>DS</sub> = 2A     | 37          | 51   | mΩ   |

| R <sub>DS(on)</sub> | Drain to Source On Resistance    | V <sub>GS</sub> = 4.5V, I <sub>DS</sub> = 2A     | 31          | 42   | mΩ   |

|                     |                                  | V <sub>GS</sub> = 8V, I <sub>DS</sub> = 2A       | 29          | 39   | mΩ   |

|                     |                                  | $V_{GS} = 2.5V, I_D = 2A$                        | 52          | 75   | mΩ   |

| R <sub>DD(on)</sub> | Drain to Drain On Resistance     | V <sub>GS</sub> = 4.5V, I <sub>DS</sub> = 2A     | 41          | 55   | mΩ   |

|                     |                                  | V <sub>GS</sub> = 8V, I <sub>DS</sub> = 2A       | 38          | 50   | mΩ   |

| 9 <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 10V, I <sub>D</sub> = 2A       | 6.4         |      | S    |

| Dynamic             | Characteristics                  | ,                                                |             | •    |      |

| C <sub>ISS</sub>    | Input Capacitance                | V <sub>GS</sub> = 0V,                            | 450         | 585  | pF   |

| Coss                | Output Capacitance               | $V_{DS} = 12.5V$ ,                               | 250         | 325  | pF   |

| C <sub>RSS</sub>    | Reverse Transfer Capacitance     | f = 1MHz                                         | 10          | 13   | pF   |

| R <sub>G</sub>      | Seried Gate Resistance           |                                                  | 1.4         | 2.8  | Ω    |

| Qg                  | Gate Charge Total (4.5V)         |                                                  | 3.1         | 4    | nC   |

| Q <sub>gd</sub>     | Gate Charge Gate to Drain        | V <sub>DS</sub> = 12.5V,                         | 0.33        |      | nC   |

| Q <sub>gs</sub>     | Gate Charge Gate to Source       | $I_D = 2A$                                       | 0.85        |      | nC   |

| Q <sub>g(th)</sub>  | Gate Charge at Vth               |                                                  | 0.48        |      | nC   |

| Q <sub>OSS</sub>    | Output Charge                    | $V_{DS} = 12.2V, V_{GS} = 0V$                    | 4.5         |      | nC   |

| t <sub>d(on)</sub>  | Turn On Delay Time               |                                                  | 5.4         |      | ns   |

| t <sub>r</sub>      | Rise Time                        | V <sub>DS</sub> = 12.5V, V <sub>GS</sub> = 4.5V, | 4.3         |      | ns   |

| t <sub>d(off)</sub> | Turn Off Delay Time              | $I_D = 2A, R_G = 2\Omega$                        | 13.2        |      | ns   |

| t <sub>f</sub>      | Fall Time                        |                                                  | 2.9         |      | ns   |

| Diode CI            | haracteristics                   | <del></del>                                      |             |      |      |

| V <sub>SD</sub>     | Diode Forward Voltage            | I <sub>S</sub> = 2A, V <sub>GS</sub> = 0V        | 0.78        | 1    | V    |

| Q <sub>rr</sub>     | Reverse Recovery Charge          | V <sub>dd</sub> = 12.2V, I <sub>F</sub> = 2A,    | 4.2         |      | nC   |

| t <sub>rr</sub>     | Reverse Recovery Time            | di/dt = 300A/μs                                  | 13.4        |      | ns   |

|                     |                                  |                                                  |             |      |      |

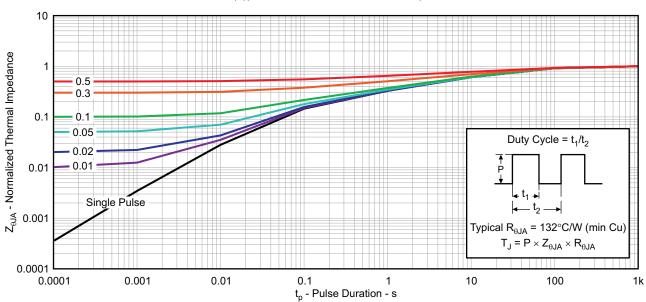

#### THERMAL CHARACTERISTICS

(T<sub>A</sub> = 25°C unless otherwise stated)

|                | PARAMETER                                                                  | MIN | TYP | MAX | UNIT |

|----------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| Rθ             | Thermal Resistance Junction to Ambient (Minimum Cu area) (1) (2)           |     |     | 165 | °C/W |

| R <sub>θ</sub> | Thermal Resistance Junction to Ambient (1 in <sup>2</sup> Cu area) (2) (3) |     |     | 68  | °C/W |

- (1) Device mounted on FR4 material with minimum Cu mounting area.

- (2) Measured with both devices biased in a parallel condition.

- (3) Device mounted on FR4 material with 1 in<sup>2</sup> of 2oz. Cu.

Submit Documentation Feedback

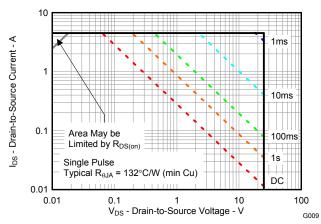

Max  $R_{\theta JA} = 68^{\circ}\text{C/W}$  when mounted on 1inch<sup>2</sup> of 2 oz. Cu.

Max  $R_{\theta JA} = 165^{\circ}\text{C/W}$  when mounted on minimum pad area of 2 oz. Cu.

#### TYPICAL MOSFET CHARACTERISTICS

(T<sub>A</sub> = 25°C unless otherwise stated)

Figure 1. Transient Thermal Impedance

G012

SLPS251 – MAY 2010 www.ti.com

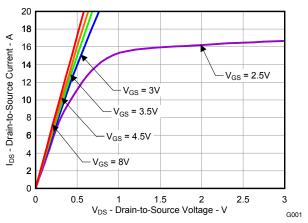

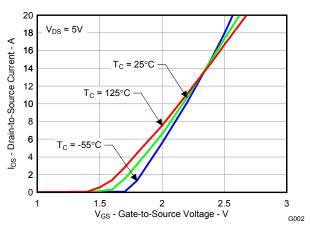

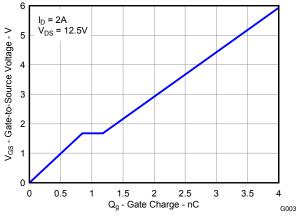

# **TYPICAL MOSFET CHARACTERISTICS (continued)**

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

Figure 2. Saturation Characteristics

**ISTRUMENTS**

Figure 3. Transfer Characteristics

Figure 4. Gate Charge

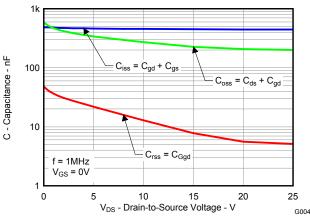

Figure 5. Capacitance

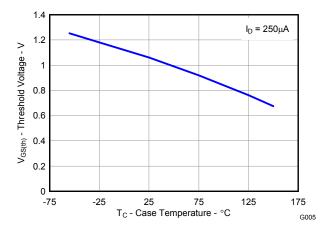

Figure 6. Threshold Voltage vs. Temperature

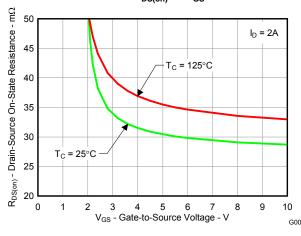

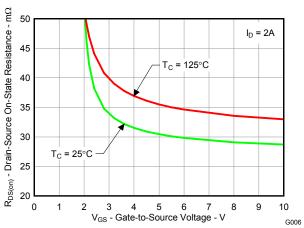

Figure 7.  $R_{DS(on)}$  vs. Gate-to-Source Voltage

## **TYPICAL MOSFET CHARACTERISTICS (continued)**

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

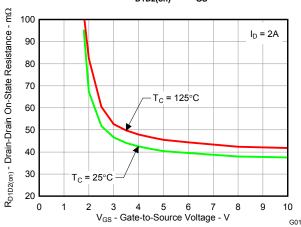

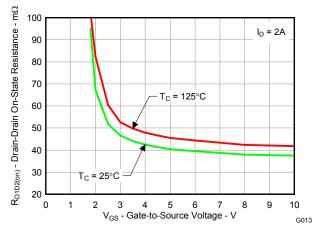

Figure 8. R<sub>D1D2(on)</sub> vs. Gate-to-Source Voltage

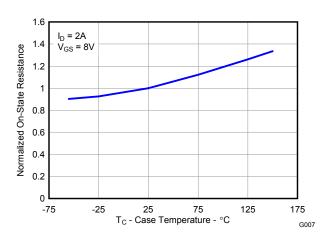

Figure 9. On Resistance vs. Temperature

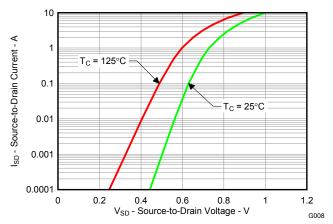

Figure 10. Typical Diode Forward Voltage

Figure 11. Maximum Safe Operating Area

Figure 12. Maximum Drain Current vs. Temperature

SLPS251 - MAY 2010 www.ti.com

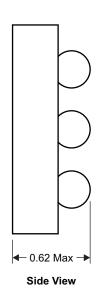

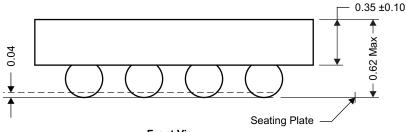

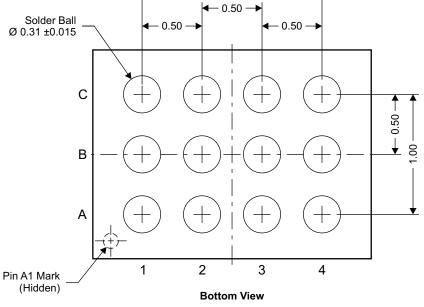

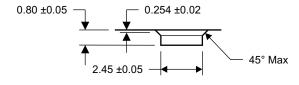

#### **MECHANICAL DATA**

# CSD86311W1723 Package Dimensions

**INSTRUMENTS**

| Pinout         |             |  |  |  |  |  |

|----------------|-------------|--|--|--|--|--|

| Position       | Designation |  |  |  |  |  |

| A2, A3, A4     | Drain 1     |  |  |  |  |  |

| C2, C3, C4     | Drain 2     |  |  |  |  |  |

| A1             | Gate 1      |  |  |  |  |  |

| C1             | Gate 2      |  |  |  |  |  |

| B1, B2, B3, B4 | Source      |  |  |  |  |  |

M0184-01

NOTE: All dimensions are in mm (unless otherwise specified)

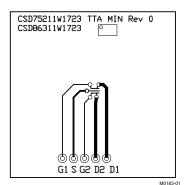

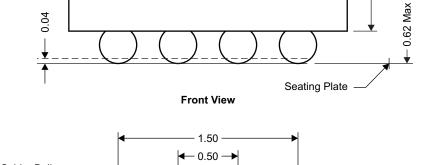

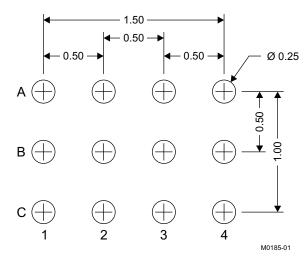

#### **Land Pattern Recommendation**

NOTE: All dimensions are in mm (unless otherwise specified)

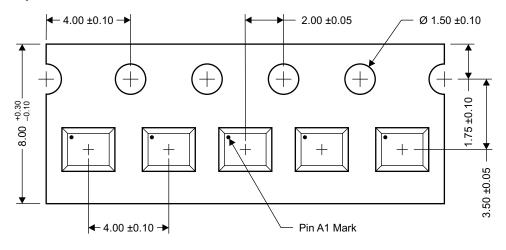

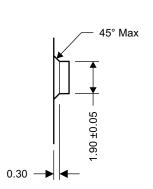

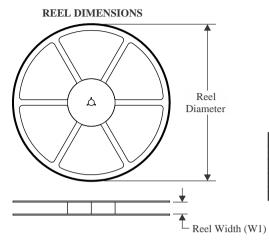

# **Tape and Reel Information**

M0186-01

NOTE: All dimensions are in mm (unless otherwise specified)

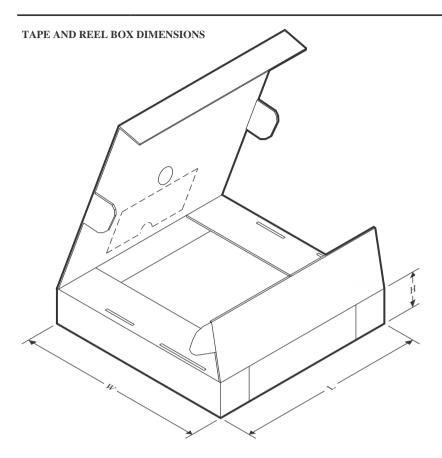

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

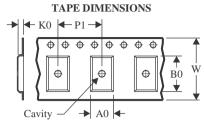

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

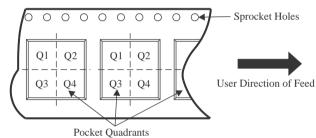

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CSD86311W1723 | DSBGA           | YZG                | 12 | 3000 | 180.0                    | 8.4                      | 2.38       | 1.8        | 0.69       | 4.0        | 8.0       | Q2               |

| CSD86311W1723 | DSBGA           | YZG                | 12 | 3000 | 179.0                    | 14.4                     | 2.45       | 1.9        | 0.8        | 4.0        | 8.0       | Q1               |

www.ti.com 9-Aug-2022

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD86311W1723 | DSBGA        | YZG             | 12   | 3000 | 182.0       | 182.0      | 20.0        |

| CSD86311W1723 | DSBGA        | YZG             | 12   | 3000 | 199.0       | 211.0      | 35.0        |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated