**INA823** SBOSA75B - JULY 2021 - REVISED NOVEMBER 2021

# INA823 Precision, Low-Power, Wide-Supply (2.7-V to 36-V) Instrumentation Amplifier

#### 1 Features

- Input overvoltage protection up to ±60 V

- Input voltage extends 150 mV below negative vlagus

- Low power supply current: 180 µA (typ)

- Precision performance:

- Low offset voltage: 20 μV (typ), 100 μV (max)

- Low input bias current: 8nA (max)

- Common-mode rejection:

- $84 \, dB, G = 1 \, (min)$

- 104 dB, G = 10 (min)

- 120 dB, G ≥ 100 (min)

- Power supply rejection: 100 dB, G = 1 (min)

- Input voltage noise: 21 nV/√Hz

- Bandwidth: 1.9 MHz (G = 1), 60 kHz (G = 100)

- Stable with 1-nF capacitive loads

- Supply range:

- Single-supply: 2.7 V to 36 V

- Dual-supply: ±1.35 V to ±18 V

- Specified temperature range: -40°C to +125°C

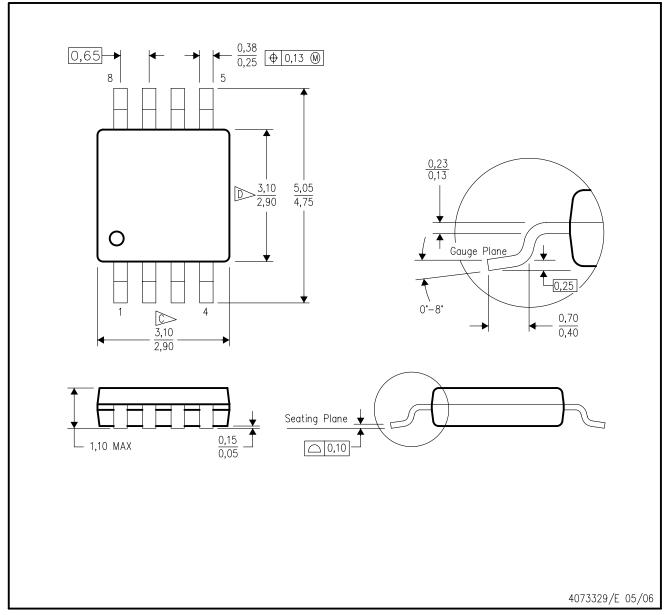

- Packages: 8-pin SOIC and 8-pin VSSOP

# 2 Applications

- Flow transmitter

- Wearable fitness and activity monitor

- Infusion pump

- Blood glucose monitor

- Electrocardiogram (ECG)

- Surgical equipment

- Weigh scale

- Analog input module

- Process analytics (pH, gas, concentration, force and humidity)

- Battery test

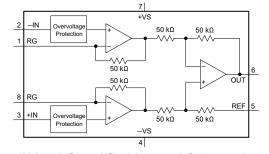

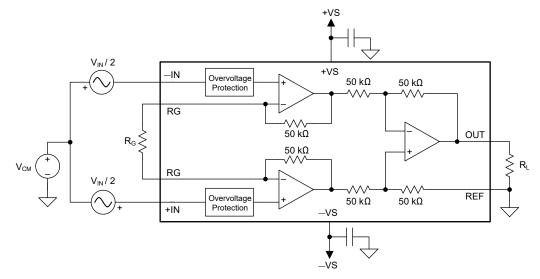

**INA823 Simplified Internal Schematic**

# 3 Description

The INA823 is an integrated instrumentation amplifier that offers low power consumption and operates over a wide, single-supply or dual-supply range. A single external resistor sets any gain from 1 to 10,000. The device provides low input offset voltage, low offset voltage drift, low input bias current, and low current noise while remaining cost-effective. Additional circuitry protects the inputs against overvoltage up to ±60 V.

The INA823 is optimized to provide a high commonmode rejection ratio. At G = 1, the common-mode rejection ratio exceeds 84 dB across the full input common-mode range. The INA823 has a wide common-mode voltage range as low as 150-mV below negative supply. The device is designed for low-voltage operation from a 2.7-V single supply, and dual supplies up to ±18 V. The low power and single supply operation enable hand-held, battery-operated systems.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |

|-------------|------------------------|-------------------|--|

| INA823      | SOIC (8)               | 4.90 mm × 3.91 mm |  |

| IIVA023     | VSSOP (8)              | 3.00 mm x 3.00 mm |  |

For all available packages, see the package option addendum at the end of the data sheet.

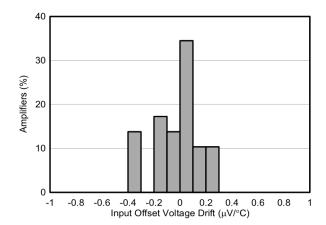

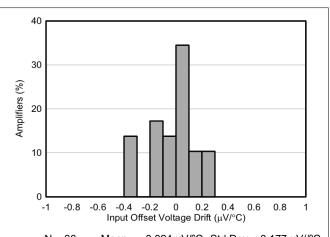

Typical Distribution of Input Stage Offset Voltage Drift

# **Table of Contents**

| 1 Features1                           | 9 Application and Implementation2                     |

|---------------------------------------|-------------------------------------------------------|

| 2 Applications1                       |                                                       |

| 3 Description1                        |                                                       |

| 4 Revision History2                   |                                                       |

| 5 Device Comparison Table3            |                                                       |

| 6 Pin Configuration and Functions3    |                                                       |

| 7 Specifications4                     |                                                       |

| 7.1 Absolute Maximum Ratings4         | 12 Device and Documentation Support3                  |

| 7.2 ESD Ratings4                      |                                                       |

| 7.3 Recommended Operating Conditions4 | 12.2 Documentation Support3                           |

| 7.4 Thermal Information4              | 12.3 Receiving Notification of Documentation Updates3 |

| 7.5 Electrical Characteristics5       | 12.4 Support Resources3                               |

| 7.6 Typical Characteristics7          | 12.5 Trademarks3                                      |

| 8 Detailed Description19              |                                                       |

| 8.1 Overview19                        | 12.7 Glossary3                                        |

| 8.2 Functional Block Diagram19        | 13 Mechanical, Packaging, and Orderable               |

| 8.3 Feature Description20             | Information3                                          |

| 8.4 Device Functional Modes22         |                                                       |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision A (April 2019) to Revision B (November 2021)Page• Changed device from advanced information (preview) to production data (active)1

# **5 Device Comparison Table**

| DEVICE | DESCRIPTION                                                                                                                   | GAIN EQUATION        | RG AT PINS |

|--------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|

| INA849 | 1-nV/√Hz Noise, 35-μV Offset, 0.4 μV/°C V <sub>OS</sub> Drift, 28-MHz Bandwidth, Precision Instrumentation Amplifier          | G = 1 + 6 kΩ / RG    | 2, 3       |

| INA821 | 35-μV Offset, 0.4 μV/°C V <sub>OS</sub> Drift, 7-nV/√Hz Noise, High-Bandwidth, Precision Instrumentation Amplifier            | G = 1 + 49.4 kΩ / RG | 2, 3       |

| INA819 | 35-μV Offset, 0.4 μV/°C V <sub>OS</sub> Drift, 8-nV/√Hz Noise, Low-Power, Precision Instrumentation Amplifier                 | G = 1 + 50 kΩ / RG   | 2, 3       |

| INA826 | 200-µA Supply Current, 3-V to 36-V Supply Instrumentation Amplifier With Rail-to-Rail Output                                  | G = 1 + 49.4 kΩ / RG | 2, 3       |

| INA818 | 35-μV Offset, 0.4 μV/°C V <sub>OS</sub> Drift, 8-nV/√Hz Noise, Low-Power, Precision Instrumentation Amplifier                 | G = 1 + 50 kΩ / RG   | 1, 8       |

| INA828 | 50-μV Offset, 0.5 μV/°C V <sub>OS</sub> Drift, 7-nV/√Hz Noise, Low-Power, Precision Instrumentation Amplifier                 | G = 1 + 50 kΩ / RG   | 1, 8       |

| INA333 | 25-μV V <sub>OS</sub> , 0.1 μV/°C V <sub>OS</sub> Drift, 1.8-V to 5-V, RRO, 50-μA I <sub>Q</sub> , Chopper-Stabilized INA     | G = 1 + 100 kΩ / RG  | 1, 8       |

| PGA280 | 1/8 V/V to 128 V/V Programmable Gain Instrumentation Amplifier With 3-V or 5-V Differential Output; Analog Supply up to ±18 V | Digital programmable | N/A        |

| INA159 | G = 0.2 V Differential Amplifier for ±10-V to 3-V and 5-V Conversion                                                          | G = 0.2 V/V          | N/A        |

| PGA112 | Precision Programmable Gain Op Amp With SPI                                                                                   | Digital programmable | N/A        |

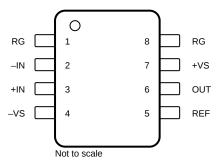

# **6 Pin Configuration and Functions**

Figure 6-1. D (8-Pin SOIC) and DGK (8-Pin VSSOP) Packages, Top View

Table 6-1. Pin Functions

| PIN  |      | TYPE   | DESCRIPTION                                                         |  |

|------|------|--------|---------------------------------------------------------------------|--|

| NAME | NO.  | ITPE   | DESCRIPTION                                                         |  |

| -IN  | 2    | Input  | Negative (inverting) input                                          |  |

| +IN  | 3    | Input  | Positive (noninverting) input                                       |  |

| OUT  | 6    | Output | Output                                                              |  |

| REF  | 5    | Input  | Reference input. This pin must be driven by a low impedance source. |  |

| RG   | 1, 8 | _      | Gain setting pin. Place a gain resistor between pin 1 and pin 8.    |  |

| -VS  | 4    | Power  | Negative supply                                                     |  |

| +VS  | 7    | Power  | Positive supply                                                     |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                             |                                      | MIN                      | MAX                      | UNIT |

|------------------|---------------------------------------------|--------------------------------------|--------------------------|--------------------------|------|

| Vs               | –VS, +VS pins voltage                       | Dual supply, $V_S = (+V_S) - (-V_S)$ |                          | ± 20                     | V    |

| vs               | -v3, +v3 piris voltage                      | Single supply, $V_S = (+V_S)$        |                          | 40                       | V    |

|                  | IN pins voltage                             |                                      | (-V <sub>S</sub> ) - 60  | (+V <sub>S</sub> ) + 60  | V    |

|                  | RG, REF, OUT pins voltage                   |                                      | (-V <sub>S</sub> ) - 0.5 | (+V <sub>S</sub> ) + 0.5 | V    |

|                  | RG pins current                             |                                      | -10                      | 10                       | mA   |

|                  | OUT pin current                             |                                      | -50                      | 50                       | mA   |

| I <sub>SC</sub>  | Output short-circuit current <sup>(2)</sup> |                                      | Continuous               |                          |      |

| T <sub>A</sub>   | Operating temperature                       |                                      | -50                      | 150                      | °C   |

| TJ               | Junction temperature                        |                                      |                          | 175                      | °C   |

| T <sub>stg</sub> | Storage temperature                         |                                      | <b>–</b> 65              | 150                      | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 7.2 ESD Ratings

|        |                          |                                                                       | VALUE | UNIT |

|--------|--------------------------|-----------------------------------------------------------------------|-------|------|

| V      | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V(ESD) | Electrostatic discriarge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±750  | v    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                       |                                      | MIN   | MAX | UNIT |

|----------------|-----------------------|--------------------------------------|-------|-----|------|

| Ve             | Supply voltage        | Single supply, $V_S = (+V_S)$        | 2.7   | 36  | V    |

| V <sub>S</sub> | Supply voltage        | Dual supply, $V_S = (+V_S) - (-V_S)$ | ±1.35 | ±18 | V    |

| T <sub>A</sub> | Specified temperature |                                      | -40   | 125 | °C   |

#### 7.4 Thermal Information

|                       |                                              |          | INA823      |      |  |

|-----------------------|----------------------------------------------|----------|-------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (VSSOP) | UNIT |  |

|                       |                                              | 8 PINS   | 8 PINS      |      |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 126.7    | 167.5       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 67.0     | 60.3        | °C/W |  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 70.1     | 88.7        | °C/W |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 18.6     | 7.9         | °C/W |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 69.4     | 87.1        | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a      | n/a         | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: INA823

<sup>(2)</sup> Short-circuit to V<sub>S</sub> / 2.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

at  $T_A$  = 25°C,  $V_S$  = ±15 V,  $R_L$  = 10 k $\Omega$ ,  $V_{CM}$  =  $V_{REF}$  = 0 V, and G = 1 (unless otherwise noted)

|                  | PARAMETER                                         | TEST                                                                                    | CONDITIONS                                                      | MIN             | TYP           | MAX            | UNIT                  |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|---------------|----------------|-----------------------|

| INPUT            |                                                   |                                                                                         |                                                                 |                 |               |                |                       |

|                  |                                                   |                                                                                         |                                                                 |                 | 20            | 100            | .,                    |

| V <sub>OSI</sub> | Input stage offset voltage(1) (3)                 | T = 40°C to 1405°C(2)                                                                   |                                                                 |                 |               | 190            | μV                    |

|                  |                                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C^{(2)}$                                    | )                                                               |                 | 0.2           | 1.2            | μV/°C                 |

|                  |                                                   |                                                                                         |                                                                 |                 | 140           | 450            | /                     |

| $V_{OSO}$        | Output stage offset voltage <sup>(1)</sup> (3)    | T = 40°C to ±125°C(2                                                                    | )                                                               |                 |               | 850            | μV                    |

|                  |                                                   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}^{(2)}$                              | ,                                                               |                 | 1             | 5              | μV/°C                 |

|                  |                                                   |                                                                                         | G = 1, RTI                                                      | 100             | 130           |                |                       |

| PSRR             | Power-supply rejection ratio                      | V <sub>S</sub> = ±1.35 V to ±18 V                                                       | G = 10, RTI                                                     | 115             | 148           |                | dB                    |

| FOINIX           | rower-supply rejection ratio                      | VS - 11.33 V 10 110 V                                                                   | G = 100, RTI                                                    | 120             | 148           |                | uБ                    |

|                  |                                                   |                                                                                         | G = 1000, RTI                                                   | 120             | 148           |                |                       |

| Z <sub>IN</sub>  | Input impedance                                   |                                                                                         |                                                                 |                 | 12    8.5     |                | GΩ    pF              |

|                  | RFI filter, -3-dB frequency                       |                                                                                         |                                                                 |                 | 20            |                | MHz                   |

| $V_{CM}$         | Operating input voltage <sup>(4)</sup>            | V <sub>S</sub> = ±1.35 V to ±18 V                                                       |                                                                 | $(-V_S) - 0.15$ |               | $(+V_{S}) - 1$ | +V <sub>S</sub> ) – 1 |

| V CM             | Operating input voltage.                          | VS - 11.00 V to 110 V                                                                   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ See Figure |                 | e Figure 7-53 |                | V                     |

|                  | Input overvoltage                                 | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}^{(2)}$                              | )                                                               |                 |               | ±60            | V                     |

|                  |                                                   | At dc to 60 Hz, RTI, $V_{CM} = (V-) -0.15 V$ to $(V+) - 1 V$ , $G = 1$                  |                                                                 | 84              | 110           |                | dB                    |

| CMRR             | Common-mode rejection ratio                       | At dc to 60 Hz, RTI, $V_{CM} = (V-) -0.15 \text{ V}$ to $(V+) - 1 \text{ V}$ , $G = 10$ |                                                                 | 104             | 136           |                |                       |

|                  |                                                   | At dc to 60 Hz, RTI, V <sub>C</sub> M<br>G ≥ 100                                        | $_{\text{M}}$ = (V-) -0.15 V to (V+) - 1 V,                     | 120             | 149           |                |                       |

| BIAS CI          | JRRENT                                            |                                                                                         |                                                                 |                 |               |                |                       |

|                  |                                                   |                                                                                         |                                                                 |                 | 1.2           | 8              |                       |

| I <sub>B</sub>   | Input bias current                                | T <sub>A</sub> = -40°C to +125°C                                                        |                                                                 |                 | 2.4           |                | nA                    |

|                  |                                                   |                                                                                         |                                                                 |                 | 15            |                | pA/°C                 |

|                  |                                                   |                                                                                         |                                                                 |                 | 0.4           | 4              | nA                    |

| los              | Input offset current                              | T <sub>A</sub> = -40°C to +125°C                                                        |                                                                 |                 | 0.8           |                | ΠA                    |

|                  |                                                   |                                                                                         |                                                                 |                 | 4             |                | pA/°C                 |

| NOISE \          | /OLTAGE                                           |                                                                                         |                                                                 |                 |               |                |                       |

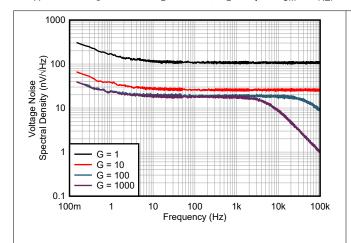

| e <sub>NI</sub>  | Input stage voltage noise density <sup>(6)</sup>  | f = 1 kHz, G = 1000, R <sub>S</sub>                                                     | = 0 Ω                                                           |                 | 21            |                | nV/√ <del>Hz</del>    |

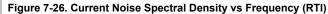

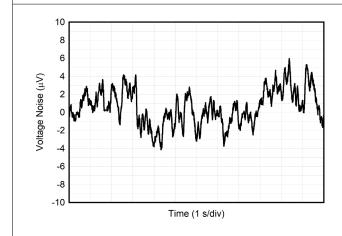

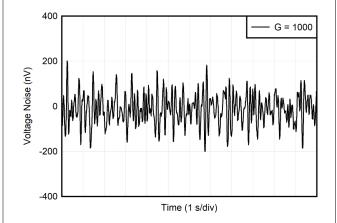

|                  | Input stage voltage noise <sup>(6)</sup>          | $f_B$ = 0.1 Hz to 10 Hz, G = 1000, $R_S$ = 0 Ω                                          |                                                                 |                 | 0.4           |                | μV <sub>PP</sub>      |

| e <sub>NO</sub>  | Output stage voltage noise density <sup>(6)</sup> | f = 1 kHz, R <sub>S</sub> = 0 Ω                                                         |                                                                 |                 | 120           |                | nV/√ <del>Hz</del>    |

| NO               | Output stage voltage noise <sup>(6)</sup>         | f <sub>B</sub> = 0.1 Hz to 10 Hz, R <sub>S</sub>                                        | ; = 0 Ω                                                         |                 | 5             |                | μV <sub>PP</sub>      |

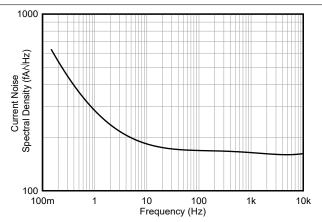

|                  | Current noise density                             | f = 1 kHz                                                                               |                                                                 |                 | 160           |                | fA/√ <del>Hz</del>    |

| In               | Current noise                                     | f <sub>B</sub> = 0.1 Hz to 10 Hz, G                                                     | = 100                                                           |                 | 5             |                | pA <sub>PP</sub>      |

# 7.5 Electrical Characteristics (continued)

at  $T_A = 25^{\circ}$ C,  $V_S = \pm 15$  V,  $R_I = 10$  k $\Omega$ ,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

|                  | PARAMETER                    | TEST                                                 | CONDITIONS                                           | MIN                       | TYP                       | MAX                       | UNIT   |

|------------------|------------------------------|------------------------------------------------------|------------------------------------------------------|---------------------------|---------------------------|---------------------------|--------|

| GAIN             |                              |                                                      |                                                      |                           |                           |                           |        |

|                  | Gain equation                |                                                      |                                                      | 1 + (1                    | 100 kΩ / R <sub>G</sub> ) |                           | V/V    |

| G                | Gain                         |                                                      |                                                      | 1                         |                           | 10000                     | V/V    |

|                  |                              |                                                      | G = 1                                                |                           | ±0.01                     | ±0.04                     | 0/     |

| 05               | (5)                          |                                                      | G = 10                                               |                           | ±0.025                    | ±0.2                      |        |

| GE               | Gain error <sup>(5)</sup>    | V <sub>O</sub> = ±10 V                               | G = 100                                              |                           | ±0.025                    | ±0.2                      | %      |

|                  |                              |                                                      | G = 1000                                             |                           | ±0.05                     | ±0.2                      |        |

|                  | O-in-duit(5)                 | T - 40°0 t- 1405°0                                   | G = 1                                                |                           | ±0.2                      | ±5                        | /00    |

|                  | Gain drift <sup>(5)</sup>    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | G > 1                                                |                           | ±12                       | ±35                       | ppm/°C |

|                  |                              | G = 1 to 10                                          | -                                                    |                           | 2                         | 10                        |        |

|                  | Gain nonlinearity            | G > 10                                               |                                                      |                           | 5                         |                           | ppm    |

|                  |                              | $G = 1$ to 100, $R_L = 2$ kΩ                         |                                                      |                           | 15                        |                           |        |

| OUTPL            | JT                           |                                                      |                                                      |                           |                           |                           |        |

|                  | Output voltage swing         |                                                      |                                                      | (-V <sub>S</sub> ) + 0.15 |                           | (+V <sub>S</sub> ) – 0.15 | V      |

|                  | Load capacitance             | Stable operation                                     |                                                      |                           | 1000                      |                           | pF     |

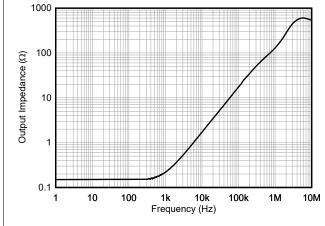

| Z <sub>OUT</sub> | Closed-loop output impedance |                                                      |                                                      | See                       | Figure 7-37               |                           | Ω      |

| I <sub>SC</sub>  | Short-circuit current        | Continuous to V <sub>S</sub> / 2                     |                                                      |                           | ±20                       |                           | mA     |

| FREQU            | JENCY RESPONSE               |                                                      |                                                      |                           |                           |                           |        |

|                  |                              | G = 1                                                |                                                      |                           | 1.9                       |                           | MHz    |

| DW               | Ddividelle 0 dD              | G = 10                                               |                                                      |                           | 350                       |                           |        |

| BW               | Bandwidth, –3 dB             | G = 100                                              |                                                      |                           | 60                        |                           | kHz    |

|                  |                              | G = 1000                                             |                                                      |                           | 6                         |                           |        |

| SR               | Slew rate                    | G = 1, V <sub>O</sub> = ±10 V                        |                                                      |                           | 0.9                       |                           | V/µs   |

|                  |                              |                                                      | G = 1 to 10, V <sub>STEP</sub> = 10 V                |                           | 12                        |                           |        |

|                  |                              | To 0.01%                                             | G = 100, V <sub>STEP</sub> = 10 V                    |                           | 28                        |                           |        |

|                  | Cattling time                |                                                      | G = 1000, V <sub>STEP</sub> = 10 V                   |                           | 260                       |                           |        |

| ts               | Settling time                |                                                      | G = 1 to 10, V <sub>STEP</sub> = 10 V                |                           | 14                        |                           | μs     |

|                  |                              | To 0.001%                                            | G = 100, V <sub>STEP</sub> = 10 V                    |                           | 33                        |                           |        |

|                  |                              |                                                      | G = 1000, V <sub>STEP</sub> = 10 V                   |                           | 290                       |                           |        |

| REFER            | RENCE INPUT                  |                                                      | •                                                    |                           |                           |                           |        |

| R <sub>IN</sub>  | Input impedance              |                                                      |                                                      |                           | 100                       |                           | kΩ     |

|                  | Reference input voltage      |                                                      |                                                      | (-V <sub>S</sub> )        |                           | (+V <sub>S</sub> )        | V      |

|                  | Gain to output               |                                                      |                                                      |                           | 1                         |                           | V/V    |

|                  | Reference gain error         | inside the output voltage                            | e swing                                              |                           | 0.01                      | 0.05                      | %      |

| POWE             | R SUPPLY                     |                                                      |                                                      |                           |                           |                           |        |

| 1.               | Quiogoant gurrent            | V = 0.V                                              |                                                      |                           | 180                       | 250                       |        |

| IQ               | Quiescent current            | V <sub>IN</sub> = 0 V                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                           |                           | 300                       | μΑ     |

- Total offset, referred-to-input (RTI):  $V_{OS} = (V_{OSI}) + (V_{OSO} / G)$ . (1)

- Specified by characterization. (2)

- (3)

- Offset drifts are uncorrelated. Input-referred offset drift is calculated using:  $\Delta V_{OS(RTI)} = \sqrt{[\Delta V_{OS)}]^2 + (\Delta V_{OSO}/G)^2}$ . Input voltage range of the instrumentation amplifier input stage. The input range depends on the common-mode voltage, differential voltage, gain, and reference voltage. See Typical Characteristic curves for more information.

- The values specified for G > 1 do not include the effects of the external gain-setting resistor,  $R_G$ . Total RTI voltage noise is equal to:  $e_{N(RTI)} = \sqrt{[e_{NI}\ ^2 + (e_{NO}\ /\ G)^2]}$ . (5)

# 7.6 Typical Characteristics

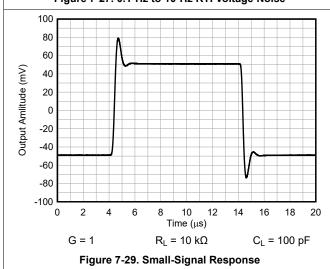

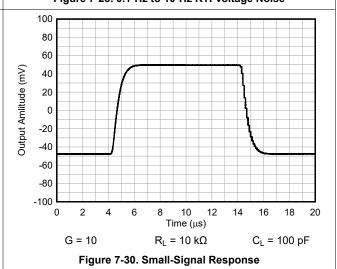

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

# Table 7-1. Table of Graphs

| FIGURE TITLE                                              | FIGURE NUMBER |

|-----------------------------------------------------------|---------------|

| Typical Distribution Graphs                               |               |

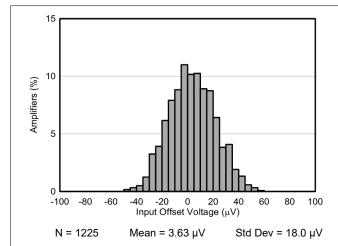

| Typical Distribution of Input Stage Offset Voltage        | Figure 7-1    |

| Typical Distribution of Input Stage Offset Voltage Drift  | Figure 7-2    |

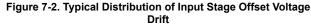

| Typical Distribution of Output Stage Offset Voltage       | Figure 7-3    |

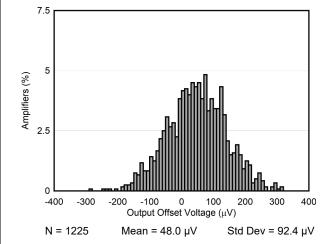

| Typical Distribution of Output Stage Offset Voltage Drift | Figure 7-4    |

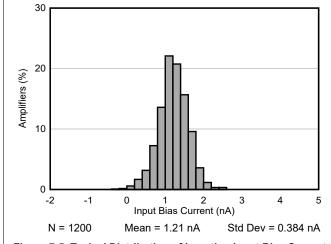

| Typical Distribution of Inverting Input Bias Current      | Figure 7-5    |

| Typical Distribution of Noninverting Input Bias Current   | Figure 7-6    |

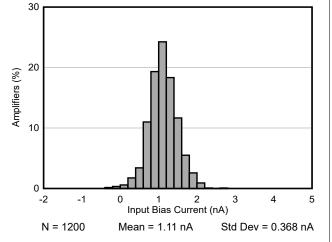

| Typical Distribution of Input Offset Current              | Figure 7-7    |

| Typical CMRR Distribution, G = 1                          | Figure 7-8    |

| Typical CMRR Distribution, G = 10                         | Figure 7-9    |

| Typical Gain Error Distribution                           | Figure 7-10   |

| vs Temperature Graphs                                     | <u>'</u>      |

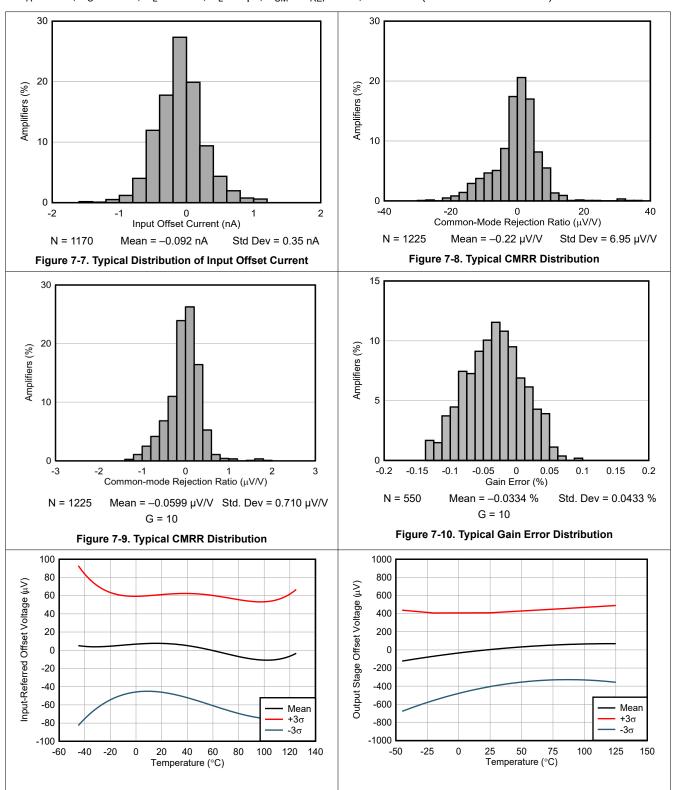

| Input Stage Offset Voltage vs Temperature                 | Figure 7-11   |

| Output Stage Offset Voltage vs Temperature                | Figure 7-12   |

| Input Bias Current vs Temperature                         | Figure 7-13   |

| Input Offset Current vs Temperature                       | Figure 7-14   |

| CMRR vs Temperature, G = 1                                | Figure 7-15   |

| CMRR vs Temperature, G = 10                               | Figure 7-16   |

| Gain Error vs Temperature, G = 1                          | Figure 7-17   |

| Gain Error vs Temperature, G = 100                        | Figure 7-18   |

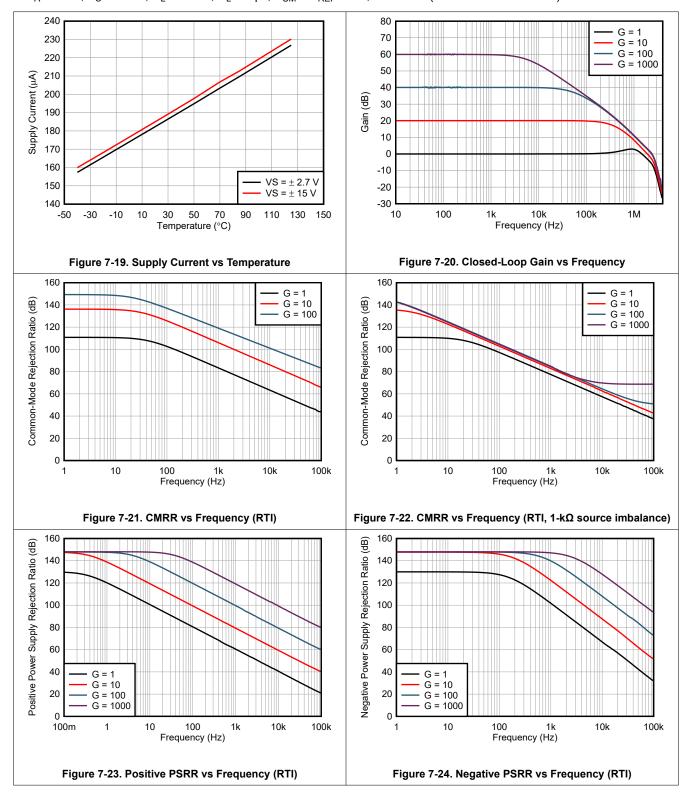

| Supply Current vs Temperature                             | Figure 7-19   |

| AC Performance Graphs                                     | <u>'</u>      |

| Closed-Loop Gain vs Frequency                             | Figure 7-20   |

| CMRR vs Frequency (RTI)                                   | Figure 7-21   |

| CMRR vs Frequency (RTI, 1-kΩ source imbalance)            | Figure 7-22   |

| Positive PSRR vs Frequency (RTI)                          | Figure 7-23   |

| Negative PSRR vs Frequency (RTI)                          | Figure 7-24   |

| Voltage Noise Spectral Density vs Frequency (RTI)         | Figure 7-25   |

| Current Noise Spectral Density vs Frequency (RTI)         | Figure 7-26   |

| 0.1-Hz to 10-Hz RTI Voltage Noise                         | Figure 7-27   |

| 0.1-Hz to 10-Hz RTI Voltage Noise, G = 1000               | Figure 7-28   |

| Small-Signal Response, G = 1                              | Figure 7-29   |

| Small-Signal Response, G = 10                             | Figure 7-30   |

| Small-Signal Response, G = 100                            | Figure 7-31   |

| Small-Signal Response, G = 1000                           | Figure 7-32   |

| Overshoot vs Capacitive Loads                             | Figure 7-33   |

| Large-Signal Step Response                                | Figure 7-34   |

| Settling Time vs Step Size                                | Figure 7-35   |

| Large-Signal Frequency Response                           | Figure 7-36   |

| Closed-Loop Output Impedance vs Frequency                 | Figure 7-37   |

# 7.6 Typical Characteristics

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

# Table 7-1. Table of Graphs (continued)

| FIGURE TITLE                                                                                          | FIGURE NUMBER |

|-------------------------------------------------------------------------------------------------------|---------------|

| Input and Output Voltage Graphs                                                                       | '             |

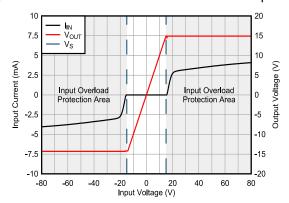

| Input Current vs Input Overvoltage                                                                    | Figure 7-38   |

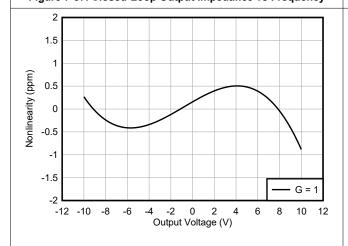

| Gain Nonlinearity, G = 1                                                                              | Figure 7-39   |

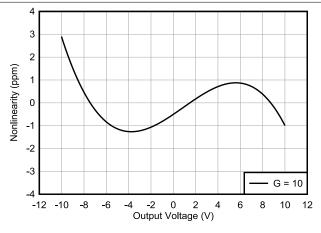

| Gain Nonlinearity, G = 10                                                                             | Figure 7-40   |

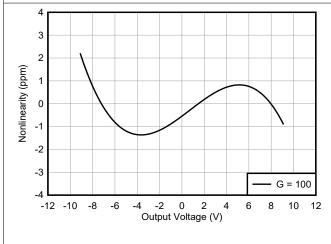

| Gain Nonlinearity, G = 100                                                                            | Figure 7-41   |

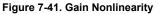

| Gain Nonlinearity, G = 1000                                                                           | Figure 7-42   |

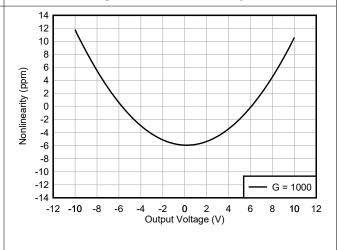

| Positive Input Bias Current vs Common-Mode Voltage (V <sub>S</sub> _)                                 | Figure 7-43   |

| Positive Input Bias Current vs Common-Mode Voltage (V <sub>S+</sub> )                                 | Figure 7-44   |

| Negative Input Bias Current vs Common-Mode Voltage (V <sub>S</sub> _)                                 | Figure 7-45   |

| Negative Input Bias Current vs Common-Mode Voltage (V <sub>S+</sub> )                                 | Figure 7-46   |

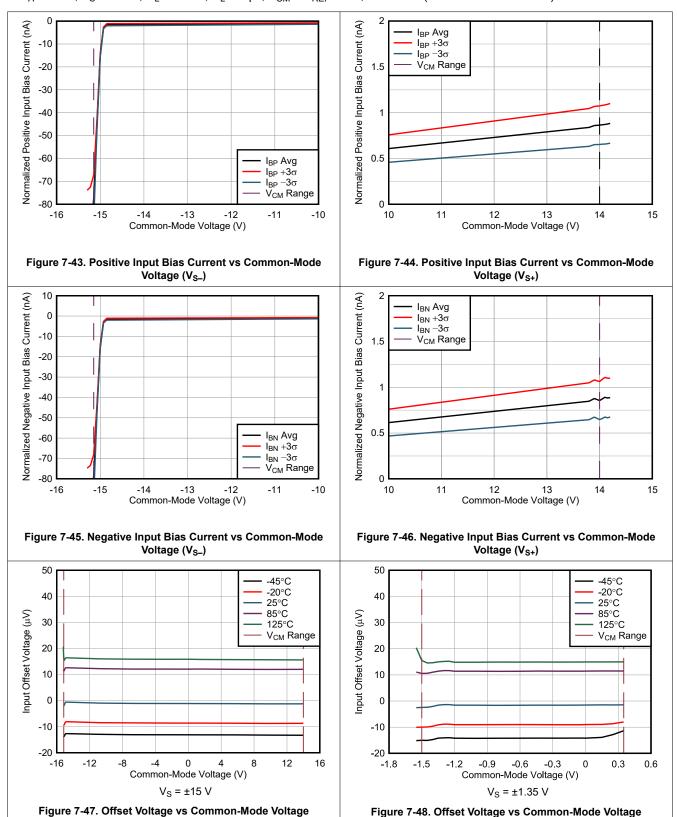

| Offset Voltage vs Common-Mode Voltage, V <sub>S</sub> = 30 V                                          | Figure 7-47   |

| Offset Voltage vs Common-Mode Voltage, V <sub>S</sub> = 2.7 V                                         | Figure 7-48   |

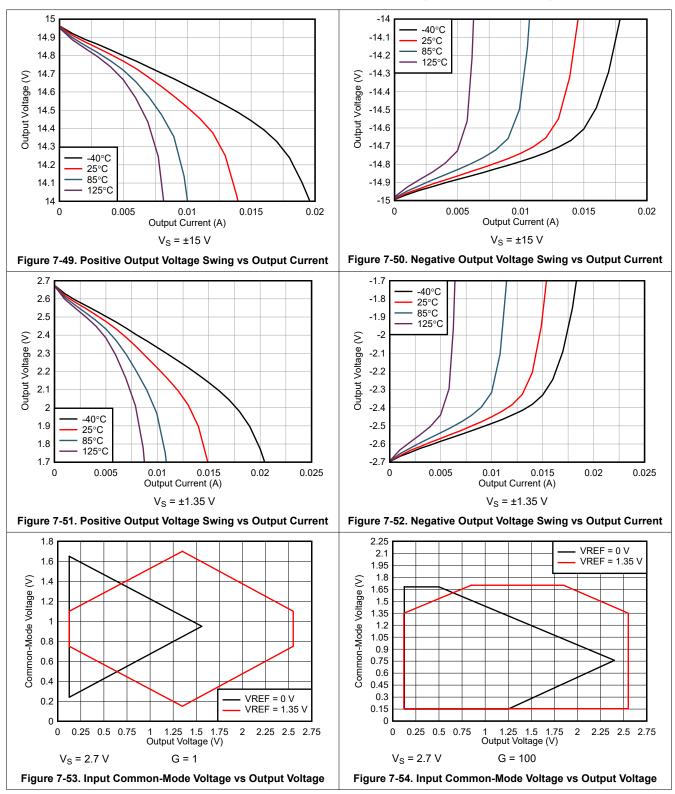

| Positive Output Voltage Swing vs Output Current, V <sub>S</sub> = 30 V                                | Figure 7-49   |

| Negative Output Voltage Swing vs Output Current, V <sub>S</sub> = 30 V                                | Figure 7-50   |

| Positive Output Voltage Swing vs Output Current, V <sub>S</sub> = 2.7 V                               | Figure 7-51   |

| Negative Output Voltage Swing vs Output Current, V <sub>S</sub> = 2.7 V                               | Figure 7-52   |

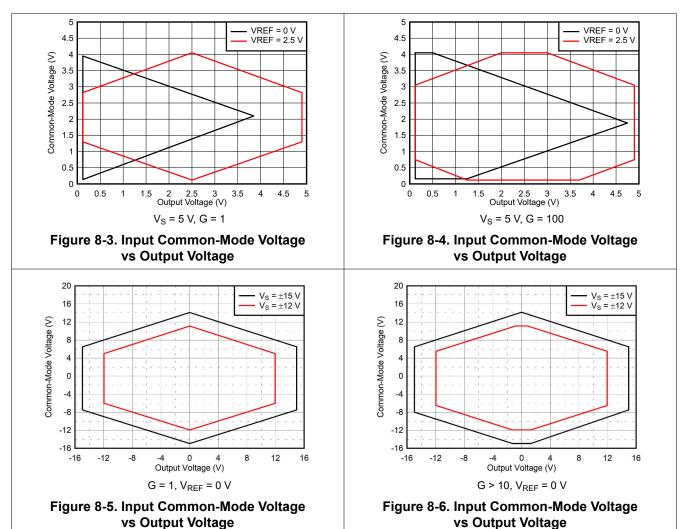

| Input Common-Mode Voltage vs Output Voltage, V <sub>S</sub> = 2.7 V, G = 1                            | Figure 7-53   |

| Input Common-Mode Voltage vs Output Voltage, V <sub>S</sub> = 2.7 V, G = 1                            | Figure 7-54   |

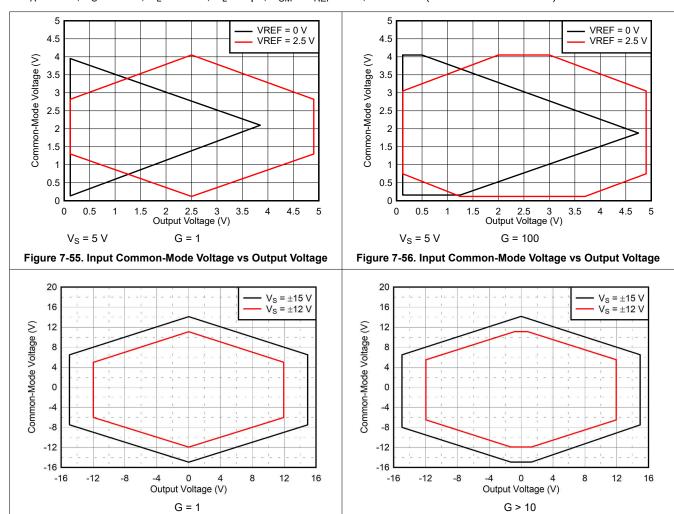

| Input Common-Mode Voltage vs Output Voltage, V <sub>S</sub> = 5 V, G = 1                              | Figure 7-55   |

| Input Common-Mode Voltage vs Output Voltage, V <sub>S</sub> = 5 V, G = 100                            | Figure 7-56   |

| Input Common-Mode Voltage vs Output Voltage, $V_S$ = 24 V and $V_S$ = 30 V, G = 1                     | Figure 7-57   |

| Input Common-Mode Voltage vs Output Voltage, $V_S = 24 \text{ V}$ and $V_S = 30 \text{ V}$ , $G = 10$ | Figure 7-58   |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

#### 7.6 Typical Characteristics

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

Figure 7-1. Typical Distribution of Input Stage Offset Voltage

N = 30 Mean =  $-0.024 \,\mu\text{V/°C}$  Std Dev =  $0.177 \,\mu\text{V//°C}$

Figure 7-3. Typical Distribution of Output Stage Offset Voltage

Figure 7-4. Typical Distribution of Output Stage Offset Voltage Drift

Figure 7-5. Typical Distribution of Inverting Input Bias Current

Figure 7-6. Typical Distribution of Noninverting Input Bias Current

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

Figure 7-11. Input Stage Offset Voltage vs Temperature

Figure 7-12. Output Stage Offset Voltage vs Temperature

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

Figure 7-25. Voltage Noise Spectral Density vs Frequency (RTI)

Figure 7-27. 0.1-Hz to 10-Hz RTI Voltage Noise

Figure 7-28. 0.1-Hz to 10-Hz RTI Voltage Noise

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

Figure 7-37. Closed-Loop Output Impedance vs Frequency

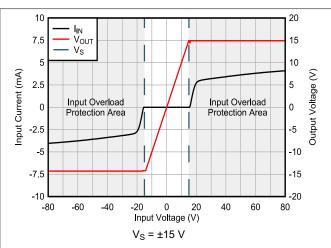

Figure 7-38. Input Current vs Input Overvoltage

Figure 7-39. Gain Nonlinearity

Figure 7-40. Gain Nonlinearity

Figure 7-42. Gain Nonlinearity

at  $T_A$  = 25°C,  $V_S$  = ±15 V,  $R_L$  = 10 k $\Omega$ ,  $C_L$  = 0 pF,  $V_{CM}$  =  $V_{REF}$  = 0 V, and G = 1 (unless otherwise noted)

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

at  $T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ ,  $C_L = 0$  pF,  $V_{CM} = V_{REF} = 0$  V, and G = 1 (unless otherwise noted)

Figure 7-57. Input Common-Mode Voltage vs Output Voltage

Figure 7-58. Input Common-Mode Voltage vs Output Voltage

# 8 Detailed Description

#### 8.1 Overview

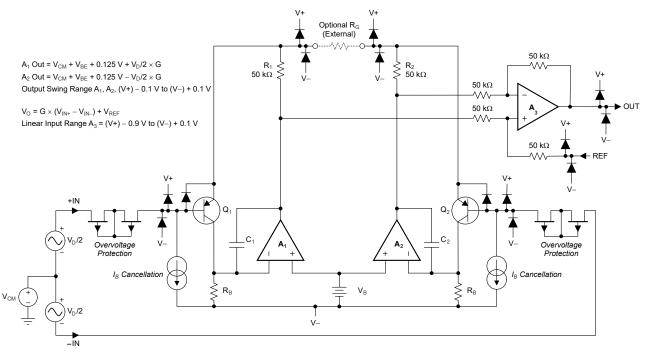

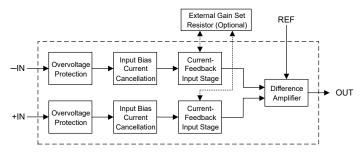

The INA823 is a monolithic precision instrumentation amplifier that incorporates a current-feedback input stage and a four-resistor difference-amplifier output stage. One of the features of an instrumentation amplifier (IA) is that the gain is set by placing an external resistor across the RG pins, as described in Section 8.3.1. The three-op-amp IA topology in the INA823 limits the maximum input voltage applied to the input terminal. The maximum input voltage depends on the common-mode voltage, differential voltage, gain, and the reference voltage; for more information, see Section 8.3.2. The INA823 also features protection at each input by two junction field-effect transistors (JFETs) that provide a low series resistance under normal signal conditions, and preserve excellent noise performance. When excessive voltage is applied, these transistors limit the input current, as described in Section 8.3.3.

The INA823 is developed for medical-sector applications such as infusion pumps (see Section 9.2.1), and industrial applications such as programmable logic controllers (see Section 9.2.2)

The schematic in Figure 8-1 shows how the INA823 operates. A differential input voltage is buffered by the input transistors,  $Q_1$  and  $Q_2$ , and is forced across  $R_G$ . This causes a signal current through  $R_G$ ,  $R_1$ , and  $R_2$ . The output difference amplifier,  $A_3$ , removes the common-mode component of the input signal and refers the output signal to the REF pin. The threshold voltage of  $Q_1$  and  $Q_2$  (defined as  $V_{BE}$ ) along with the voltage drop across  $R_1$  and  $R_2$  produce output voltages on  $R_1$  and  $R_2$ , respectively, that are approximately 0.8 V less than the input voltages.

Figure 8-1. Detailed Schematic

#### 8.2 Functional Block Diagram

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

#### 8.3 Feature Description

#### 8.3.1 Gain-Setting Function

Figure 8-2 shows that the gain of the INA823 is set by a single external resistor ( $R_G$ ) connected between the RG pins (pins 1 and 8).

Figure 8-2. Simplified Schematic of the INA823 With Gain and Output Equations

The gain of the INA823 can be calculated with Equation 1:

$$G = 1 + \frac{100 \text{ k}\Omega}{R_G} \tag{1}$$

The value of the external gain resistor R<sub>G</sub> is then derived from the gain equation:

$$R_{G} = \frac{100 \text{ k}\Omega}{G - 1} \tag{2}$$

Table 8-1 lists several commonly used gains and resistor values. The  $100\text{-k}\Omega$  term in Equation 1 is a result of the sum of the two internal  $50\text{-k}\Omega$  feedback resistors. These on-chip resistors are laser-trimmed to accurate absolute values. The accuracy and temperature coefficients of these resistors are included in the gain accuracy and drift specifications of the Section 7.5. As shown in Figure 8-2 and explained in more details in Section 11, make sure to connect low-ESR,  $0.1\text{-}\mu\text{F}$  ceramic bypass capacitors between each supply pin and ground that are placed as close to the device as possible.

Table 8-1. Commonly Used Gains and Resistor Values

| DESIRED GAIN | NEAREST 1% R <sub>G</sub> (Ω) | CALCULATED GAIN ERROR (%) |

|--------------|-------------------------------|---------------------------|

| 1            | Not connected                 | Not connected             |

| 2            | 100 k                         | 0                         |

| 5            | 24.9 k                        | 0.321                     |

| 10           | 11 k                          | 0.909                     |

| 20           | 5.23 k                        | 0.602                     |

| 33           | 3.09 k                        | 1.098                     |

| 50           | 2.05 k                        | 0.439                     |

| 65           | 1.58 k                        | 1.091                     |

| 100          | 1.02 k                        | 0.961                     |

| 200          | 499                           | 0.700                     |

| 500          | 200                           | 0.200                     |

| 1000         | 100                           | 0.100                     |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

#### 8.3.1.1 Gain Drift

The stability and temperature drift of the external gain setting resistor ( $R_G$ ) also affects gain. The contribution of  $R_G$  to gain accuracy and drift is determined from Equation 2.

The best gain drift of 5 ppm/°C (maximum) is achieved when the INA823 uses G = 1 V/V without  $R_G$  connected. In this case, gain drift is limited by the slight mismatch of the temperature coefficient of the integrated 50-k $\Omega$  resistors in the differential amplifier (A<sub>3</sub>).

At gains greater than 1 V/V, gain drift increases as a result of the individual drift of the 50-k $\Omega$  resistors in the feedback of  $A_1$  and  $A_2$  relative to the drift of the external gain resistor ( $R_G$ .) The low temperature coefficient of the internal feedback resistors significantly improves the overall temperature stability of applications using gains greater than 1 V/V over alternate options.

#### 8.3.2 Input Common-Mode Voltage Range

The INA823 linear input voltage range extends from 1 V less than the positive supply to 0.15 V less than the negative supply, and maintains excellent common-mode rejection throughout this range. The common-mode range for the most common operating conditions are shown in Figure 8-3. While there are other methods to calculate the common-mode voltage range, the suggested tool is the Analog Engineers Calculator.

A single-supply instrumentation amplifier has special design considerations. To achieve a common-mode range that extends to single-supply ground, the INA823 employs a current-feedback topology with PNP input

transistors. The matched PNP transistors, Q1 and Q2, shift the input voltages of both inputs up by a diode drop, and (through the feedback network) shift the output of A1 and A2 by approximately 0.6 V. The output of A1 and A2 is well within the linear range when the inputs are within the single-supply ground. When inputs are within the supply ground, differential measurements can be made at the ground level. As a result of this input level-shifting, the voltages at pin 1 and pin 8 are not equal to the respective input pin voltages. For most applications, this inequality is not important because only the gain-setting resistor connects to these pins.

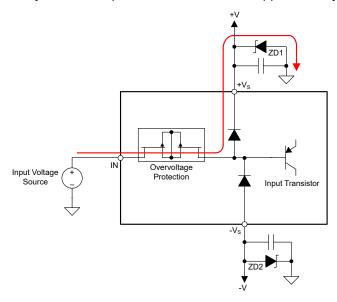

#### 8.3.3 Input Protection

The inputs of the INA823 device are individually protected for voltages up to  $\pm 60$  V and for short transients up to  $\pm 80$  V. For example, a condition of -60 V on one input and  $\pm 60$  V on the other input does not cause damage. Internal circuitry on each input provides low series impedance under normal signal conditions. If the input is overloaded, the protection circuitry limits the input current to a value of approximately 4 mA.

Figure 8-7. Input Current Path During an Overvoltage Condition

During an input overvoltage condition, current flows through the input protection diodes into the power supplies, as shown in Figure 8-7. If the power supplies are unable to sink current, then Zener diode clamps (ZD1 and ZD2 in Figure 8-7) must be placed on the power supplies to provide a current pathway to ground. Figure 8-8 shows the input current for input voltages from -80 V to +80 V when the INA823 is powered by  $\pm 15 \text{-V}$  supplies.

Figure 8-8. Input Current vs Input Overvoltage

#### 8.4 Device Functional Modes

The INA823 has a single functional mode and is operational when the power supply voltage is greater than 2.7 V  $(\pm 1.35 \text{ V})$ . The maximum power-supply voltage for the INA823 is 36 V  $(\pm 18 \text{ V})$ .

Product Folder Links: INA823

# 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 9.1 Application Information

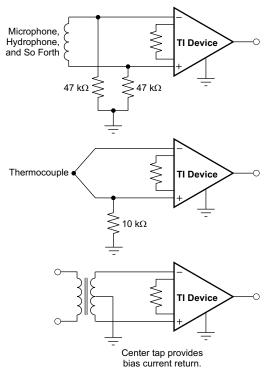

#### 9.1.1 Input Bias Current Return Path

The input impedance of the INA823 is extremely high, but a path must be provided for the input bias current of both inputs. This input bias current is typically 1.2 nA. High input impedance means that this input bias current changes little with varying input voltage.

For proper operation, input circuitry must provide a path for this input bias current. Figure 9-1 shows various provisions for an input bias current path. Without a bias current path, the inputs float to a potential that exceeds the common-mode range of the INA823, and the input amplifiers saturate. If the differential source resistance is low, the bias current return path connects to one input (as shown in the thermocouple example in Figure 9-1). With a higher source impedance, use two equal resistors to provide a balanced input, with the possible advantages of a lower input offset voltage as a result of bias current, and better high-frequency common-mode rejection. Furthermore, matched input impedances generally minimize the impact to performance in cases where the input common-mode voltage is very low and input bias current can increase as the I<sub>B</sub> cancellation circuity runs out of headroom. The input offset current typically remains low; therefore, well-matched input impedances reduce the differential error voltage that would otherwise arise.

For more details about why a valid input bias current return path is necessary, see the *Importance of Input Bias Current Return Paths in Instrumentation Amplifier Applications* application note.

Copyright © 2017, Texas Instruments Incorporated

Figure 9-1. Providing an Input Common-Mode Current Path

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

#### 9.2 Typical Applications

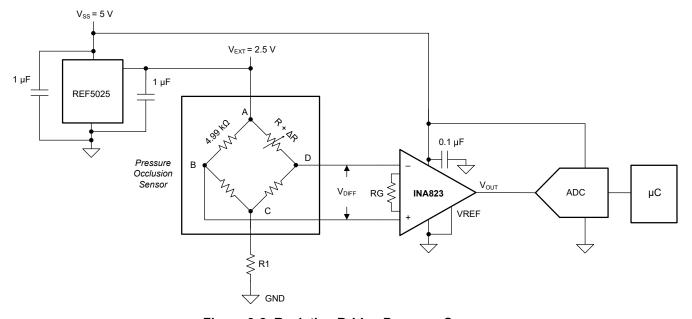

#### 9.2.1 Resistive-Bridge Pressure Sensor

The INA823 is an integrated instrumentation amplifier that measures small differential voltages while simultaneously rejecting larger common-mode voltages. The device offers a low power consumption of 250 µA (max) and high precision, thus minimizing errors with voltage offset, offset drift and gain error.

The device is designed for portable applications where sensors measure physical parameters, such as changes in fluid, pressure, temperature, or humidity. An example of a pressure sensor used in the medical sector is in portable infusion pumps or dialysis machines.

The pressure sensor is made of a piezo-resistive element that can be derived as a classical 4-resistor Wheatstone bridge. Occlusion (infusion of fluids, medication, or nutrients) happens only in one direction, and therefore, can only cause the resistive element (R) to expand. This expansion causes a change in voltage on one leg of the Wheatstone bridge, which induces a differential voltage  $V_{\text{DIFF}}$ .

Figure 9-2 showcases an exemplary circuit for an occlusion pressure sensor application, as required in infusion pumps. When blockage (occlusion) occurs against a set-point value, the tubing depresses, thus causing the piezo-resistive element to expand (Node AD:  $R + \Delta R$ ). The signal chain connected to the bridge downstream processes the pressure change and can trigger an alarm.

Figure 9-2. Resistive-Bridge Pressure Sensor

Low-tolerance bridge resistors must be used to minimize the offset and gain errors.

Given that there is only a positive differential voltage applied, this circuit is laid out in single-ended supply mode. The excitation voltage,  $V_{\text{EXT}}$ , to the bridge must be precise and stable; otherwise, measurement error is introduced.

The REF5025 is a low-noise, low-drift (3 ppm/C), and high-precision (0.05%) voltage reference that is an excellent option to generate the excitation voltage  $V_{\text{EXT}}$ .

The following subsections give the design requirements and detailed design procedure for an application with a occlusion pressure sensor.

For more information and design tips to consider when using a resistive-bride pressure sensor, see the *Design* tips for a resistive-bridge pressure sensor in industrial process-control systems analog applications journal.

#### 9.2.1.1 Design Requirements

For this application, the design requirements are as shown in Table 9-1.

| Table 9-1. Do | esign Red | uirements |

|---------------|-----------|-----------|

|---------------|-----------|-----------|

| DESCRIPTION                      | VALUE                                            |

|----------------------------------|--------------------------------------------------|

| Single supply voltage            | V <sub>S</sub> = 5 V                             |

| Excitation voltage               | V <sub>EXT</sub> = 2.5 V                         |

| Occlusion pressure range         | P = 110 psi, increments of p = 0.5 psi           |

| Occlusion pressure sensitivity   | S = 2 ± 0.5 (25%) mV/V/psi                       |

| Occlusion pressure impedance (R) | $R = 4.99 \text{ k}\Omega \pm 50 \Omega (0.1\%)$ |

| Total pressure sampling rate     | Sr = 20 Hz                                       |

| Full-scale range of ADC          | V <sub>ADC(fs)</sub> = V <sub>OUT</sub> = 4.5 V  |

#### 9.2.1.2 Detailed Design Procedure

This section provides basic calculations to lay out the instrumentation amplifier with respect to the given design requirements.

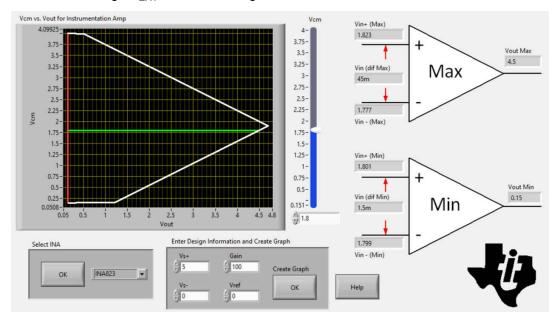

One of the key considerations in resistive-bridge sensors is the common-mode voltage,  $V_{CM}$ . If the bridge is balanced (no pressure, thus no voltage change),  $V_{CM(MAX)}$  is half of the bridge excitation ( $V_{EXT}$ ). As the pressure increases to the maximum value, the common-mode voltage decreases to  $V_{CM(MIN)}$ .

To achieve the output voltage of  $V_{OUT}$  = 4.5 V with the INA823, the limitation for the common-mode voltage is at  $V_{CM(INA823max)}$  = 1.8 V, as shown in Figure 7-56 and Figure 9-3 (where an initial gain value of 100 V/V is used as an approximation). An additional series resistor in the Wheatstone bridge string (R1) is required to shift the common-mode voltage to this value. However, be aware that shifting the common-mode voltage also changes the effective excitation voltage  $V_{EXT}$  across the bridge.

Figure 9-3. Screen Shot From Analog Engineer's Calculator

Calculate the new effective excitation voltage  $V_{\text{EXT(NOM)}}$  associated with a desired  $V_{\text{CM(MIN)}}$  value by solving the following:

$$V_{\text{EXT(NOM)}} = 2* \left( \frac{V_{\text{EXT}} - V_{\text{CM(MIN)}}}{1 + S_{\text{MAX}} * P_{\text{MAX}}} \right) = 2* \left( \frac{2.5 - 1.8}{1 + 2.5 \text{ mV/}_{\text{V*psi}} * 10 \text{ psi}} \right) = 1.366 \text{ V}$$

(3)

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

V<sub>EXT(NOM)</sub> can in turn be used to calculate the desired value of R1:

$$R_1 = R\left(\frac{V_{EXT}}{V_{EXT(NOM)}} - 1\right) = 4.99 \text{ k}\Omega\left(\frac{2.5 \text{ V}}{1.366 \text{ V}} - 1\right) = 4.144 \text{ k}\Omega$$

(4)

Use a standard 0.1% resistor value of 4.12 k $\Omega$ .

Calculate the maximum value of  $V_{\text{DIFF}}$  by solving the following equation for the maximum pressure of 10 psi:

$$V_{DIFF} = (S_{MAX} * P_{MAX}) * V_{EXT(NOM)} = (2.5 \text{ mV/} V_{psi} * 10 \text{ psi}) * 1.366 \text{ V} = 34.15 \text{ mV}$$

(5)

Use the resulting value to verify that the minimum bridge common-mode voltage,  $V_{CM(MIN)}$ , is within the limits of the INA823 by solving the following:

$$V_{CM(MAX)} = V_{CM(MIN)} + \frac{V_{DIFF}}{2} = 1.8 \text{ V} + \frac{34.15 \text{ mV}}{2} = 1.817 \text{ V}$$

(6)

Next, use Equation 7 to calculate the required gain for the given maximum sensor output voltage span,  $V_{DIFF}$ , with respect to the required  $V_{OIJT}$ , which is the full-scale range of the ADC.

$$G = \frac{V_{OUT}}{V_{DIFF(MAX)}} = \frac{4.5 \text{ V}}{34.15 \text{ mV}} = 131.77 \text{ V/V}$$

(7)

Equation 8 calculates the gain-setting resistor value using the INA823 gain equation shown in Equation 2:

$$R_{G} = \frac{100 \text{ k}\Omega}{G - 1} = \frac{100 \text{ k}\Omega}{131.77 \text{ V/V} - 1} = 764.69 \Omega$$

(8)

Use a standard 0.1% resistor value of 768  $\Omega$ , so as not to exceed the full-scale range of the ADC.

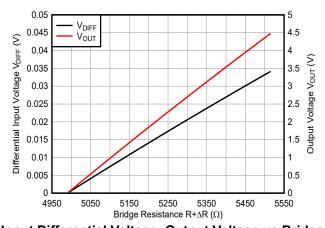

## 9.2.1.3 Application Curves

The following typical characteristic curve is for the circuit in Figure 9-2.

Figure 9-4. Input Differential Voltage, Output Voltage vs Bridge Resistance

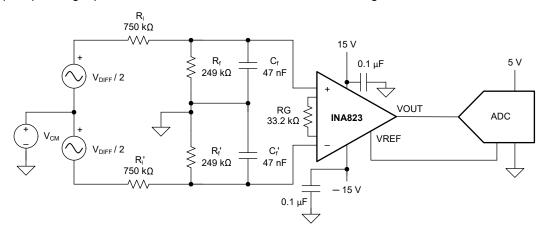

### 9.2.2 Supporting High Common-Mode Voltage in PLC Input Modules

Figure 9-5 showcases a high common-mode voltage circuit that is commonly required for programmable logic controller (PLC) analog input modules. This circuit uses a resistive scaling network in front of the IA.

Figure 9-5. High Common-Mode Voltage PLC Input Module

For a detailed description of the passive scaling approach and more, see the *Supporting High-Voltage Common Mode Using Instrumentation Amplifier* application brief.

#### 9.2.2.1 Design Requirements

Table 9-2 lists the requirements for this design example.

|                                          | - 5           |

|------------------------------------------|---------------|

| PARAMETER                                | VALUE         |

| Supply voltage                           | ±15 V         |

| Common-mode voltage                      | +36 V / –43 V |

| Input differential signal                | 1 V           |

| Gain V <sub>OUT</sub> /V <sub>DIFF</sub> | 1 V/V         |

| Minimum dc CMRR                          | 65 dB         |

**Table 9-2. Design Parameters**

#### 9.2.2.2 Detailed Design Procedure

The gain of the IA is calculated so that the circuit operates at unity gain, where  $V_{OUT} = V_{DIFF}$ .

The single-ended input impedance,  $R_{in}(SE)$ , of the circuit is the sum of the scaling resistors ( $R_f + R_i$ ). To minimize the error that is caused by the tolerance of the scaling resistors, keep  $R_{in} > 1 \text{ M}\Omega$ .

Ideally, choose the resistors so that Rf / Ri = Rf' / Ri'. In the real world, designers have to trade off between the mismatch of ratios that degrades the common-mode rejection ratio (CMRR) and the acceptable cost for the design.

The following text describe how to estimate the CMRR performance of the external resistor scaling approach. In the calculation of CMRR, the following factors are considered:

- Take into account the number of resistors, which is estimated by  $\sqrt{n}$ , where n is the number of resistors applied. In this case, this estimation results in a factor of 2.

- ΔR / R is the resistor matching ratio. The resistor tolerance for all four resistors is 0.1%.

- Take into account that a normal production distribution of the resistor value with a standard deviation of  $\pm 3 \sigma$  (99.7%). In this case, the assumption results in a factor  $\sigma = 1/3 = 0.33$  into the equation.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

Equation 9 calculates the common-mode rejection ratio with given factors:

$$CMRR_{dB} = \frac{G1 + 1}{\alpha \cdot \frac{\Delta R}{R} \cdot \sqrt{n}}$$

(9)

$$CMRR_{dB} = \frac{0.25 + 1}{0.33 \cdot 0.1\% \cdot \sqrt{4}} = 65.5 \text{ dB}$$

(10)

The scaling ratio G1 is calculated by:

$$G1 = \frac{R_{f}}{R_{f} + R_{i}} \tag{11}$$

where

- R<sub>f</sub> is variable

- R<sub>i</sub> is fixed at 750 kΩ.

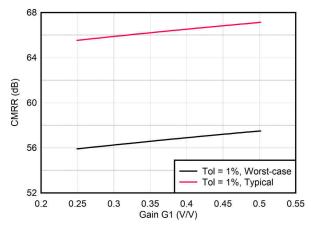

Figure 9-6 shows a comparison between the CMRR performance at worst-case ( $\alpha$  neglected) and considering normal distribution for different gain settings of G1.

For more details about the calculation of CMRR, see the *Difference amplifier (subtractor) circuit* analog engineer's circuit.

### 9.2.2.3 Application Curves

Figure 9-6. Common-mode Rejection Ratio of External Resistor Network for Different Scaling Ratios

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 10 Power Supply Recommendations

The nominal performance of the INA823 is specified with a supply voltage of ±15 V and midsupply reference voltage. The device also operates using power supplies from ±1.35 V (2.7 V) to ±18 V (36 V) and non-midsupply reference voltages with excellent performance. Parameters that can vary significantly with operating voltage and reference voltage are shown in *Section 7.6*.

#### CAUTION

Supply voltages higher than 40 V (±20 V) can permanently damage the device.

# 11 Layout

#### 11.1 Layout Guidelines

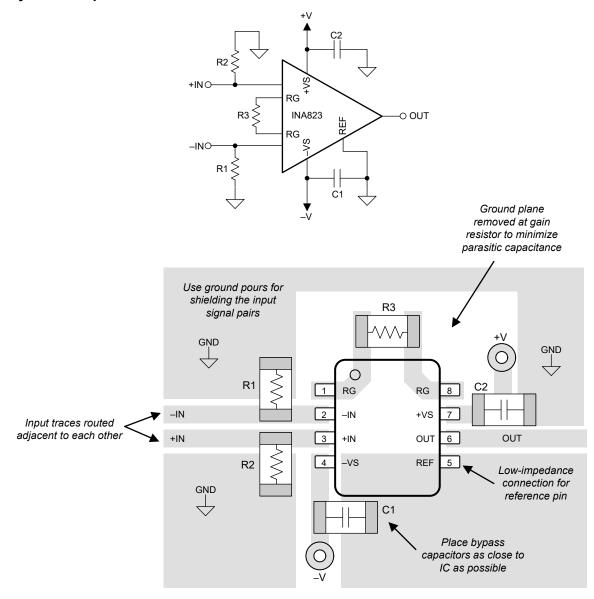

Attention to good layout practices is always recommended. For best operational performance of the device, use the following PCB layout practices:

- Make sure that both input paths are well-matched for source impedance and capacitance to avoid converting common-mode signals into differential signals.

- Use bypass capacitors to reduce the coupled noise by providing low-impedance power sources local to the analog circuitry.

- Connect low-ESR, 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for singlesupply applications.

- Route the input traces as far away from the supply or output traces as possible to reduce parasitic coupling. If

these traces cannot be kept separate, crossing the sensitive trace perpendicular is much better than crossing

in parallel with the noisy trace.

- Place the external components as close to the device as possible.

- Use short, symmetric, and wide traces to connect the external gain resistor to minimize capacitance mismatch between the RG pins.

- Keep the traces as short as possible.

# 11.2 Layout Example

Figure 11-1. Example Schematic and Associated PCB Layout

# 12 Device and Documentation Support

# 12.1 Device Support

#### 12.1.1 Development Support

- SPICE-based analog simulation program TINA-TI software folder

- Analog Engineer's Calculator

#### 12.1.1.1 PSpice® for TI

PSpice<sup>®</sup> for TI is a design and simulation environment that helps evaluate performance of analog circuits. Create subsystem designs and prototype solutions before committing to layout and fabrication, reducing development cost and time to market.

#### 12.2 Documentation Support

#### 12.2.1 Related Documentation

For related documentation see the following:

- Texas Instruments, Comprehensive Error Calculation for Instrumentation Amplifiers application note

- Texas Instruments, Importance of Input Bias Current Return Paths in Instrumentation Amplifier Applications application note

- Texas Instruments, REF50xx Low-Noise, Very Low Drift, Precision Voltage Reference data sheet

- Texas Instruments, OPAx191 36-V, Low Power, Precision, CMOS, Rail-to-Rail Input/Output, Low Offset Voltage, Low Input Bias Current Op Amp data sheet

#### 12.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.5 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

#### 12.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.7 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

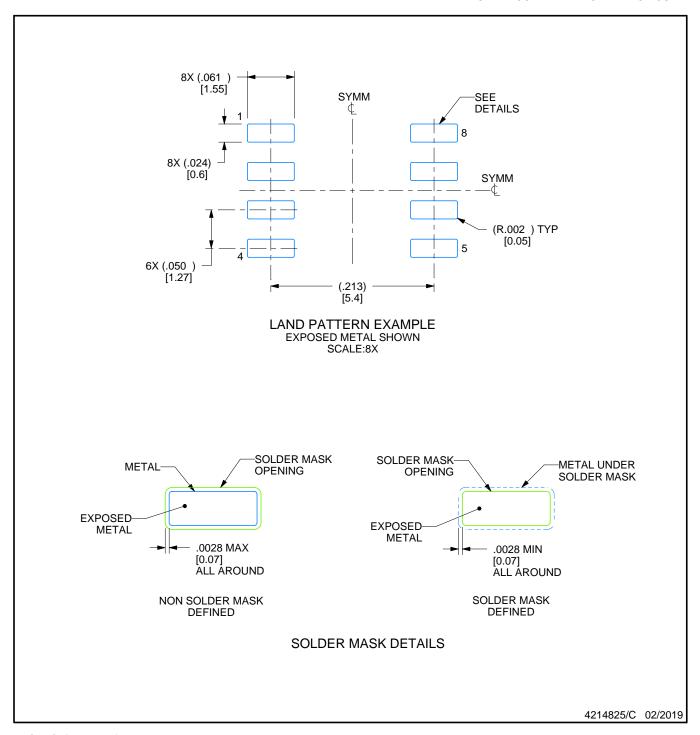

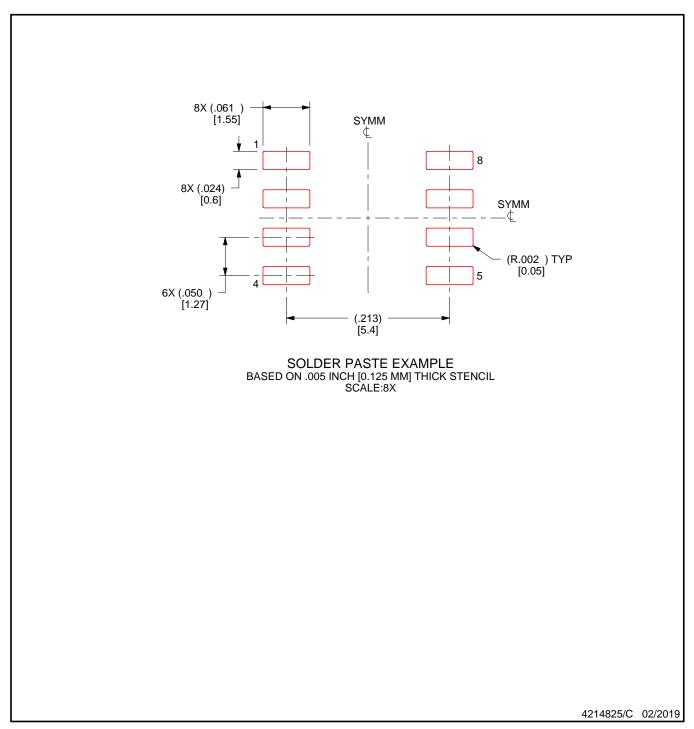

#### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2021 Texas Instruments Incorporated

www.ti.com 25-Jun-2022

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |               |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| INA823DGKR       | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 2IVJ                 | Samples |

| INA823DGKT       | ACTIVE        | VSSOP        | DGK                | 8    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 2IVJ                 | Samples |

| INA823DR         | ACTIVE        | SOIC         | D                  | 8    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | INA823               | Samples |

| INA823DT         | ACTIVE        | SOIC         | D                  | 8    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | INA823               | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

# PACKAGE OPTION ADDENDUM

www.ti.com 25-Jun-2022

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

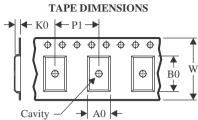

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

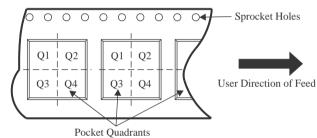

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| INA823DGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA823DGKT | VSSOP           | DGK                | 8 | 250  | 180.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA823DR   | SOIC            | D                  | 8 | 3000 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA823DT   | SOIC            | D                  | 8 | 250  | 180.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 3-Jun-2022

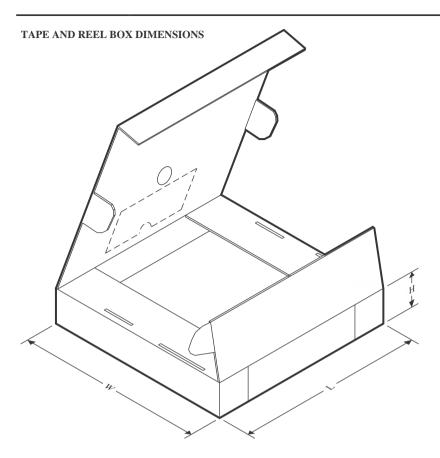

#### \*All dimensions are nominal

| 7 till dillitoriolorio di o riorrillia |              |                 |      |      |             |            |             |

|----------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                                 | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| INA823DGKR                             | VSSOP        | DGK             | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| INA823DGKT                             | VSSOP        | DGK             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| INA823DR                               | SOIC         | D               | 8    | 3000 | 356.0       | 356.0      | 35.0        |

| INA823DT                               | SOIC         | D               | 8    | 250  | 210.0       | 185.0      | 35.0        |

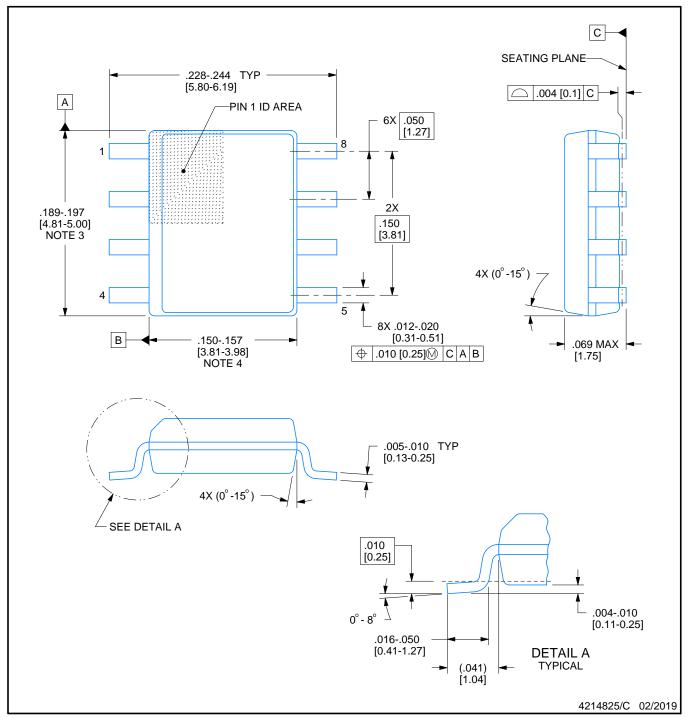

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.