LM3429, LM3429-Q1

SNVS616H - APRIL 2009-REVISED JULY 2015

# LM3429/-Q1 N-Channel Controller for Constant Current LED Drivers

#### **Features**

- LM3429-Q1 is AEC-Q100 Grade 1 Qualified for **Automotive Applications**

- V<sub>IN</sub> Range From 4.5 V to 75 V

- Adjustable Current Sense Voltage

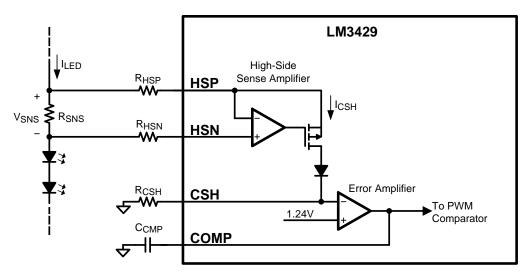

- High-Side Current Sensing

- 2-Ω, 1-A Peak MosFET Gate Driver

- Input Undervoltage Protection

- Overvoltage Protection

- **PWM Dimming**

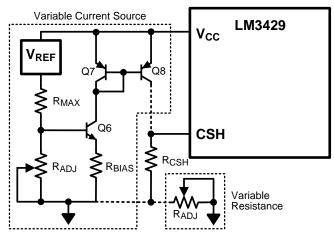

- **Analog Dimming**

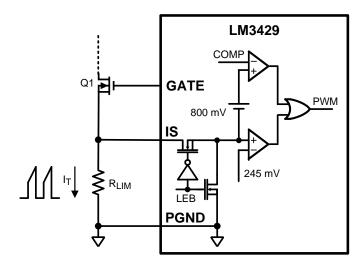

- Cycle-by-Cycle Current Limit

- Programmable Switching Frequency

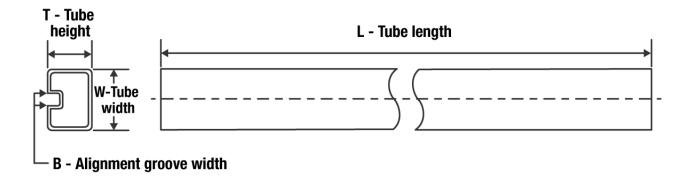

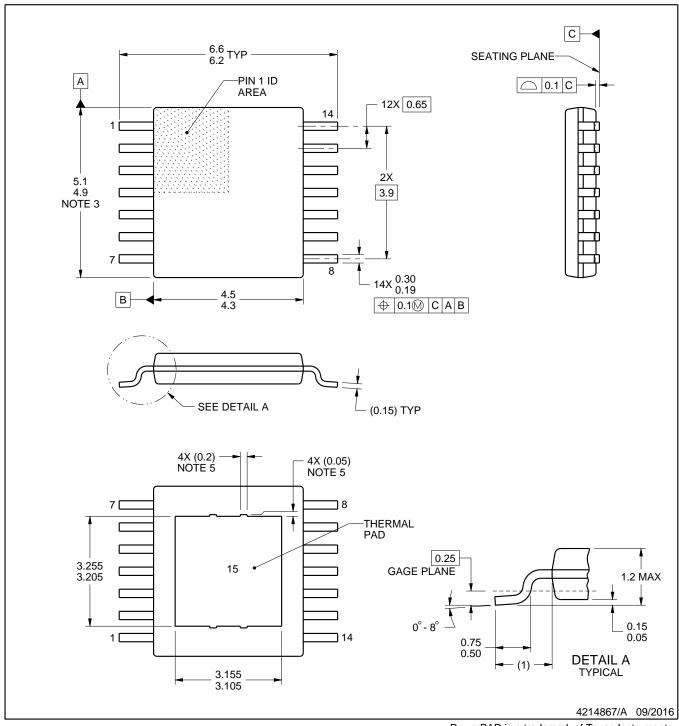

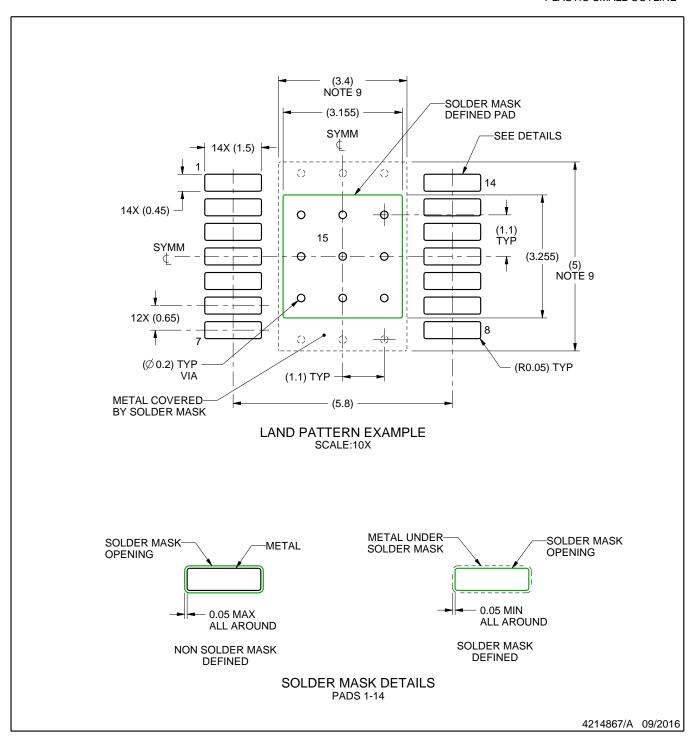

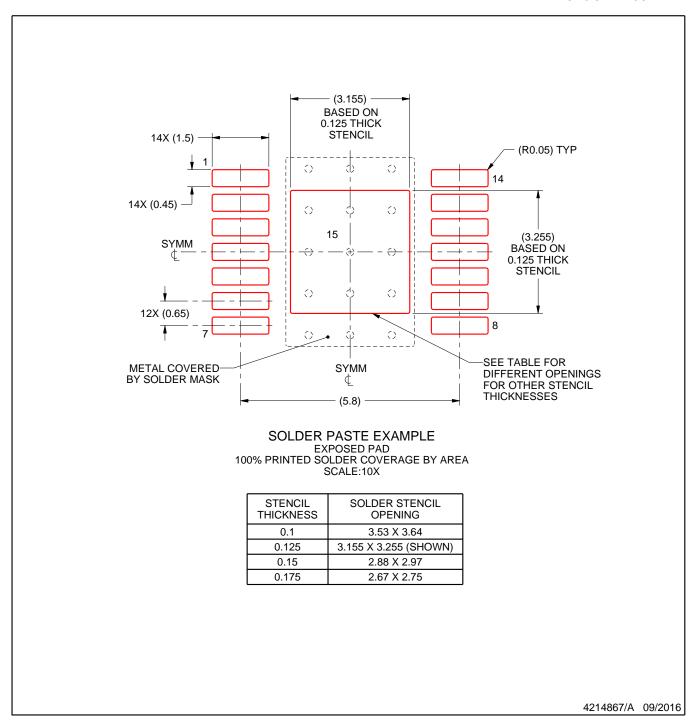

- Low Profile 14-lead HTSSOP Package

- Thermal Shutdown

# **Applications**

- LED Drivers Buck, Boost, Buck-Boost, SEPIC

- Indoor and Outdoor SSL

- Automotive

- General Illumination

- Constant-Current Regulators

# 3 Description

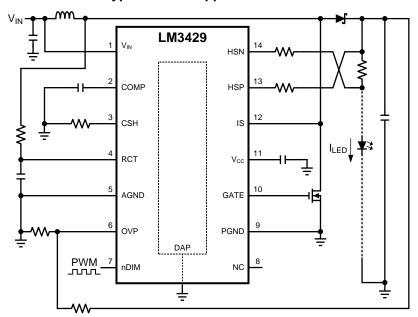

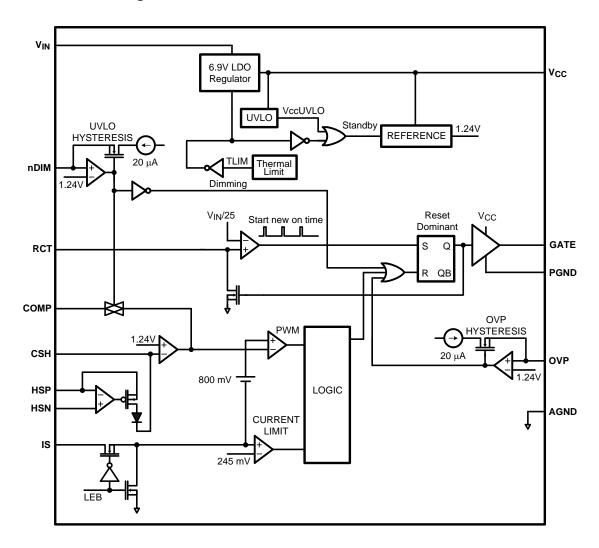

The LM3429 is a versatile high voltage N-channel MosFET controller for LED drivers. It can be easily configured in buck, boost, buck-boost and SEPIC topologies. This flexibility, along with an input voltage rating of 75V, makes the LM3429 ideal for illuminating LEDs in a very diverse, large family of applications.

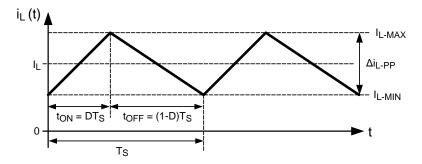

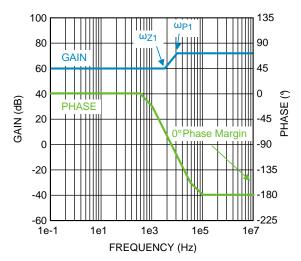

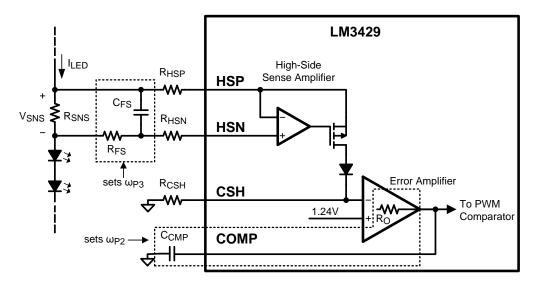

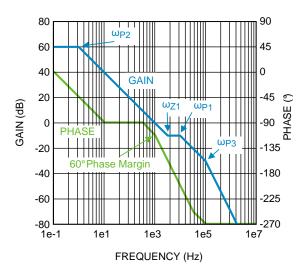

Adjustable high-side current sense voltage allows for tight regulation of the LED current with the highest efficiency possible. The LM3429 uses Predictive Offtime (PRO) control, which is a combination of peak current-mode control and a predictive off-timer. This method of control eases the design of loop compensation while providing inherent input voltage feed-forward compensation.

The LM3429 includes a high-voltage startup regulator that operates over a wide input range of 4.5 V to 75 V. The internal PWM controller is designed for adjustable switching frequencies of up to 2 MHz, thus enabling compact solutions. Additional features include analog dimming, PWM dimming, overvoltage protection, undervoltage lock-out, cycle-by-cycle current limit, and thermal shutdown.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |

|-------------|-------------|-------------------|--|

| LM3429      | HTCCOD (14) | 5.00 mm v 4.40 mm |  |

| LM3429-Q1   | HTSSOP (14) | 5.00 mm × 4.40 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

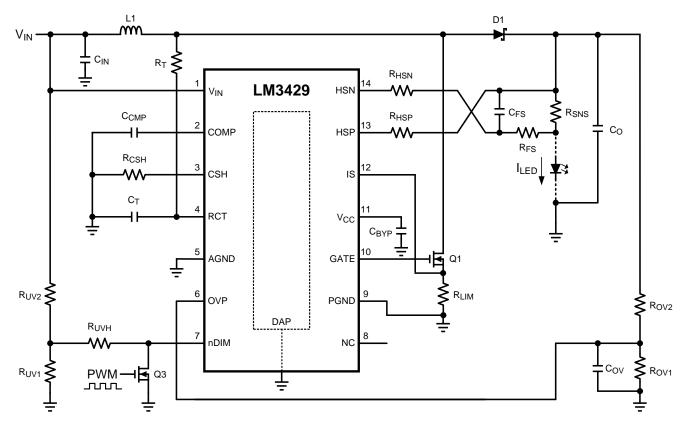

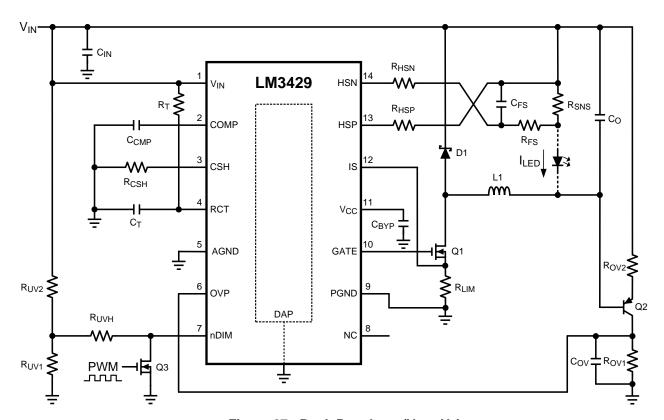

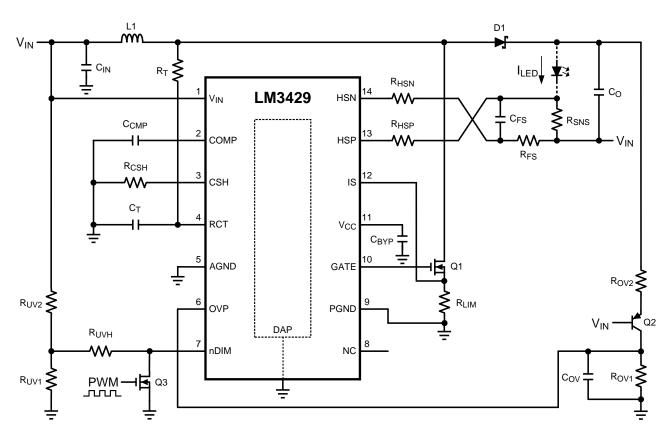

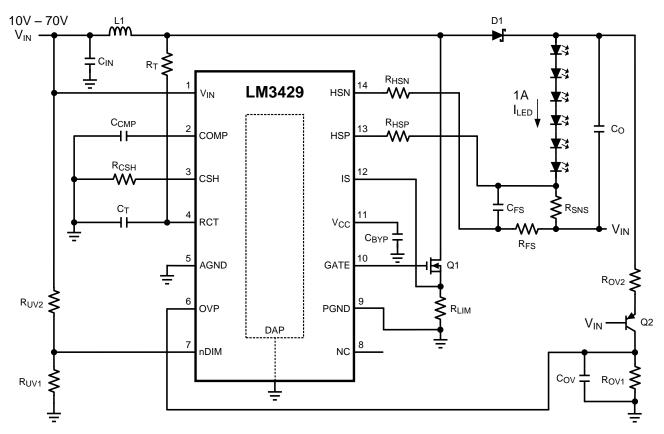

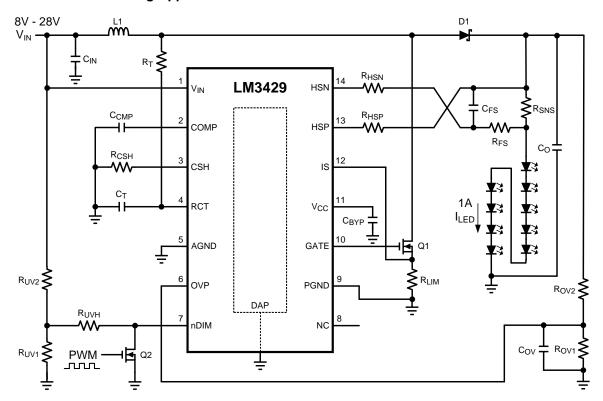

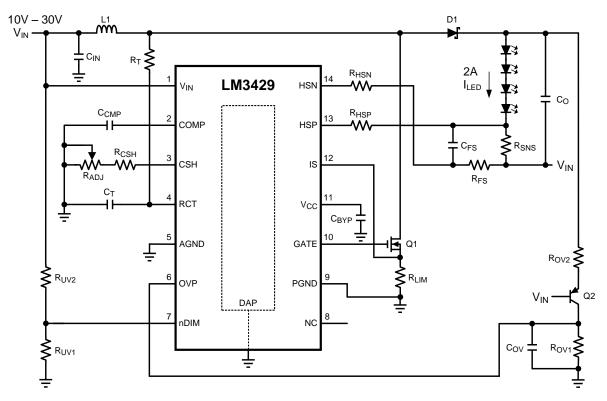

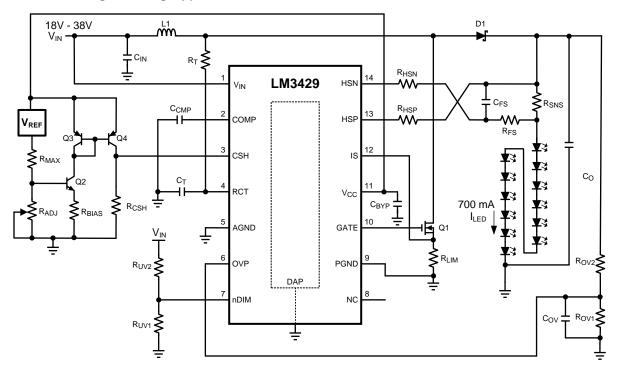

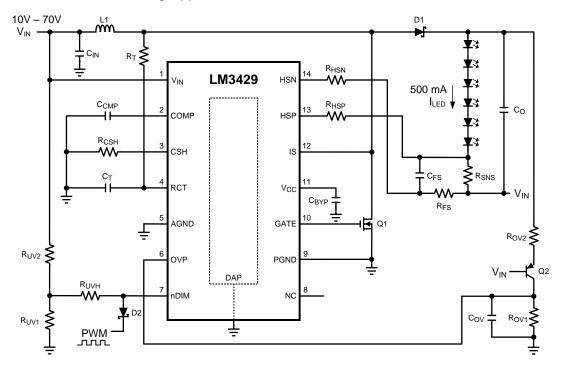

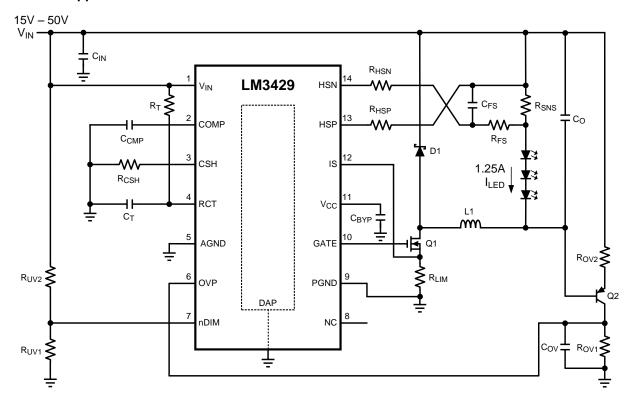

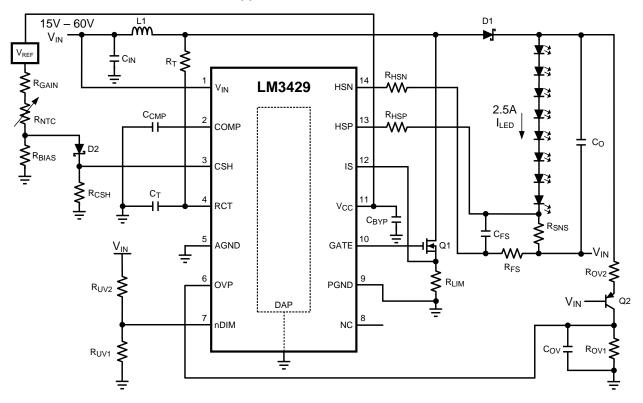

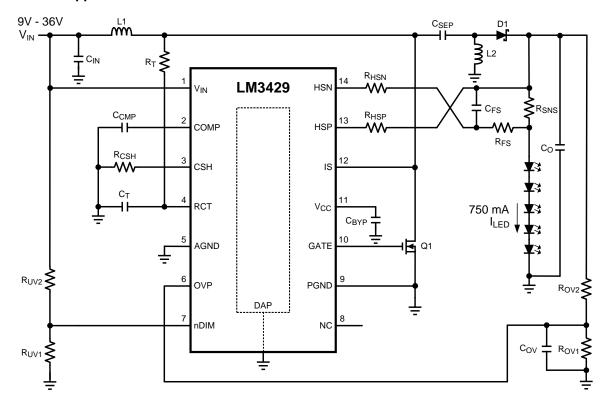

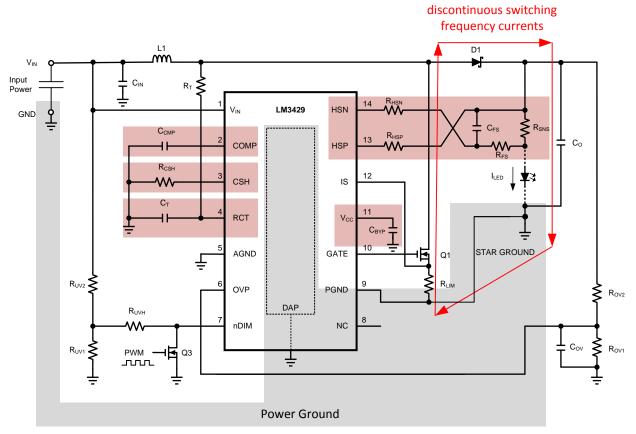

#### **Typical Boost Application Circuit**

## **Table of Contents**

| Applications 1 Description 1 | 8.1 Application Information                                                                                                                                                                                                                                              | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | 8.2 Typical Applications                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | 0.2 1, ploat 7, ppiloation                                                                                                                                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 9 Power Supply Recommendations                                                                                                                                                                                                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 9.1 Input Supply Current Limit                                                                                                                                                                                                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| _                            | 10 Layout                                                                                                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| •                            | 10.1 Layout Guidelines                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                            | 10.2 Layout Example                                                                                                                                                                                                                                                      | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 11 Device and Documentation Support                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| · -                          | 11.1 Device Support                                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 11.2 Documentation Support                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 11.3 Related Links                                                                                                                                                                                                                                                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • •                          | 11.4 Community Resources                                                                                                                                                                                                                                                 | . 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              | 11.5 Trademarks                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | 11.6 Electrostatic Discharge Caution                                                                                                                                                                                                                                     | . 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| G                            | 11.7 Glossary                                                                                                                                                                                                                                                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.4 Device Functional Modes  | 12 Mechanical, Packaging, and Orderable Information                                                                                                                                                                                                                      | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 6.5       Electrical Characteristics       5         6.6       Typical Characteristics       7         Detailed Description       9         7.1       Overview       9         7.2       Functional Block Diagram       9         7.3       Feature Description       10 | Pin Configuration and Functions39.1 Input Supply Current LimitSpecifications410Layout6.1 Absolute Maximum Ratings410.1 Layout Guidelines6.2 ESD Ratings410.2 Layout Example6.3 Recommended Operating Conditions411Device and Documentation Support6.4 Thermal Information511.1 Device Support6.5 Electrical Characteristics511.2 Documentation Support6.6 Typical Characteristics711.3 Related LinksDetailed Description911.4 Community Resources7.1 Overview911.5 Trademarks7.2 Functional Block Diagram911.6 Electrostatic Discharge Caution7.3 Feature Description1011.7 Glossary7.4 Device Functional Modes21Mechanical, Packaging, and Orderable |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision G (April 2013) to Revision H

**Page**

Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

Changes from Revision F (May 2013) to Revision G

Page

Submit Documentation Feedback

Copyright © 2009–2015, Texas Instruments Incorporated

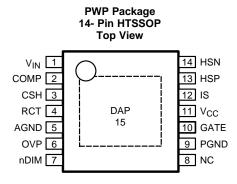

# 5 Pin Configuration and Functions

# **Pin Functions**

|             | PIN             |     |                             |                                                                                                                                                                                                                                                                       |  |

|-------------|-----------------|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.         | NAME            | 1/0 | DESCRIPTION                 | APPLICATION INFORMATION                                                                                                                                                                                                                                               |  |

| 1           | V <sub>IN</sub> | I   | Input Voltage               | Bypass with 100 nF capacitor to AGND as close to the device as possible in the circuit board layout.                                                                                                                                                                  |  |

| 2           | COMP            | I   | Compensation                | Connect a capacitor to AGND to set compensation.                                                                                                                                                                                                                      |  |

| 3           | CSH             | I   | Current Sense High          | Connect a resistor to AGND to set signal current. For analog dimming, connect current source or potentiometer to AGND (see <i>Analog Dimming</i> section).                                                                                                            |  |

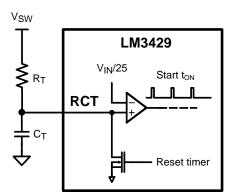

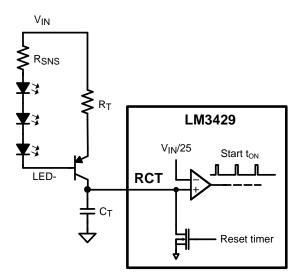

| 4           | RCT             | I   | Resistor Capacitor Timing   | Connect a resistor from the switch node and a capacitor to AGND to set the switching frequency.                                                                                                                                                                       |  |

| 5           | AGND            | GND | Analog Ground               | Connect to PGND through the DAP copper circuit board pad to provide proper ground return for CSH, COMP, and RCT.                                                                                                                                                      |  |

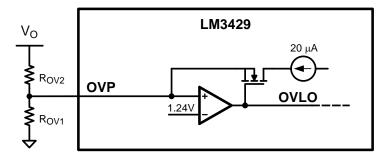

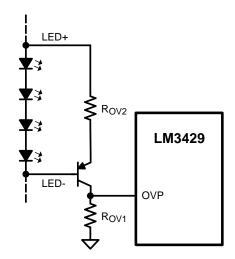

| 6           | OVP             | 1   | Overvoltage Protection      | Connect to a resistor divider from the output ( $V_O$ ) or the input to program output overvoltage lockout (OVLO). Turn-off threshold is 1.24 V and hysteresis for turn-on is provided by 20 $\mu$ A current source.                                                  |  |

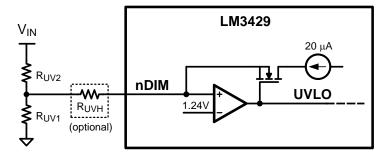

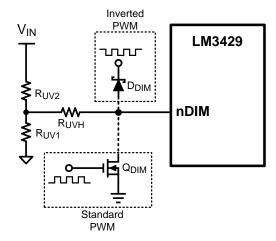

| 7           | nDIM            | 1   | Not DIM input               | Connect a PWM signal for dimming as detailed in the <i>PWM Dimn</i> section and/or a resistor divider from V <sub>IN</sub> to program input undervoltage lockout (UVLO). Turn-on threshold is 1.24 V and hysteresis for turn-off is provided by 20 µA current source. |  |

| 8           | NC              |     | No Connection               | Leave open.                                                                                                                                                                                                                                                           |  |

| 9           | PGND            | GND | Power Ground                | Connect to AGND through DAP copper pad to provide ground return for GATE.                                                                                                                                                                                             |  |

| 10          | GATE            | 0   | Gate Drive Output           | Connect to the gate of the external NFET.                                                                                                                                                                                                                             |  |

| 11          | V <sub>CC</sub> | I   | Internal Regulator Output   | Bypass with a 2.2 μF–3.3 μF, ceramic capacitor to PGND.                                                                                                                                                                                                               |  |

| 12          | IS              | I   | Main Switch Current Sense   | Connect to the drain of the main N-channel MosFET switch for $R_{DS-ON}$ sensing or to a sense resistor installed in the source of the same device.                                                                                                                   |  |

| 13          | HSP             | I   | LED Current Sense Positive  | Connect through a series resistor to LED current sense resistor (positive).                                                                                                                                                                                           |  |

| 14          | HSN             | I   | LED Current Sense Negative  | Connect through a series resistor to LED current sense resistor (negative).                                                                                                                                                                                           |  |

| DAP<br>(15) | DAP             | GND | Thermal pad on bottom of IC | Connect to AGND and PGND.                                                                                                                                                                                                                                             |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN             | MAX                                                                                                                                                         | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>IN</sub> , nDIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -0.3            | 76                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OVP, HSP, HSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -0.3            | 76                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3            | 3                                                                                                                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.3            | 76                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | –2 for 100 ns                                                                                                                                               | V    |

| Voltage         V <sub>CC</sub> COMP, CSH         GATE           PGND         V <sub>IN</sub> , nDIM           OVP, HSP, HSN         RCT           IS         IS    Maximum Junction Temperature  Maximum Lead Temperature (Reflow and Solder) (3)  Continuous Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -0.3            | 8                                                                                                                                                           | 1    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | COMP, CSH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -0.3            | 6                                                                                                                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -0.3            | V <sub>CC</sub>                                                                                                                                             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | –2.5 for 100 ns | V <sub>CC</sub> +2.5 for 100 ns                                                                                                                             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DONID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3            | 0.3                                                                                                                                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.5 for 100 ns  |                                                                                                                                                             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>IN</sub> , nDIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | -0.3 76 -0.3 3 -0.3 76 -2 for 100 ns -0.3 8 -0.3 6 -0.3 V <sub>CC</sub> 2.5 for 100 ns V <sub>CC</sub> +2.5 for 100 ns -0.3 0.3                             | mA   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OVP, HSP, HSN       -0.3       76         RCT       -0.3       3         -0.3       76         Is       -0.3       76         -2 for 100 ns         -2 for 100 ns         COMP, CSH       -0.3       0         -2.5 for 100 ns       V <sub>CC</sub> -2.5 for 100 ns       V <sub>CC+2.5</sub> for 100 ns         -2.5 for 100 ns       0.3         -2.5 (2.5 for 100 ns         -2.5 (2.5 for 100 ns <td cols<="" td=""><td>μΑ</td></td> | <td>μΑ</td>     | μΑ                                                                                                                                                          |      |

| Voltage         V <sub>CC</sub> −0.3         76           V <sub>CC</sub> −0.3         8           COMP, CSH         −0.3         6           −0.3         V <sub>CC</sub> −0.3         6           −0.3         V <sub>CC</sub> −0.3         V <sub>CC</sub> −2.5 for 100 ns         V <sub>CC+2.5</sub> for 100 ns         −0.3         0.3           −2.5 for 100 ns         V <sub>CC+2.5</sub> for 100 ns         −0.3         0.3           −2.5         2.5 for 100 ns         −1         −1           OVP, HSP, HSN         −100         −1           RCT         −1         5           IS         −1         1           COMP, CSH         −200         200           GATE         −1         1           Maximum Junction Temperature         Internally Limited           Maximum Lead Temperature (Reflow and Solder) (3)         260           Continuous Power Dissipation         Internally Limited | ^                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                                                                                                                                                             |      |

| Continuous Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 76 3 76 -2 for 100 ns 8 6 V <sub>CC</sub> 0 ns V <sub>CC+2.5</sub> for 100 ns 0.3 2.5 for 100 ns -1 -100 5 -1 200 1 nternally Limited 260 nternally Limited | mA   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | COMP, CSH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -200            | 200                                                                                                                                                         | μΑ   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -1              | 1                                                                                                                                                           | mA   |

| Maximum Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Maximum Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | Internally Limited                                                                                                                                          |      |

| Maximum Lead Temperature (Reflow and Solder) (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | 260                                                                                                                                                         | °C   |

| Continuous Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interna         | Internally Limited                                                                                                                                          |      |

| Storage Temperature, T <sub>sto</sub> –65 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 150             | °C                                                                                                                                                          |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                            |                                                                               |                                                                  | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------|

| LM3429                                     | IN PWP PACKAGE                                                                |                                                                  |       |      |

|                                            |                                                                               | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1) | ±2000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1000                                                            | V     |      |

| LM3429                                     | -Q1 IN PWP PACKAGE                                                            |                                                                  |       |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(3)</sup>                       | ±2000                                                            | V     |      |

|                                            | Electrostatic discharge                                                       | Charged device model (CDM), per AEC Q100-011                     | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

|                                      | MIN | MAX | UNIT |

|--------------------------------------|-----|-----|------|

| Operating Junction Temperature Range | -40 | 125 | °C   |

| Input Voltage V <sub>IN</sub>        | 4.5 | 75  | V    |

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/Distributors for availability and specifications.

<sup>(3)</sup> Refer to http://www.ti.com/packaging for more detailed information and mounting techniques.

#### 6.4 Thermal Information

|                        |                                              | LM3429-Q1    | LM3429       |      |

|------------------------|----------------------------------------------|--------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | PWP (HTSSOP) | UNIT |

|                        |                                              | 14 PINS      | 14 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 47.8         | 47.8         | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 26.5         | 26.5         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 22.3         | 22.3         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.7          | 0.7          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 22.1         | 22.1         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 3.3          | 3.3          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

MIN and MAX limits apply  $T_J = (-40^{\circ}\text{C to } 125^{\circ}\text{C})$  unless specified otherwise. Unless otherwise stated the following condition applies:  $V_{IN} = 14 \text{ V}$ .

|                      | PARAMETER                             | TEST CONDITIONS                                                       | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|----------------------|---------------------------------------|-----------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| STARTUP              | REGULATOR (V <sub>CC</sub> )          |                                                                       |                    |                    |                    |      |

| V <sub>CC-REG</sub>  | V <sub>CC</sub> Regulation            | I <sub>CC</sub> = 0 mA                                                | 6.3                | 6.9                | 7.35               | V    |

| I <sub>CC-LIM</sub>  | V <sub>CC</sub> Current Limit         | $V_{CC} = 0V$                                                         | 20                 | 27                 |                    | A    |

| IQ                   | Quiescent Current                     | Static                                                                |                    | 1.6                | 3                  | mA   |

| $V_{CC-UVLO}$        | V <sub>CC</sub> UVLO Threshold        | V <sub>CC</sub> Increasing                                            |                    | 4.17               | 4.5                |      |

|                      |                                       | V <sub>CC</sub> Decreasing                                            | 3.7                | 4.08               |                    | V    |

| V <sub>CC-HYS</sub>  | V <sub>CC</sub> UVLO Hysteresis       |                                                                       |                    | 0.1                |                    |      |

| OVERVOLT             | TAGE PROTECTION (OVP)                 |                                                                       |                    |                    |                    |      |

| V <sub>TH-OVP</sub>  | OVP OVLO Threshold                    | OVP Increasing                                                        | 1.18               | 1.24               | 1.28               | V    |

| I <sub>HYS-OVP</sub> | OVP Hysteresis Source Current         | OVP Active (high)                                                     | 10                 | 20                 | 30                 | μΑ   |

| ERROR AN             | IPLIFIER                              |                                                                       |                    |                    | <u> </u>           |      |

| V <sub>CSH</sub>     | CSH Reference Voltage                 | With Respect to AGND                                                  | 1.21               | 1.235              | 1.26               | V    |

|                      | Error Amplifier Input Bias Current    | MIN, MAX: T <sub>J</sub> = 25°C                                       | -0.6               | 0                  | 0.6                |      |