- Maximum Throughput 400 KSPS

- Built-In Reference and 8× FIFO

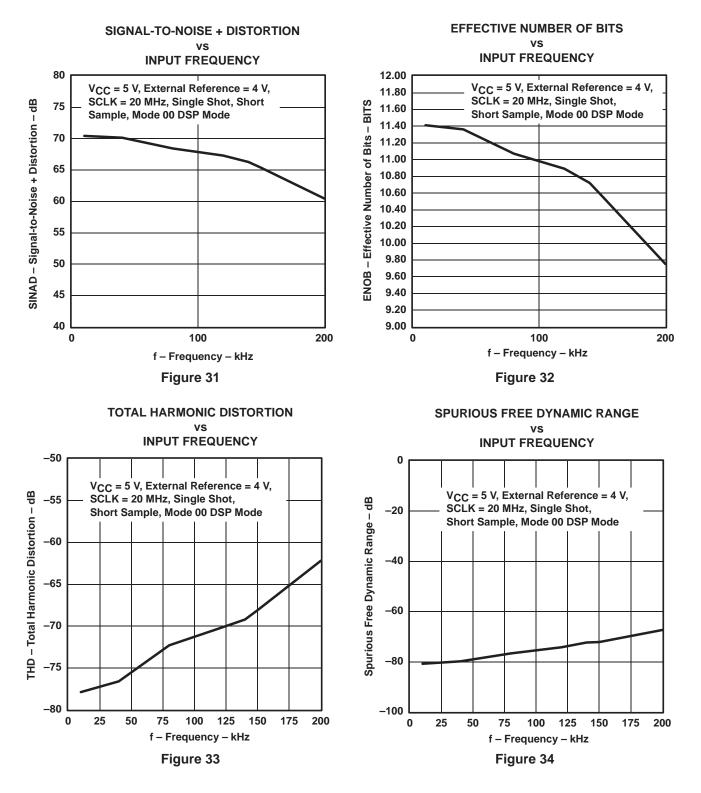

- Differential/Integral Nonlinearity Error: ±1 LSB

- Signal-to-Noise and Distortion Ratio: 69 dB, f<sub>i</sub> = 12 kHz

- Spurious Free Dynamic Range: 75 dB, f<sub>i</sub> = 12 kHz

- SPI/DSP-Compatible Serial Interfaces With SCLK up to 20 MHz

- Single Supply 5 Vdc

- Analog Input Range 0 V to Supply Voltage With 500 kHz BW

- Hardware Controlled and Programmable

Sampling Period

- Low Operating Current (4 mA at 5.5 V External Ref, 6 mA at 5.5 V, Internal Ref)

- Power Down: Software/Hardware

Power-Down Mode (1 μA Max, Ext Ref),

Auto Power-Down Mode (1 μA, Ext Ref)

- Programmable Auto-Channel Sweep

#### description

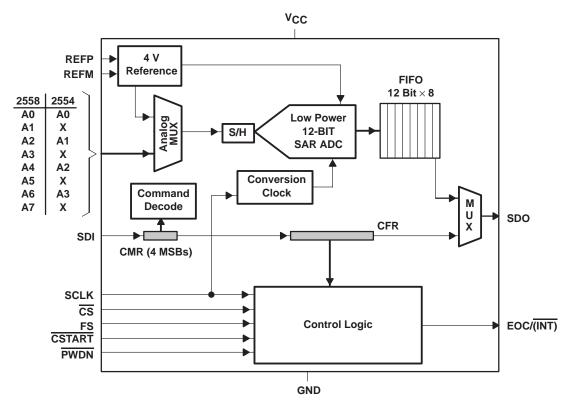

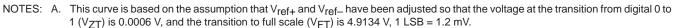

The TLC2558 and TLC2554 are a family of high-performance, 12-bit low power, 1.6  $\mu$ s, CMOS analog-to-digital converters (ADC) which operate from a single 5 V power supply. These devices have three digital inputs and a 3-state output [chip select ( $\overline{CS}$ ), serial input-output clock (SCLK), serial data input (SDI), and serial data output (SDO)] that provide a direct 4-wire interface to the serial port of most popular host microprocessors (SPI interface). When interfaced with a DSP, a frame sync (FS) signal is used to indicate the start of a serial data frame.

In addition to a high-speed A/D converter and versatile control capability, these devices have an on-chip analog multiplexer that can select any analog inputs or one of three internal self-test voltages. The sample-and-hold function is automatically started after the fourth SCLK edge (normal sampling) or can be controlled by a special pin, CSTART, to extend the sampling period (extended sampling). The normal sampling period can also be programmed as short (12 SCLKs) or as long (24 SCLKs) to accommodate faster SCLK operation popular among high-performance signal processors. The TLC2558 and TLC2554 are designed to operate with very low power consumption. The power-saving feature is further enhanced with software/hardware/auto power down modes and programmable conversion speeds. The converter uses the external SCLK as the source of the conversion clock to achieve higher (up to 1.6 µs when a 20 MHz SCLK is used) conversion speed. There is a 4-V internal reference available. An optional external reference can also be used to achieve maximum flexibility.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

#### functional block diagram

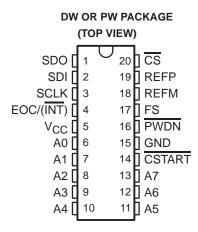

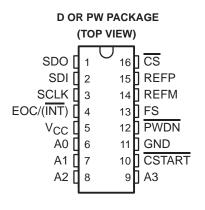

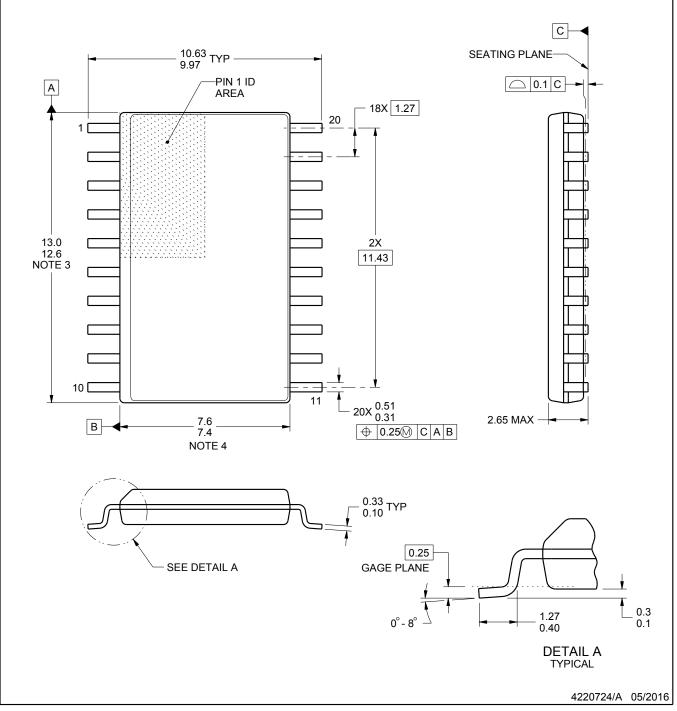

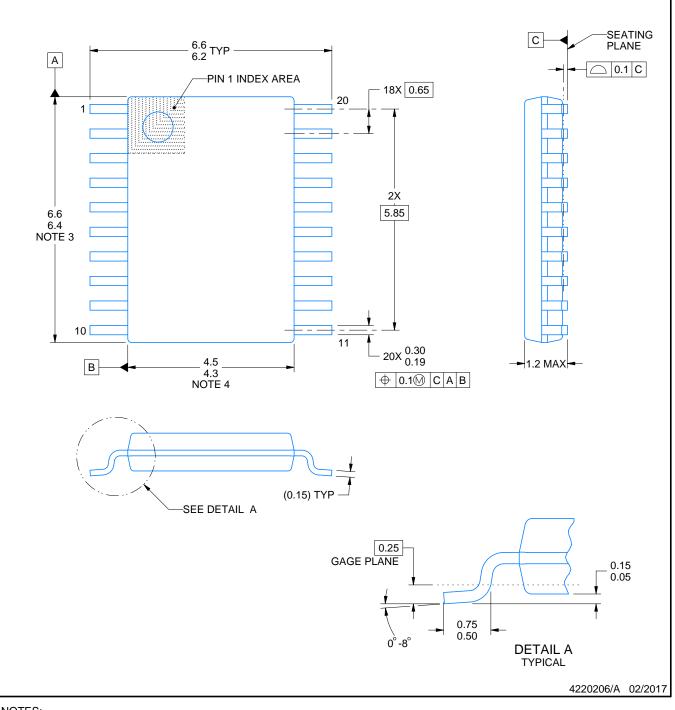

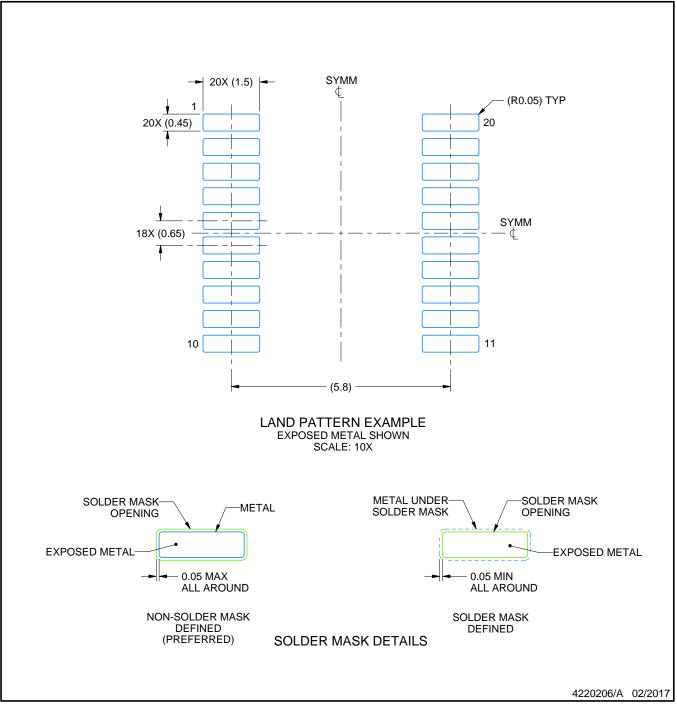

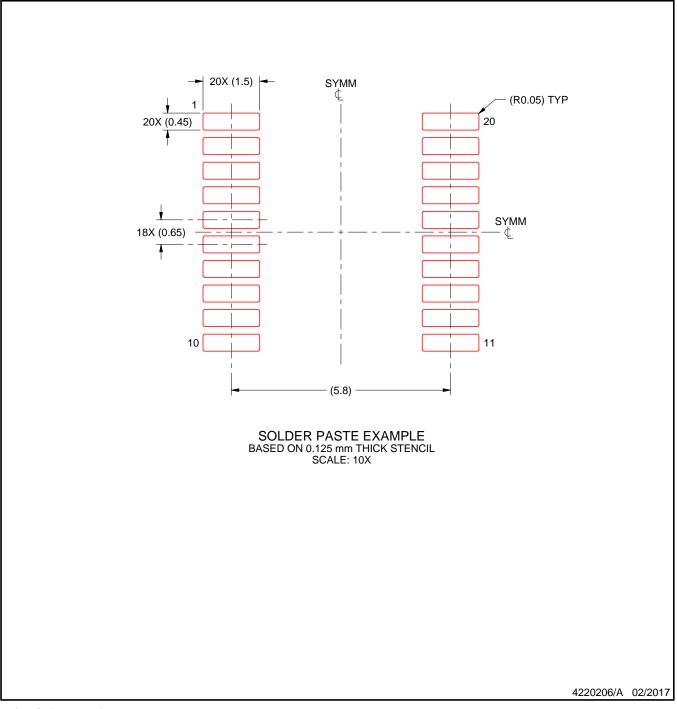

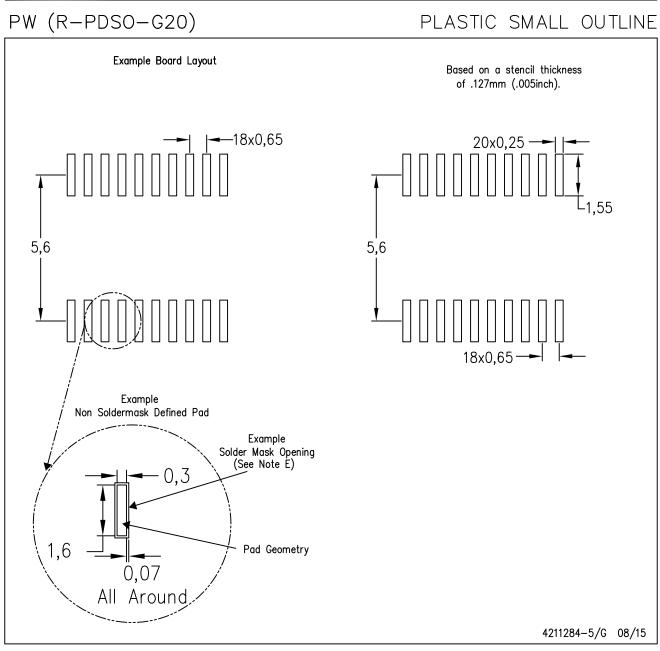

|               | PACKAGED DEVICES |                 |                |                  |  |  |  |

|---------------|------------------|-----------------|----------------|------------------|--|--|--|

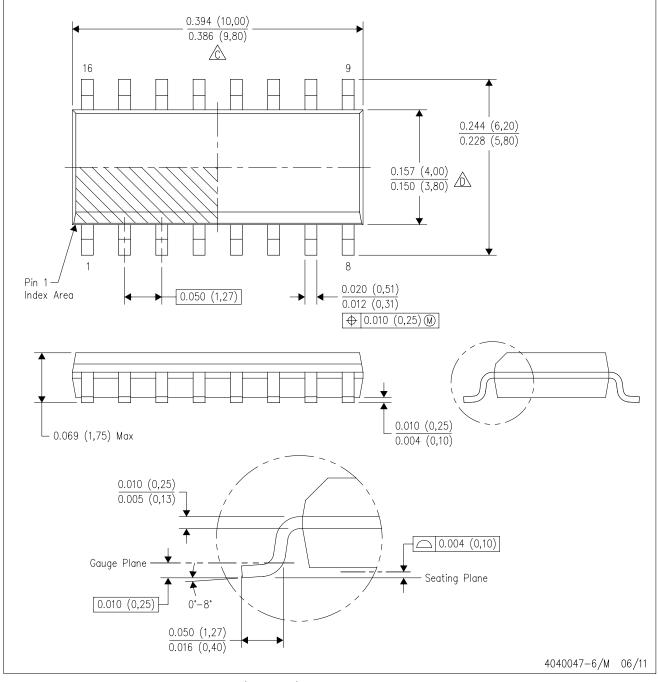

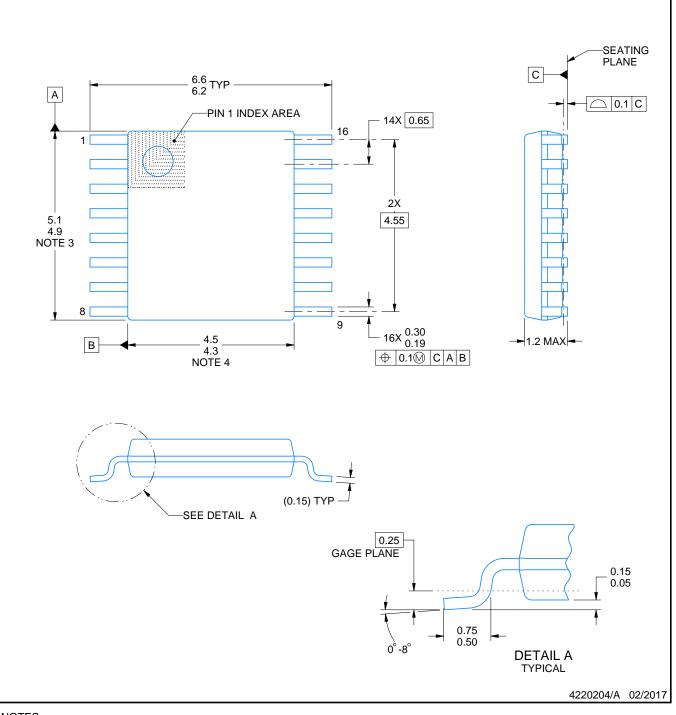

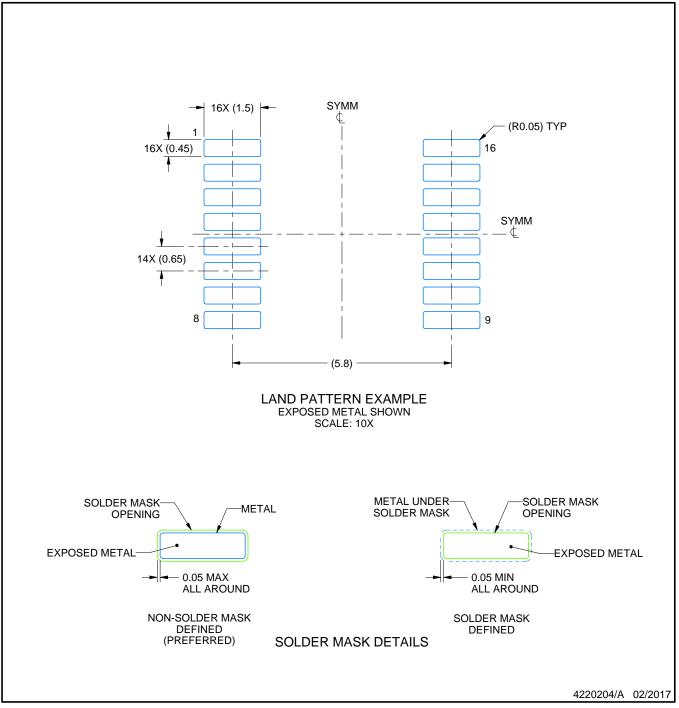

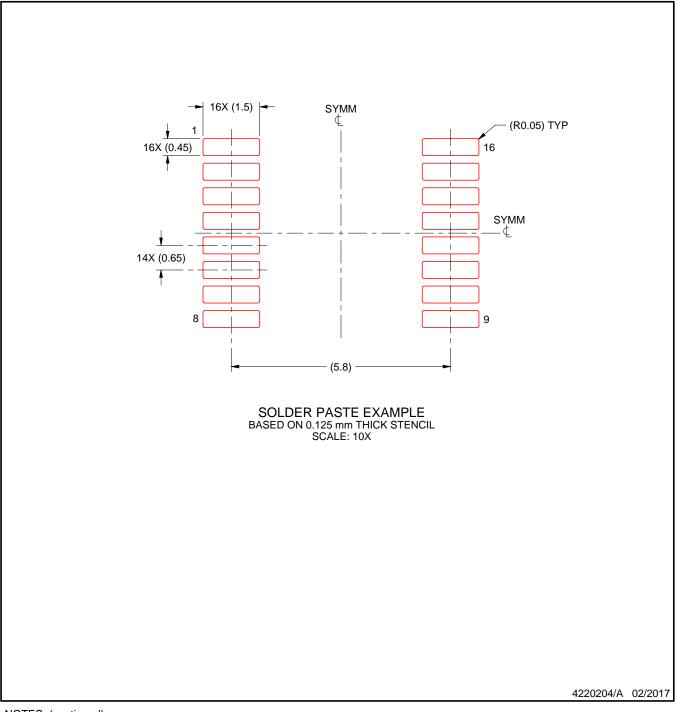

| TA            | 20-TSSOP<br>(PW) | 20-SOIC<br>(DW) | 16-SOIC<br>(D) | 16-TSSOP<br>(PW) |  |  |  |

| 0°C to 70°C   | TLC2558CPW       | TLC2558CDW      | TLC2554CD      | TLC2554CPW       |  |  |  |

| -40°C to 85°C | TLC2558IPW       | TLC2558IDW      | TLC2554ID      | TLC2554IPW       |  |  |  |

#### **Terminal Functions**

| TERMINAL                                                                                                                              |                  |                                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                                                                  | N                | 0.                                       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| NAME                                                                                                                                  | TLC2554          | TLC2558                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| A0         A0           A1         A1           A2         A2           A3         A3           A4         A5           A6         A7 | 6<br>7<br>8<br>9 | 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | I   | Analog signal inputs. The analog inputs are applied to these terminals and are internally multiplexed. The driving source impedance should be less than or equal to 1 k $\Omega$ .<br>For a source impedance greater than 1 k $\Omega$ , use the asynchronous conversion start signal CSTART (CSTART low time controls the sampling period) or program long sampling period to increase the sampling time.                                                                                                                                                                                                                                                   |  |

| CS                                                                                                                                    | 16               | 20                                       | I   | Chip select. A high-to-low transition on the $\overline{CS}$ input resets the internal 4-bit counter, enables SDI, and removes SDO from 3-state within a maximum setup time. SDI is disabled within a setup time after the 4-bit counter counts to 16 (clock edges) or a low-to-high transition of $\overline{CS}$ whichever happens first. SDO is 3-stated after the rising edge of $\overline{CS}$ .<br>$\overline{CS}$ can be used as the FS pin when a dedicated serial port is used.                                                                                                                                                                    |  |

| CSTART                                                                                                                                | 10               | 14                                       | I   | This terminal controls the start of sampling of the analog input from a selected multiplex channel. A high-to-low transition starts sampling of the analog input signal. A low-to-high transition puts the $S/H$ in hold mode and starts the conversion. This input is independent from SCLK and works when $\overline{CS}$ is high (inactive). The low time of $\overline{CSTART}$ controls the duration of the sampling period of the converter (extended sampling).                                                                                                                                                                                       |  |

|                                                                                                                                       |                  |                                          |     | Tie this terminal to V <sub>CC</sub> if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| EOC/(INT)                                                                                                                             | 4                | 4                                        | 0   | End of conversion or interrupt to host processor.<br><b>[PROGRAMMED AS EOC]</b> : This output goes from a high-to-low logic level at the end of the sampling period and remains low until the conversion is complete and data are ready for transfer. EOC is used in conversion mode 00 only.<br><b>[PROGRAMMED AS INT]</b> : This pin can also be programmed as an interrupt output signal to the host processor. The falling edge of INT indicates data are ready for output. The following $\overline{CS} \downarrow$ or $\overline{FS}^{\uparrow}$ clears INT. The falling edge of INT puts SDO back to 3-state even if $\overline{CS}$ is still active. |  |

| FS                                                                                                                                    | 13               | 17                                       | I   | DSP frame sync input. Indication of the start of a serial data frame in or out of the device. If FS remains low at the falling edge of $\overline{CS}$ , SDI is not enabled. A high-to-low transition on the FS input resets the internal 4-bit counter and enables SDI within a maximum setup time. SDI is disabled within a setup time after the 4-bit counter counts to 16 (clock edges) or a low-to-high transition of $\overline{CS}$ whichever happens first. SDO is 3-stated after the 16th bit is presented.<br>Tie this terminal to V <sub>CC</sub> if not used.                                                                                    |  |

| GND                                                                                                                                   | 11               | 15                                       | I   | Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWDN                                                                                                                                  | 12               | 16                                       | I   | Both analog and reference circuits are powered down when this pin is at logic zero. The device can be restarted by active CS or CSTART after this pin is pulled back to logic one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SCLK                                                                                                                                  | 3                | 3                                        | I   | Input serial clock. This terminal receives the serial SCLK from the host processor. SCLK is used to clock the input SDI to the input register. It is also used as the source of the conversion clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SDI                                                                                                                                   | 2                | 2                                        | I   | Serial data input. The input data is presented with the MSB (D15) first. The first 4-bit MSBs, D(15–12) are decoded as one of the 16 commands (12 only for the TLC2554). All trailing blanks are filled with zeros. The configure write commands require an additional 12 bits of data. When FS is not used (FS =1), the first MSB (D15) is expected after the falling edge of CS and is shifted in on the rising edges of SCLK (after CS $\downarrow$ ). When FS is used (typical with an active FS from a DSP) the first MSB (D15) is expected after the falling edge of FS and is shifted in on the falling edges of SCLK.                                |  |

SLAS220A –JUNE 1999

#### **Terminal Functions (Continued)**

| ٦     | TERMINAL NO. |         | TERMINAL |                                                                                                                                                                                                                                                                                                           | TERMINAL |  | TERMINAL |  |  |

|-------|--------------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|----------|--|--|

| NAME  |              |         | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                               |          |  |          |  |  |

| INAME | TLC2554      | TLC2558 |          |                                                                                                                                                                                                                                                                                                           |          |  |          |  |  |

| SDO   | 1            | 1       | 0        | The 3-state serial output for the A/D conversion result. SDO is kept in the high-impedance state when $\overline{CS}$ is high and after the $\overline{CS}$ falling edge and until the MSB (D15) is presented. The output format is MSB (D15) first.                                                      |          |  |          |  |  |

|       |              |         |          | When FS is not used (FS = 1 at the falling edge of $\overline{CS}$ ), the MSB (D15) is presented to the SDO pin after the $\overline{CS}$ falling edge, and successive data are available at the rising edge of SCLK.                                                                                     |          |  |          |  |  |

|       |              |         |          | hen FS is used (FS = 0 at the falling edge of $\overline{CS}$ ), the MSB (D15) is presented to SDO after the ling edge of $\overline{CS}$ and FS = 0 is detected. Successive data are available at the falling edge of SCLK his is typically used with an active FS from a DSP.)                          |          |  |          |  |  |

|       |              |         |          | For conversion and FIFO read cycles, the first 12 bits are the result from the previous conversion (data) followed by 4 trailing zeros. The first four bits from SDO for CFR read cycles should be ignored. The register content is in the last 12 bits. SDO is 3 stated after the 16th bit.              |          |  |          |  |  |

| REFM  | 14           | 18      | I        | External reference input or internal reference decoupling.                                                                                                                                                                                                                                                |          |  |          |  |  |

| REFP  | 15           | 19      | I        | External reference input or internal reference decoupling. (Shunt capacitors of 10 $\mu$ F and 0.1 $\mu$ F between REFP and REFM.) The maximum input voltage range is determined by the difference between the voltage applied to this terminal and the REFM terminal when an external reference is used. |          |  |          |  |  |

| VCC   | 5            | 5       | Ι        | Positive supply voltage                                                                                                                                                                                                                                                                                   |          |  |          |  |  |

#### detailed description

#### analog inputs and internal test voltages

The 4/8 analog inputs and three internal test inputs are selected by the analog multiplexer depending on the command entered. The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching.

#### pseudo-differential/single-ended input

All analog inputs can be programmed as single-ended or pseudo-differential mode. Pseudo-differential mode is enabled by setting CFR.D7 – 1. Only three analog input channels (or seven channels for TLC2558) are available for TLV2554 since one input (A1 for TLC2554 or A2 for TLC2558) is used as the MINUS input when pseudo-differential mode is used. The minus input pin can have a maximum  $\pm 0.2$  V ripple. This is normally used for ground noise rejection.

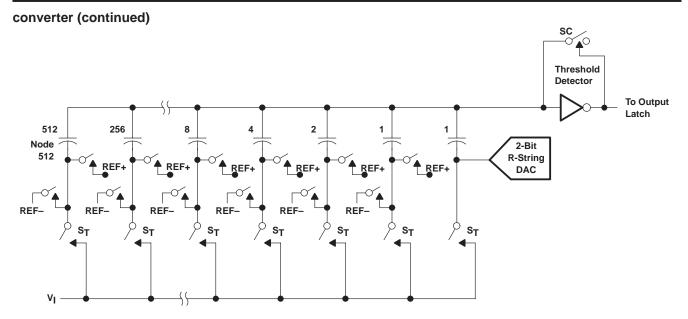

#### converter

The TLC2554/58 uses a 12-bit successive approximation ADC and 2-bit resistor string. The CMOS threshold detector in the successive-approximation conversion system determines each bit by examining the charge on a series of binary-weighted capacitors (see Figure 1). In the first phase of the conversion process, the analog input is sampled by closing the SC switch and all ST switches simultaneously. This action charges all the capacitors to the input voltage.

SLAS220A - JUNE 1999

Figure 1. Simplified Model of the Successive-Approximation System

In the next phase of the conversion process the threshold detector begins identifying bits by identifying the charge (voltage) on each capacitor relative to the reference (REFM) voltage. In the switching sequence, ten capacitors are examined separately until all ten bits are identified and the charge-convert sequence is repeated. In the first step of the conversion phase, the threshold detector looks at the first capacitor (weight = 512). Node 512 of this capacitor is switched to the REFP voltage, and the equivalent nodes of all the other capacitors on the ladder are switched to REFM. If the voltage at the summing node is greater than the trip point of the threshold detector (approximately one-half the V<sub>CC</sub> voltage), a bit 0 is placed in the output register and the 512-weight capacitor is switched to REFM. If the voltage at the summing node is less than the trip point of the threshold detector, a bit 1 is placed in the register. The 512-weight capacitor remains connected to REFP through the remainder of the successive-approximation process. The process is repeated for the 1024-weight capacitor, the 128-weight capacitor, and so forth down the line until all bits are counted.

With each step of the successive-approximation process, the initial charge is redistributed among the capacitors. The conversion process relies on charge redistribution to count and weigh the bits from MSB to LSB.

#### serial interface

| INPUT DATA FORMAT |                          |  |  |

|-------------------|--------------------------|--|--|

| MSB LSB           |                          |  |  |

| D15–D12           | D11–D0                   |  |  |

| Command           | Configuration data field |  |  |

Input data is binary. All trailing blanks can be filled with zeros.

| OUTPUT DATA FORMAT READ CFR |                  |               |  |  |

|-----------------------------|------------------|---------------|--|--|

| MSB LSB                     |                  |               |  |  |

| D15–D12                     | D12 D11–D0       |               |  |  |

| Don't care                  | Register content |               |  |  |

|                             |                  |               |  |  |

| OUTPUT DATA F               | FORMAT CONVERS   | ION/READ FIFO |  |  |

| MSB LSB                     |                  |               |  |  |

| D15                         | D3–D0            |               |  |  |

| Conversion result           | All zeros        |               |  |  |

SLAS220A –JUNE 1999

#### serial interface (continued)

The output data format is either binary (unipolar straight binary) or 2s complement.

#### binary

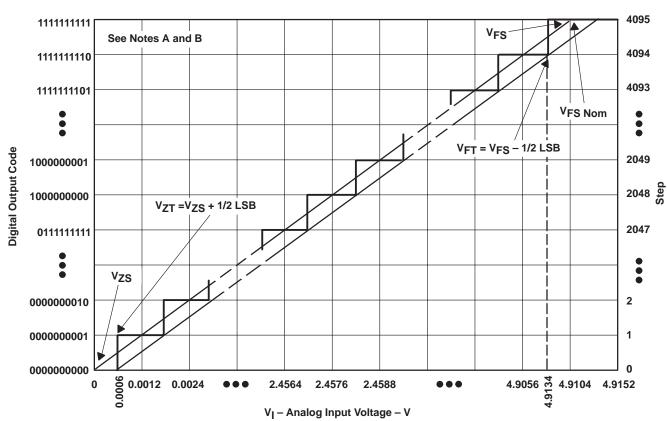

Zero scale code = 000h, Vcode = VREFM Full scale code = FFFh, Vcode = VREFP – 1 LSB

#### 2's complement

Minus full scale code = 800h, Vcode = VREFM Full scale code = 7FFh, Vcode = VREFP – 1 LSB

#### control and timing

#### start of the cycle:

- When FS is not used (FS = 1 at the falling edge of CS), the falling edge of CS is the start of the cycle. Input data is shifted in on the rising edge, and output data changes on the falling edge of SCLK. This is typically used for a SPI microcontroller, although it can also be used for a DSP.

- When FS is used (FS is an active signal from a DSP), the falling edge of FS is the start of the cycle. Input data is shifted in on the falling edge, and output data changes on the rising edge of SCLK. This is typically used for a TMS320 DSP.

#### first 4-MSBs: the command register (CMR)

The TLC2554/TLC2558 have a 4-bit command set (see Table 1) plus a 12-bit configuration data field. Most of the commands require only the first 4 MSBs, i.e. without the 12-bit data field.

#### NOTE:

The device requires a write CFR (configuration register) with 000h data (write A000h to the serial input) at power up to initialize host select mode.

The valid commands are listed in Table 1.

| SDI D(15-12) | BINARY, HEX     | TLC2558 COMMAND                                              | TLC2554 COMMAND               |  |  |  |

|--------------|-----------------|--------------------------------------------------------------|-------------------------------|--|--|--|

| 0000b        | 0000h           | Select analog input channel 0 Select analog input channel    |                               |  |  |  |

| 0001b        | 1000h           | Select analog input channel 1 N/A                            |                               |  |  |  |

| 0010b        | 2000h           | Select analog input channel 2 Select analog input channel    |                               |  |  |  |

| 0011b        | 3000h           | Select analog input channel 3                                | N/A                           |  |  |  |

| 0100b        | 4000h           | Select analog input channel 4                                | Select analog input channel 2 |  |  |  |

| 0101b        | 5000h           | Select analog input channel 5 N/A                            |                               |  |  |  |

| 0110b        | 6000h           | Select analog input channel 6                                | Select analog input channel 3 |  |  |  |

| 0111b        | 7000h           | Select analog input channel 7 N/A                            |                               |  |  |  |

| 1000b        | 8000h           | SW power down (analog + reference)                           |                               |  |  |  |

| 1001b        | 9000h           | Read CFR register data shown as SDO D(11–0)                  |                               |  |  |  |

| 1010b        | A000h plus data | Write CFR followed by 12-bit data                            |                               |  |  |  |

| 1011b        | B000h           | Select test, voltage = (REFP+REFM)/2                         |                               |  |  |  |

| 1100b        | C000h           | Select test, voltage = REFM                                  |                               |  |  |  |

| 1101b        | D000h           | Select test, voltage = REFP                                  |                               |  |  |  |

| 1110b        | E000h           | FIFO read, FIFO contents shown as SDO D(15–4), D(3–0) = 0000 |                               |  |  |  |

| 1111b        | F000h plus data | Reserved                                                     |                               |  |  |  |

#### Table 1. TLC2554/TLC2558 Command Set

#### control and timing (continued)

#### configuration

Configuration data is stored in one 12-bit configuration register (CFR) (see Table 2 for CFR bit definitions). Once configured after first power up, the information is retained in the H/W or S/W power-down state. When the device is being configured, a write CFR cycle is issued by the host processor. This is a 16-bit write. If the SCLK stops after the first 8 bits are entered, then the next eight bits can be taken after the SCLK is resumed. The status of the CFR can be read with a read CFR command.

| BIT                 | DEFINITION                                                                                                                                                                                                                                                                              |         |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| D(15–12)            | All zeros, nonprogrammable                                                                                                                                                                                                                                                              |         |  |  |

| D11                 | Reference select<br>0: External<br>1: Internal                                                                                                                                                                                                                                          |         |  |  |

| D10                 | Output select<br>0: Unipolar straight binary<br>1: 2's complement                                                                                                                                                                                                                       |         |  |  |

| D9                  | Sample period select<br>0: Short sampling 12 SCLKs (1x sampling time)<br>1: Long sampling 24 SCLKs (2x sampling time)                                                                                                                                                                   |         |  |  |

| D8                  | Conversion clock source select<br>0: Conversion clock = SCLK<br>1: Conversion clock = SCLK/2                                                                                                                                                                                            |         |  |  |

| D7                  | Input select<br>0: Normal<br>1: Pseudo differential CH A2(2558) or CH A1 (2554) is the differential input                                                                                                                                                                               |         |  |  |

| D(6,5)              | Conversion mode select<br>00: Single shot mode<br>01: Repeat mode<br>10: Sweep mode<br>11: Repeat sweep mode                                                                                                                                                                            |         |  |  |

| D(4,3) <sup>†</sup> | TLC2558                                                                                                                                                                                                                                                                                 | TLC2554 |  |  |

|                     | Sweep auto sequence select         Sweep auto sequence select           00: 0-1-2-3-4-5-6-7         00: N/A           01: 0-2-4-6-0-2-4-6         01: 0-1-2-3-0-1-2-3           10: 0-0-2-2-4-4-6-6         10: 0-0-1-1-2-2-3-3           11: 0-2-0-2-0-2         11: 0-1-0-1-0-1       |         |  |  |

| D2                  | EOC/INT – pin function select<br>0: Pin used as INT<br>1: Pin used as EOC                                                                                                                                                                                                               |         |  |  |

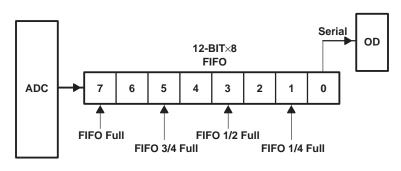

| D(1,0)              | FIFO trigger level (sweep sequence length)<br>00: Full ( <u>INT</u> generated after FIFO level 7 filled)<br>01: 3/4 ( <u>INT</u> generated after FIFO level 5 filled)<br>10: 1/2 ( <u>INT</u> generated after FIFO level 3 filled)<br>11: 1/4 (INT generated after FIFO level 1 filled) |         |  |  |

| Table 2 TI C2554/TI C25 | 58 Configuration Register | (CFR) Bit Definitions |

|-------------------------|---------------------------|-----------------------|

|                         | so configuration register |                       |

<sup>†</sup> These bits only take effect in conversion modes 10 and 11.

#### sampling

The sampling period starts after the first 4 input data are shifted in if they are decoded as one of the conversion commands. These are select analog input (channel 0 through 7) and select test (channel 1 through 3).

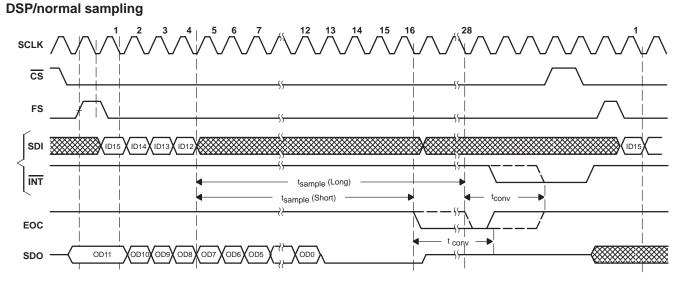

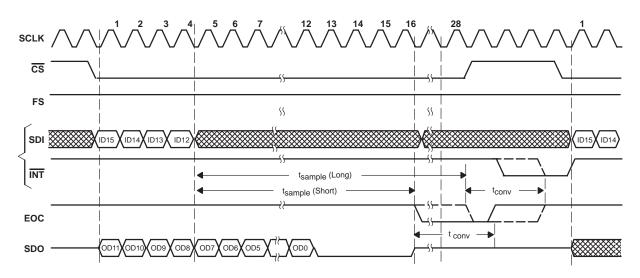

#### normal sampling

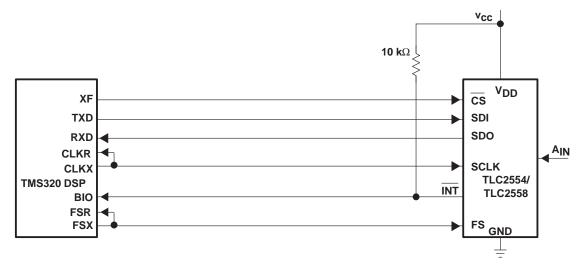

When the converter is using normal sampling, the sampling period is programmable. It can be 12 SCLKs (short sampling) or 24 SCLKs (long sampling). Long sampling helps the input analog signal sampled to settle to 0.5 LSB accuracy when input source resistance is high.

#### extended sampling

An asynchronous (to the SCLK) signal, via dedicated hardware pin CSTART, can be used in order to have total control of the sampling period and the start of a conversion. This is extended sampling. The falling edge of CSTART is the start of the sampling period. The rising edge of CSTART is the end of the sampling period and the start of an application that requires:

- The use of an extended sampling period to accommodate different input source impedance.

- The use of a faster I/O clock on the serial port but not enough sampling time is available due to the fixed number of SCLKs. This could be due to a high input source impedance or due to higher MUX ON resistance at lower supply voltage (refer to application information).

Once the conversion is complete, the processor can initiate a read cycle using either the read FIFO command to read the conversion result or simply select the next channel number for conversion. Since the device has a valid conversion result in the output buffer, the conversion result is simply presented at the serial data output.

#### TLC2554/TLC2558 conversion modes

The TLC2554 and TLC2558 have four different conversion modes (mode 00, 01, 10, 11). The operation of each mode is slightly different, depending on how the converter performs the sampling and which host interface is used. The trigger for a conversion can be an active  $\overline{CSTART}$  (extended sampling),  $\overline{CS}$  (normal sampling, SPI interface), or FS (normal sampling, TMS320 DSP interface). When FS is used as the trigger,  $\overline{CS}$  can be held active, i.e.  $\overline{CS}$  does not need to be toggled through the trigger sequence. Different types of triggers should not be mixed throughout the repeat and sweep operations. When  $\overline{CSTART}$  is used as the trigger, the conversion starts on the rising edge of  $\overline{CSTART}$ . The minimum low time for  $\overline{CSTART}$  is 800 ns. If an active  $\overline{CS}$  or FS is used as the trigger, the conversion) should be allowed between consecutive triggers so that no conversion is terminated prematurely.

#### one shot mode (mode 00)

One shot mode (mode 00) does not use the FIFO, and the EOC is generated as the conversion is in progress (or INT is generated after the conversion is done).

#### repeat mode (mode 01)

Repeat mode (mode 01) uses the FIFO. Once the programmed FIFO threshold is reached, the FIFO must be read, or the data is lost and the sequence starts over again. This allows the host to set up the converter and continue monitoring a fixed input and come back to get a set of samples when preferred. The first conversion must start with a select command so an analog input channel can be selected.

#### sweep mode (mode 10)

Sweep mode (mode 10) also uses the FIFO. Once it is programmed in this mode, all of the channels listed in the selected sweep sequence are visited in sequence. The results are converted and stored in the FIFO. This sweep sequence may not be completed if the FIFO threshold is reached before the list is completed. This allows the system designer to change the sweep sequence length. Once the FIFO has reached its programmed threshold, an interrupt (INT) is generated. The host must issue a read FIFO command to read and clear the FIFO before the next sweep can start.

#### TLC2554/TLC2558 conversion modes (continued)

#### repeat sweep mode (mode 11)

Repeat sweep mode (mode 11) works the same way as mode 10 except the operation has an option to continue even if the FIFO threshold is reached. Once the FIFO has reached its programmed threshold, an interrupt ( $\overline{INT}$ ) is generated. Then two things may happen:

- 1. The host may choose to act on it (read the FIFO) or ignore it. If the next cycle is a read FIFO cycle, all of the data stored in the FIFO is retained until it has been read in order.

- 2. If the next cycle is not a read FIFO cycle, or another CSTART is generated, all of the content stored in the FIFO is cleared before the next conversion result is stored in the FIFO, and the sweep is continued.

| CONVERSION<br>MODE | CFR<br>D(6,5) | SAMPLING<br>TYPE | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| One shot           | 00            | Normal           | <ul> <li>Single conversion from a selected channel</li> <li>CS or FS to start select/sampling/conversion/read</li> <li>One INT or EOC generated after each conversion</li> <li>Host must serve INT by selecting channel, and converting and reading the previous output.</li> </ul>                                                                                                                                                                                                                                  |

|                    |               | Extended         | <ul> <li>Single conversion from a selected channel</li> <li><u>CS</u> to select/read</li> <li><u>CSTART</u> to start sampling and conversion</li> <li>One INT or EOC generated after each conversion</li> <li>Host must serve INT by selecting next channel and reading the previous output.</li> </ul>                                                                                                                                                                                                              |

| Repeat             | 01            | Normal           | <ul> <li><u>Repeated conversions from a selected channel</u></li> <li><u>CS or FS to start sampling/conversion</u></li> <li>One <u>INT</u> generated after FIFO is filled up to the threshold</li> <li>Host must serve <u>INT</u> by either 1) (FIFO read) reading out all of the FIFO contents up to the threshold, then repeat conversions from the same selected channel or 2) writing another command(s) to change the conversion mode. If the FIFO is not read when INT is served, it is cleared.</li> </ul>    |

|                    |               | Extended         | <ul> <li>Same as normal sampling except CSTART starts each sampling and conversion when CS is<br/>high.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sweep              | 10            | Normal           | <ul> <li>One conversion per channel from a sequence of channels</li> <li>CS or FS to start sampling/conversion</li> <li>One INT generated after FIFO is filled up to the threshold</li> <li>Host must serve INT by (FIFO read) reading out all of the FIFO contents up to the threshold, then write another command(s) to change the conversion mode.</li> </ul>                                                                                                                                                     |

|                    |               | Extended         | <ul> <li>Same as normal sampling except CSTART starts each sampling and conversion when CS is<br/>high.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

| Repeat sweep       | 11            | Normal           | <ul> <li><u>Repeated conversions from a sequence of channels</u></li> <li><u>CS or FS to start sampling/conversion</u></li> <li>One <u>INT</u> generated after FIFO is filled up to the threshold</li> <li>Host must serve <u>INT</u> by either 1) (FIFO read) reading out all of the FIFO contents up to the threshold, then repeat conversions from the same selected channel or 2) writing another command(s) to change the conversion mode. If the FIFO is not read when INT is served it is cleared.</li> </ul> |

|                    |               | Extended         | <ul> <li>Same as normal sampling except CSTART starts each sampling and conversion when CS is<br/>high.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 3. TLC2554/TLC2558 Conversion Mode

NOTE: Programming the EOC/INT pin as the EOC signal works for mode 00 only. The other three modes automatically generate an INT signal irrespective of whether EOC/INT is programmed.

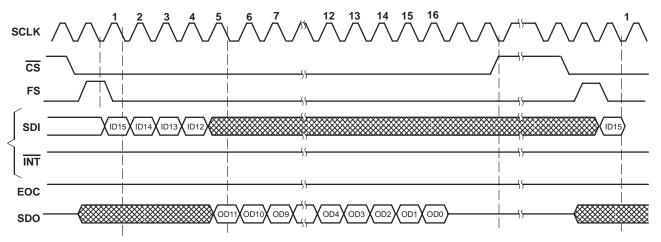

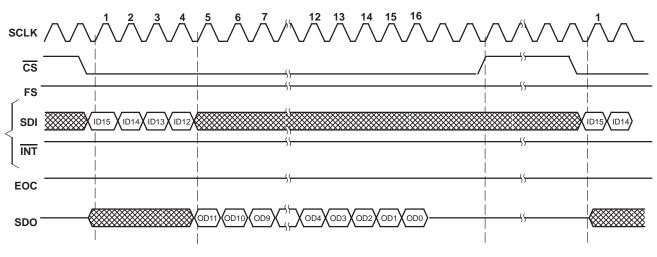

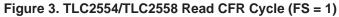

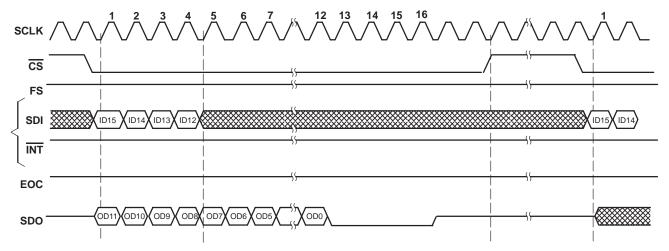

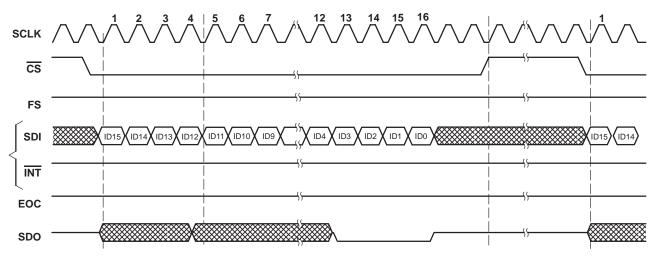

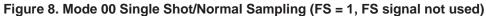

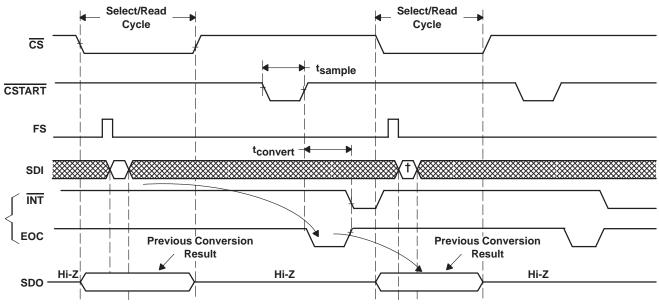

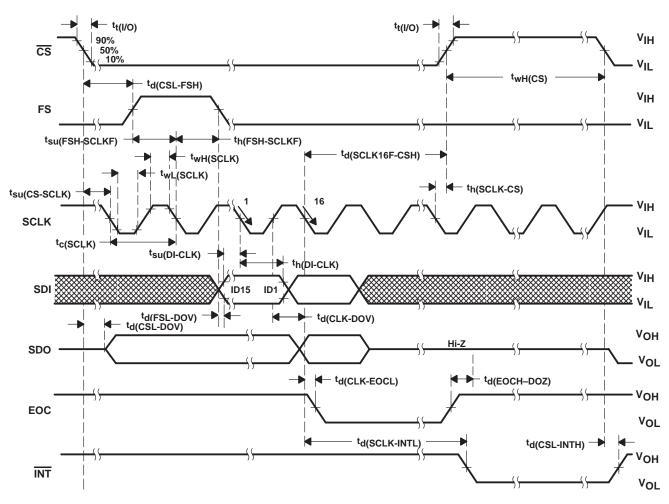

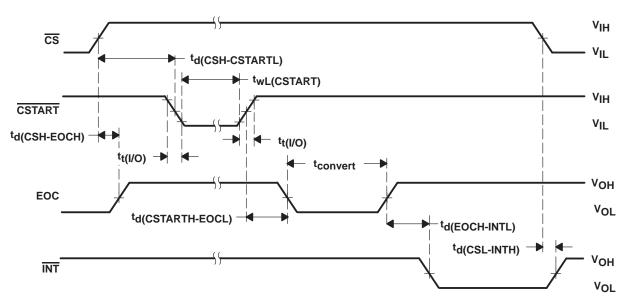

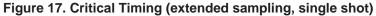

#### timing diagrams

The timing diagrams can be categorized into two major groups: nonconversion and conversion. The nonconversion cycles are read and write (configuration). None of these cycles carry a conversion. Conversion cycles are those four modes of conversion.

#### read cycle (read FIFO or read CFR)

#### read CFR cycle:

The read command is decoded in the first 4 clocks. SDO outputs the contents of the CFR after the 4th SCLK.

Figure 2. TLC2554/TLC2558 Read CFR Cycle (FS active)

#### read cycle (read FIFO or read CFR) (continued)

#### FIFO read cycle

The first command in the active cycle after INT is generated, if the FIFO is used, is assumed as the FIFO read command. The first FIFO content is output immediately before the command is decoded. If this command is not a FIFO read, then the output is terminated but the first data in the FIFO is retained until a valid FIFO read command is decoded. Use of more layers of the FIFO reduces the time taken to read multiple data. This is because the read cycle does not generate EOC or INT nor does it carry out any conversion.

Figure 4. TLC2554/TLC2558 Continuous FIFO Read Cycle (FS = 1) (controlled by SCLK, SCLK can stop between each 16 SCLKs)

#### write cycle (write CFR)

The write cycle is used to write to the configuration register CFR (with 12-bit register content). The write cycle does not generate an EOC or INT nor does it carry out any conversion.

Figure 5. TLC2554/TLC2558 Write Cycle (FS active)

Figure 6. TLC2554/TLC2558 Write Cycle (FS = 1)

SLAS220A – JUNE 1999

#### conversion cycles

Figure 7. Mode 00 Single Shot/Normal Sampling (FS signal used)

#### conversion cycles (continued)

<sup>†</sup> This is one of the single shot commands. Conversion starts on next rising edge of CSTART.

#### Figure 9. Mode 00 Single Shot/Extended Sampling (FS signal used, FS pin connected to TMS320 DSP)

#### CS used as FS input

When interfacing with the TMS320 DSP using conversion mode 00, the FSR signal from the DSP may be connected to the CS input if this is the only device on the serial port. This will save one output pin from the DSP. Output data is made available on the rising edge of SCLK and input data is latched on the rising edge of SCLK in this case.

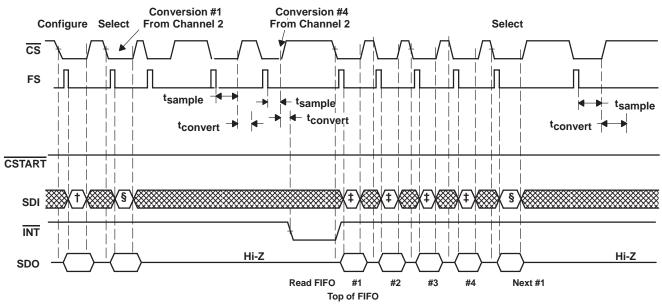

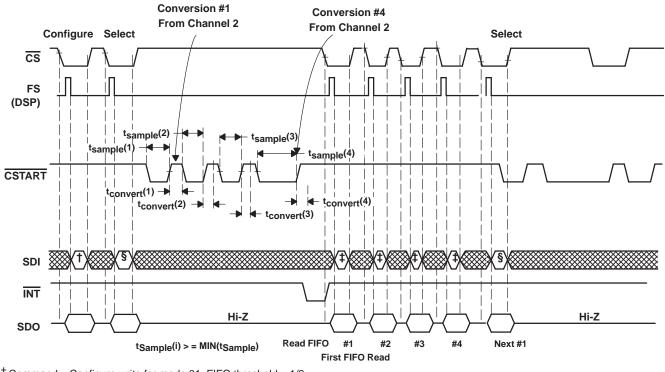

#### modes using the FIFO: modes 01, 10, 11 timing

Modes 01, 10, and 11 timing are very similar except for how and when the FIFO is read, how the device is configured, and how channel(s) are selected.

Mode 01 (repeat mode) requires a two-cycle configuration where the first one sets the mode and the second one selects the channel. Once the FIFO is filled up to the threshold programmed, it has the option to either read the FIFO or configure for other modes. Therefore, the sequence is either configure: select : triggered conversions : FIFO read : select : triggered conversions : FIFO read or configure : select : triggered conversions : configure : .... Each configure clears the FIFO and the action that follows the configure command depends on the mode setting of the device.

#### modes using the FIFO: modes 01, 10, 11 timing (continued)

<sup>†</sup>Command = Configure write for mode 01, FIFO threshold = 1/2

<sup>‡</sup>Command = Read FIFO, 1st FIFO read

§ Command = Select ch2.

<sup>†</sup> Command = Configure write for mode 01, FIFO threshold = 1/2

‡ Command = Read FIFO. 1st FIFO read

§ Command = Select ch2.

Figure 11. TLC2554/TLC2558 Mode 01 μp/DSP Serial Interface (conversions triggered by CSTART)

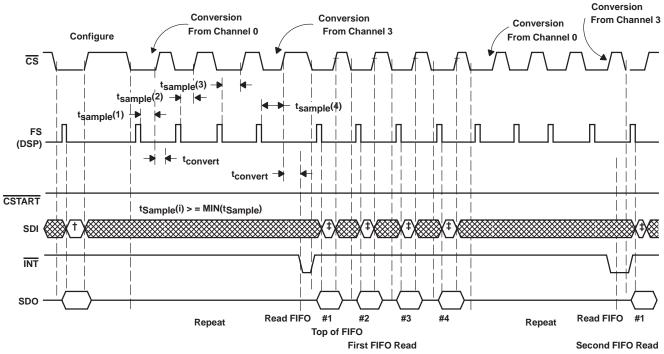

#### modes using the FIFO: modes 01, 10, 11 timing (continued)

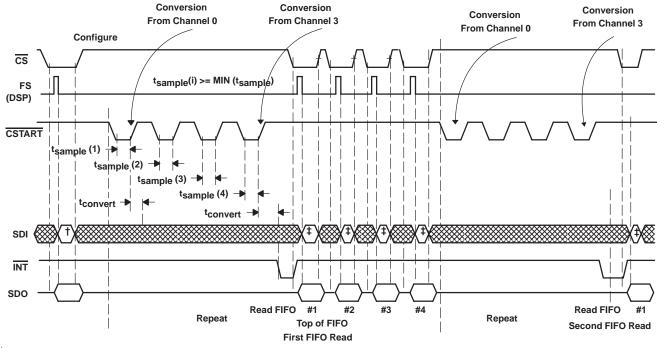

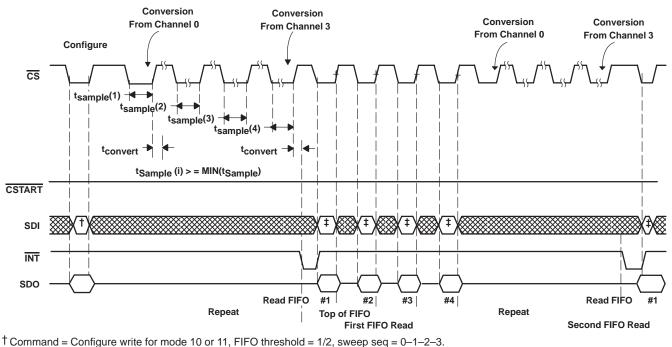

Mode 10 (sweep mode) requires reconfiguration at the start of each new sweep sequence. Once the FIFO is filled up to the programmed threshold, the host has the option to either read the FIFO or configure for other modes. Once the FIFO is read, the host must reconfigure the device before the next sweep sequence can be started. So the sequence is either configure : triggered conversions : FIFO read : configure. or configure : triggered conversions : configure : .... Each configure clears the FIFO and the action that follows the configure command depends on the mode setting of the device.

Mode 11 (repeat sweep mode) requires one cycle configuration. This sweep sequence can be repeated without reconfiguration. Once the FIFO is filled up to the programmed threshold, the host has the option to either read the FIFO or configure for other modes. So the sequence is either configure : triggered conversions : FIFO read : triggered conversions : FIFO read ... or configure : triggered conversions : configure : .... Each configure clears the FIFO and the action that follows the configure command depends on the mode setting of the device.

<sup>†</sup> Command = Configure write for mode 10 or 11, FIFO threshold = 1/2, sweep seq = 0-1-2-3. <sup>‡</sup> Command = Read FIFO

#### Figure 12. TLC2554/TLC2558 Mode 10/11 DSP Serial Interface (conversions triggered by FS)

#### modes using the FIFO: modes 01, 10, 11 timing (continued)

<sup>&</sup>lt;sup>†</sup> Command = Configure write for mode 10 or 11, FIFO threshold = 1/2, sweep seq = 0-1-2-3. ‡ Command = Read FIFO

#### Figure 13. TLC2554/TLC2558 Mode 10/11 DSP Serial Interface (conversions triggered by CSTART)

‡ Command = Read FIFO

#### **FIFO** operation

**FIFO Threshold Pointer**

Figure 15. TLC2554/TLC2558 FIFO

The device has an 8 layer FIFO that can be programmed for different thresholds. An interrupt is sent to the host after the preprogrammed threshold is reached. The FIFO can be used to store data from either a fixed channel or a series of channels based on a preprogrammed sweep sequence. For example, an application may require eight measurements from channel 3. In this case, the FIFO is filled with 8 data sequentially taken from channel 3. Another application may require data from channel 0, channel 2, channel 4, and channel 6 in an orderly manner. Therefore, the threshold is set for 1/2 and the sweep sequence 0-2-4-6-0-2-4-6 is chosen. An interrupt is sent to the host as soon as all four data are in the FIFO.

#### SCLK and conversion speed

There are multiple ways to adjust the conversion speed. The maximum equivalent conversion clock ( $f_{SCLK}$ /DIV) should not exceed 10 MHz.

• The SCLK is used as the source of the conversion clock and 14 conversion clocks are required to complete a conversion plus 4 SCLKs overhead.

The devices can operate with an SCLK up to 20 MHz for the supply voltage range specified. The clock divider provides speed options appropriate for an application where a high speed SCLK is used for faster I/O. The total conversion time is  $14 \times (DIV/f_{SCLK})$  where DIV is 1 or 2. For example a 20-MHz SCLK with the divide by 2 option produces a { $14 \times (2/20 \text{ M}) + 4 \times (1/20 \text{ MHz})$ } = 1.6 µs conversion time.

Auto power down can be used. This mode is always on. If the device is not accessed (by CS or CSTART), the converter is powered down to save power. The built-in reference is left on in order to quickly resume operation within one half SCLK period. This provides unlimited choices to trade speed with power savings.

#### reference voltage

The device has a built-in reference with a level of 4 V. If the internal reference is used, REFP is set to 4 V and REFM is set to 0 V. An external reference can also be used through two reference input pins, REFP and REFM, if the reference source is programmed as external. The voltage levels applied to these pins establish the upper and lower limits of the analog inputs to produce a full-scale and zero-scale reading respectively. The values of REFP, REFM, and the analog input should not exceed the positive supply or be lower than GND consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REFP and at zero when the input signal is equal to or lower than REFM.

#### **FIFO** operation (continued)

#### power down

Writing 8000h to the device puts the device into a software power-down state. For a hardware power down, the dedicated PWDN pin provides another way to power down the device asynchronously. These two power-down modes power down the entire device including the built-in reference to save power. It requires 20 ms to resume from either a software or hardware power down.

Auto power down mode is always enabled. This mode maintains the built-in reference if an internal reference is used, so resumption is fast enough to be used between cycles.

The configuration register is not affected by any of the power down modes but the sweep operation sequence has to be started over again. All FIFO contents are cleared by the power-down modes.

#### power up and initialization

Initialization requires:

- 1. Determine processor type by writing A000h to the TLC2554/58

- 2. Configure the device

The first conversion after power up or resuming from power down is not valid.

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage range, GND to V <sub>CC</sub>                       |                |

|--------------------------------------------------------------------|----------------|

| Reference input voltage                                            |                |

| Digital input voltage range                                        |                |

| Operating virtual junction temperature range, T <sub>J</sub>       | –40°C to 150°C |

| Operating free-air temperature range, T <sub>A</sub> : TLC2554/58C | 0°C to 70°C    |

| TLC2554/58I                                                        | –40°C to 85°C  |

| Storage temperature range, T <sub>stg</sub>                        |                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds       |                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                                                                  | MIN | NOM | MAX                  | UNIT |

|------------------------------------------------------------------|-----|-----|----------------------|------|

| Supply voltage, V <sub>CC</sub>                                  | 4.5 | 5   | 5.5                  | V    |

| Positive external reference voltage input, VREFP (see Note 1)    | 2   |     | VCC                  | V    |

| Negative external reference voltage input, VREFM (note Note 1)   | 0   |     | 2                    | V    |

| Differential reference voltage input, VREFP - VREFM (see Note 1) | 2   | VCC | V <sub>CC</sub> +0.2 | V    |

| Analog input voltage (see Note 1)                                | 0   |     | VCC                  | V    |

| High level control input voltage, VIH                            | 2.1 |     |                      | V    |

| Low-level control input voltage, VIL                             |     |     | 0.6                  | V    |

| Rise time, for CS, CSTART SDI at 0.5 pF, t <sub>r(I/O)</sub>     |     |     | 4.76                 | ns   |

| Fall time, for CS, CSTART SDI at 0.5 pF, t <sub>f(I/O)</sub>     |     |     | 2.91                 | ns   |

| Rise time, for INT, EOC, SDO at 30 pF, t <sub>r(Output)</sub>    |     |     | 2.43                 | ns   |

| Fall time, for INT, EOC, SDO at 30 pF, t <sub>f(Output)</sub>    |     |     | 2.3                  | ns   |

NOTE 1: When binary output format is used, analog input voltages greater than that applied to REFP convert as all ones (1111111111), while input voltages less than that applied to REFM convert as all zeros (00000000000). The device is functional with reference down to 2 V (VREFP – VREFM –1); however, the electrical specifications are no longer applicable.

SLAS220A – JUNE 1999

#### recommended operating conditions (continued)

|                                                                                                                                 |                                                              | MIN | NOM | MAX      | UNIT  |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|----------|-------|

| Transition time, for FS, SCLK, SDI, tt(CLK)                                                                                     |                                                              | 0.5 |     |          | SCLK  |

| Setup time, CS falling edge before SCLK rising edge (FS=1) or before S <sup>t</sup> su(CS-SCLK)                                 | CLK falling edge (when FS is active),                        | 0.5 |     |          | SCLK  |

| Hold time, CS rising edge after SCLK rising edge (FS=1) or after SC $^{t}h(SCLK-CS)$                                            | LK falling edge (when FS is active),                         | 5   |     |          | ns    |

| Delay time, delay from CS falling edge to FS rising edge, td(CSL-FSH                                                            | H)                                                           | 0.5 |     | 7        | SCLKs |

| Delay time, delay time from 16th SCLK falling edge to CS rising edge                                                            | e (FS is active), t <sub>d</sub> (SCLK16F-CSH)               | 0.5 |     |          | SCLKs |

| Setup time, FS rising edge before SCLK falling edge, t <sub>SU(FSH-SCLKI</sub>                                                  | F)                                                           |     |     | 0.5      | SCLKs |

| Hold time, FS hold high after SCLK falling edge, th(FSH-SCLKF)                                                                  |                                                              | 0.5 |     |          | SCLKs |

| Pulse width, CS high time, t <sub>wH(CS)</sub>                                                                                  |                                                              | 100 |     |          | ns    |

| SCLK cycle time, V <sub>CC</sub> = 2.7 V to 3.6V, t <sub>c(SCLK)</sub>                                                          |                                                              | 67  |     |          | ns    |

| SCLK cycle time, $V_{CC} = 4.5 V$ to 5.5V, $t_{C(SCLK)}$                                                                        |                                                              | 50  |     |          | ns    |

| Pulse width, SCLK low time, twL(SCLK)                                                                                           |                                                              | 20  |     | 30       | ns    |

| Pulse width, SCLK high time, twH(SCLK)                                                                                          |                                                              | 20  |     | 30       | ns    |

| Setup time, SDI valid before falling edge of SCLK (FS is active) o<br>tsu(DI-SCLK)                                              | r the rising edge of SCLK (FS=1),                            |     |     | 25       | ns    |

| Hold time, SDI hold valid after falling edge of SCLK (FS is active) of th(DI-SCLK)                                              | or the rising edge of SCLK (FS=1),                           | 5   |     |          | ns    |

| Delay time, delay from CS falling edge to SDO valid, td(CSL-DOV)                                                                | r from CS falling edge to SDO valid, t <sub>d(CSL-DOV)</sub> |     |     |          | ns    |

| Delay time, delay from FS falling edge to SDO valid, t <sub>d(FSL-DOV)</sub>                                                    |                                                              | 1   |     | 25       | ns    |

| Delay time, delay from SCLK rising edge (FS is active) or SCLK falling edge                                                     | dge (FS=1) SDO valid, t <sub>d(CLK-DOV)</sub>                | 1   |     | 25       | ns    |

| Delay time, delay from CS rising edge to SDO 3-stated, td(CSH-DOZ                                                               | ()                                                           | 1   |     | 25       | ns    |

| Delay time, delay from 16th SCLK falling edge (FS is active) or the 16 edge, td(CLK-EOCL)                                       | th rising edge (FS=1) to EOC falling                         | 1   |     | 25       | ns    |

| Delay time, delay from EOC rising edge to SDO 3-stated if CS is low,                                                            | <sup>t</sup> d(EOCH-DOZ)                                     | 1   |     | 50       | ns    |

| Delay time, delay from 16th SCLK rising edge to INT falling edge (FS = $to$ INT falling edge (when FS active), $t_d(SCLK-INTL)$ | 1) or from the 16th falling edge SCLK                        |     |     | 3.5      | μs    |

| Delay time, delay from CS falling edge to INT rising edge, td(CSL-INTH)                                                         |                                                              | 1   |     | 50       | ns    |

| Delay time, delay from CS rising edge to CSTART falling edge, td(CSH-CSTARTL)                                                   |                                                              |     |     |          | ns    |

| Delay time, delay from CSTART rising edge to EOC falling edge, td(CSTARTH-EOCL)                                                 |                                                              | 1   |     | 50       | ns    |

| Pulse width, CSTART low time, t <sub>wL</sub> (CSTART)                                                                          |                                                              | 0.8 |     |          | μs    |

| Delay time, delay from CS rising edge to EOC rising edge, td(CSH-EOCH)                                                          |                                                              |     |     | 50       | ns    |

| Delay time, delay from CSTART rising edge to CSTART falling edge, t <sub>d</sub> (CSTARTH-CSTARTL)                              |                                                              | 3.6 |     |          | μs    |

| Delay time, delay from CSTART rising edge to INT falling edge, td(CS                                                            |                                                              | 3.5 |     |          | μs    |

|                                                                                                                                 | TLC2554C/TLC2558C                                            | 0   |     | 70<br>85 | °C    |

| Operating free-air temperature, T <sub>A</sub>                                                                                  | TLC2554I/TLC2558I                                            | -40 |     |          |       |

NOTE 2: This is the time required for the clock input signal to fall from VIH max or to rise from VIL max to VIH min. In the vicinity of normal room temperature, the devices function with input clock transition time as slow as 1 µs for remote data-acquisition applications where the sensor and A/D converter are placed several feet away from the controlling microprocessor.

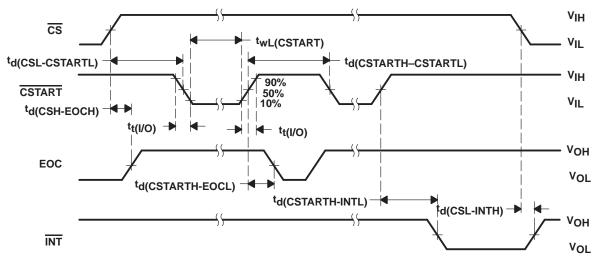

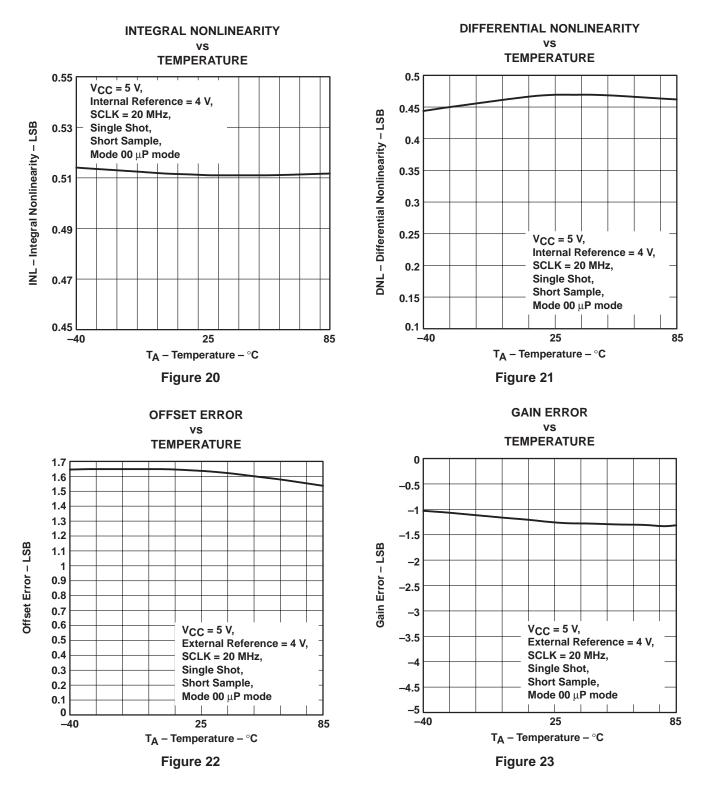

# electrical characteristics over recommended operating free-air temperature range, $V_{CC} = V_{REFP} = 4.5$ V to 5.5 V, SCLK frequency = 20 MHz at 5 V, (unless otherwise noted)

|                     | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TEST C                                                                      | ONDITIONS                                                                                                      | MIN | TYP†                                                                              | MAX  | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------|------|------|

| V <sub>OH</sub>     | High-level output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>CC</sub> = 5.5 V, I <sub>OH</sub> = -                                | -20 μA at 30 pF load                                                                                           | 2.4 |                                                                                   |      | V    |

| V <sub>OL</sub>     | Low-level output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 5.5 V, I <sub>OL</sub> = 2                                | 20 μA at 30 pF load                                                                                            |     |                                                                                   | 0.4  | V    |

|                     | ZOff-state output current<br>(high-impedance-state) $V_0 = V_{CC}$<br>$V_0 = 0$ $\overline{CS} = V_{CC}$ 1High-level input current $V_1 = V_{CC}$ 0.005Low-level input current $V_1 = 0$ V-0.005COperating supply current, normal sampling<br>(short) $\overline{CS}$ at 0 V, Ext ref $V_{CC} = 4.5$ V to 5.5 VCOperating supply current, extended sampling<br>(short) $\overline{CS}$ at 0 V, Ext ref $V_{CC} = 4.5$ V to 5.5 VCOperating supply current, extended sampling<br>(Short) $\overline{CS}$ at 0 V, Ext ref $V_{CC} = 4.5$ V to 5.5 VDOperating supply current, extended sampling<br>(S at 0 V, Int ref $V_{CC} = 4.5$ V to 5.5 V1.9COperating supply current $\overline{CS}$ at 0 V, Int ref $V_{CC} = 4.5$ V to 5.5 V2Internal reference supply current $\overline{CS}$ at 0 V, V <sub>CC</sub> = 4.5 V to 5.5 V22C(PD)Power-down supply current $\overline{CS}$ at 0 V, $V_{CC} = 4.5$ V to 5.5 V,<br>Ext clock0.1C(AUTOPWDN)Auto power-down current $\overline{CS}$ at 0 V, $V_{CC} = 4.5$ V to 5.5 V,<br>Ext clock, Ext ref0.1 | 1                                                                           | 2.5                                                                                                            |     |                                                                                   |      |      |

| I <sub>OZ</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{O} = 0$                                                                 | $CS = V_{CC}$                                                                                                  |     | -1                                                                                | -2.5 | μA   |

| IIH                 | High-level input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_I = V_{CC}$                                                              |                                                                                                                |     | 0.005                                                                             | 2.5  | μΑ   |

| Ι <sub>ΙL</sub>     | Low-level input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_I = 0 V$                                                                 |                                                                                                                |     | -0.005                                                                            | 2.5  | μΑ   |

|                     | Operating supply current, normal sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CS at 0 V, Ext ref                                                          | $V_{CC}$ = 4.5 V to 5.5 V                                                                                      |     |                                                                                   | 4    | mA   |

| ICC                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS at 0 V, Int ref                                                          | $V_{CC}$ = 4.5 V to 5.5 V                                                                                      |     | 0.4<br>1 2.5<br>1 -2.5<br>0.005 2.5<br>-0.005 2.5<br>4<br>6<br>1.9<br>2<br>2<br>2 | 6    | mA   |

|                     | On exercise a supply suggest extended compliant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS at 0 V, Ext ref                                                          | $V_{CC}$ = 4.5 V to 5.5 V                                                                                      |     | 1.9                                                                               |      | mA   |