SLWS225B - DECEMBER 2010 - REVISED MAY 2011

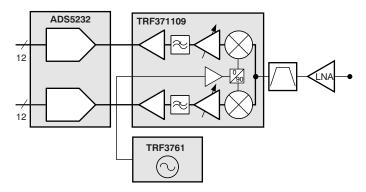

## **Direct Downconversion Receiver**

Check for Samples: TRF371109

## **FEATURES**

www.ti.com

- Frequency Range: 300 MHz to 1700 MHz

- Integrated Baseband Programmable Gain Amplifier

- On-Chip Programmable Baseband Filter

- High Cascaded IP3: 27 dBm at 900 MHz

- High IP2: 68 dBm at 900 MHz

- Hardware and Software Power Down

- Three-Wire Serial Interface

- Single Supply: 4.5-V to 5.5-V Operation

- Silicon Germanium Technology

## **APPLICATIONS**

- Multicarrier Wireless Infrastructure

- WiMAX

- High-Linearity Direct-Downconversion Receiver

- LTE (Long Term Evolution)

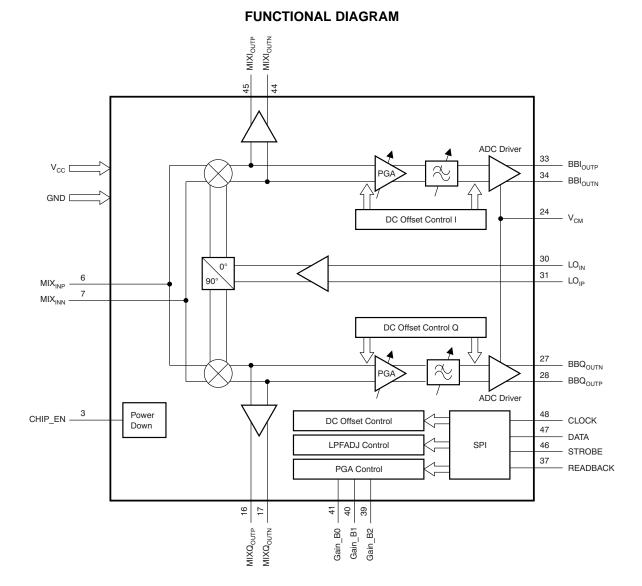

## DESCRIPTION

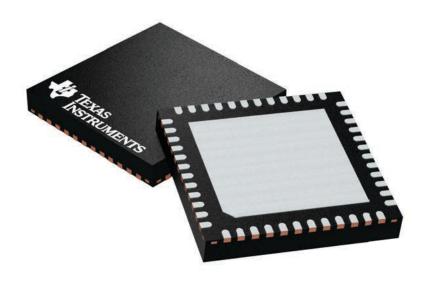

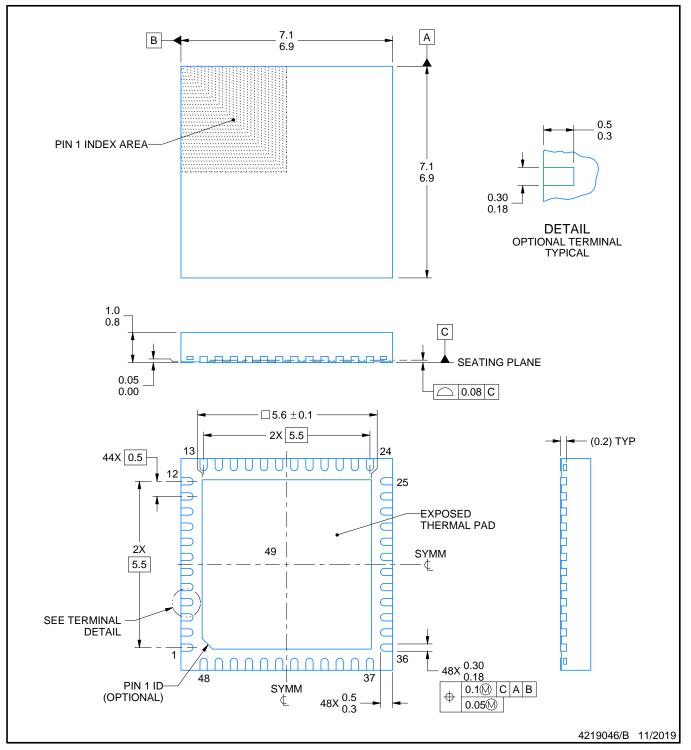

The TRF371109 is a highly linear direct-conversion quadrature receiver. The TRF371109 integrates balanced I and Q mixers, LO buffers, and phase splitters to convert an RF signal directly to I and Q baseband. The on-chip programmable gain amplifiers allow adjustment of the output signal level without the need for external variable gain (attenuator) devices. The TRF371109 integrates programmable baseband low-pass filters that attenuate nearby interference, eliminating the need for an external baseband filter.

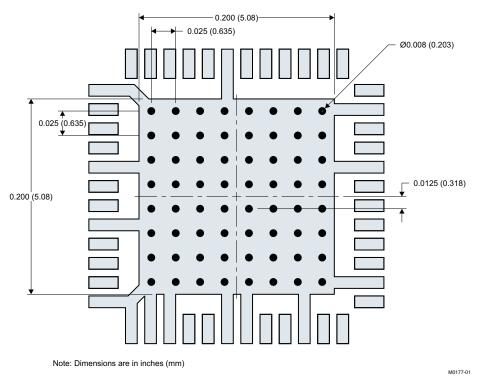

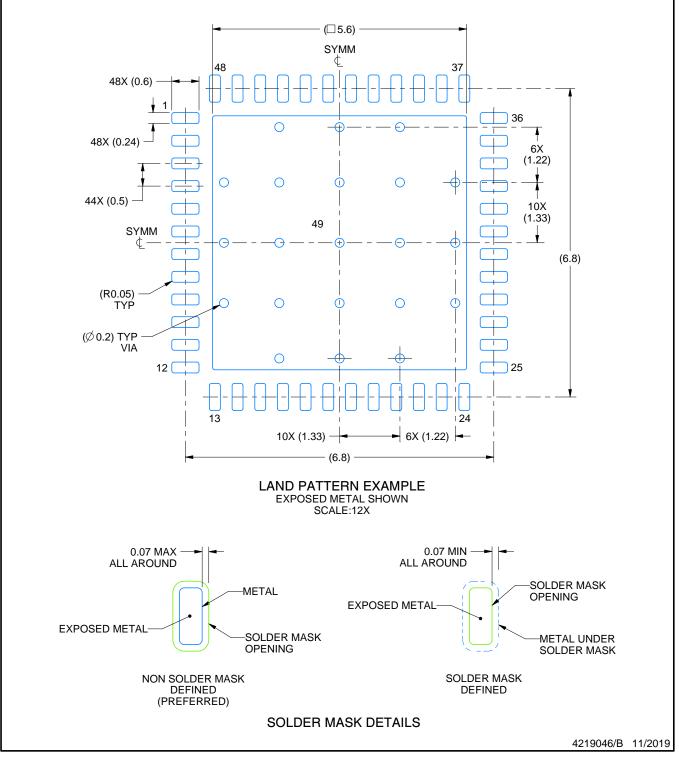

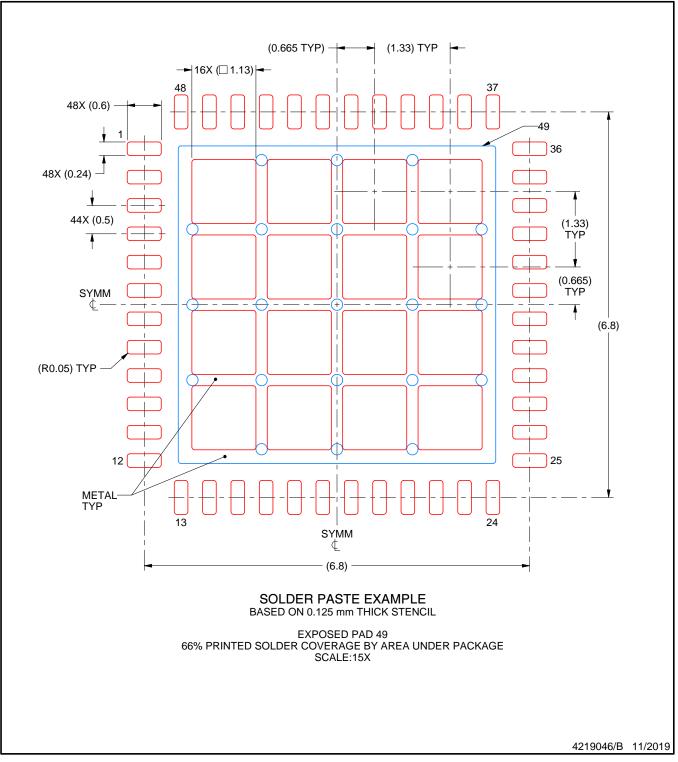

Housed in a 7-mm × 7-mm VQFN package, the TRF371109 provides the smallest and most integrated receiver solution available for high-performance equipment.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

### SLWS225B-DECEMBER 2010-REVISED MAY 2011

Real Providence

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### AVAILABLE DEVICE OPTIONS<sup>(1)</sup>

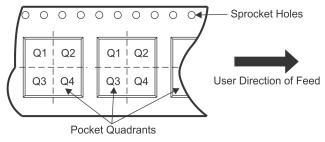

| PRODUCT   | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

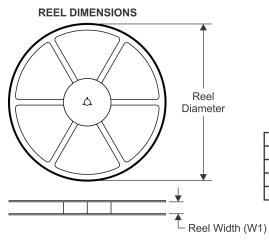

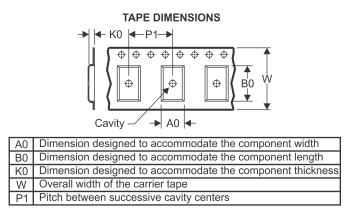

| TRF371109 | VQFN-48          | RGZ                   | –40°C to +85°C                    | TRF371109IRGZ      | TRF371109IRGZR     | Tape and Reel, 2500          |

| 18571109  | v QFIN-40        | RGZ                   | -40 C 10 +65 C TRF37 T 109IRG2    |                    | TRF371109IRGZT     | Tape and Reel, 250           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the device product folder at www.ti.com.

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted).<sup>(1)</sup>

|                                                              | VALUE                        | UNIT |

|--------------------------------------------------------------|------------------------------|------|

| Supply voltage range <sup>(2)</sup>                          | -0.3 to 5.5                  | V    |

| Digital I/O voltage range                                    | –0.3 to V <sub>CC</sub> +0.5 | V    |

| Operating virtual junction temperature range, T <sub>J</sub> | -40 to +150                  | °C   |

| Operating ambient temperature range, T <sub>A</sub>          | -40 to +85                   | °C   |

| Storage temperature range, T <sub>stg</sub>                  | -65 to +150                  | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

## **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted).

|                |                                              | MIN | NOM | MAX  | UNIT         |

|----------------|----------------------------------------------|-----|-----|------|--------------|

| $V_{CC}$       | Power-supply voltage                         | 4.5 | 5.0 | 5.5  | V            |

|                | Power-supply voltage ripple                  |     |     | 940  | $\mu V_{PP}$ |

| T <sub>A</sub> | Operating free-air temperature range         | -40 |     | +85  | °C           |

| TJ             | Operating virtual junction temperature range | -40 |     | +150 | °C           |

## THERMAL CHARACTERISTICS

Over recommended operating free-air temperature range (unless otherwise noted).

|                       | PARAMETER <sup>(1)</sup>                      | TEST CONDITIONS                | MIN  | TYP  | MAX | UNIT |

|-----------------------|-----------------------------------------------|--------------------------------|------|------|-----|------|

| R <sub>θJA</sub>      |                                               | Soldered slug, no airflow      |      | 26   |     |      |

|                       | The second second second second second second | Soldered slug, 200-LFM airflow | 20.1 |      |     | °C/W |

|                       | Thermal resistance, junction-to-ambient       | Soldered slug, 400-LFM airflow |      | 17.4 |     | C/vv |

| $R_{\theta JA}^{(2)}$ |                                               | 7-mm × 7-mm, 48-pin PDFP       | 25   |      | ]   |      |

| $R_{\theta JB}$       | Thermal resistance, junction-to-board         | 7-mm × 7-mm 48-pin PDFP        |      | 12   |     | °C/W |

(1) Determined using JEDEC standard JESD-51 with high-K board

(2) 16 layers, high-K board

## THERMAL INFORMATION

|                    |                                              | TRF371109 |          |

|--------------------|----------------------------------------------|-----------|----------|

|                    | THERMAL METRIC <sup>(1)</sup>                | RGZ       | UNITS    |

|                    |                                              | 48 PINS   | _        |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance       | 26.9      |          |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 11.2      |          |

| $\theta_{JB}$      | Junction-to-board thermal resistance         | 3.4       | °C () () |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 0.2       | °C/W     |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 3.4       | _        |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | 0.6       | _        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

SLWS225B-DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

At  $V_{CC}$  = 5 V, LO power = 0 dBm, and  $T_A$  = +25°C,unless otherwise noted.

|                     | PARAMETERS                                                       | TEST CONDITIONS                                                   | MIN                   | TYP  | MAX                   | UNIT        |

|---------------------|------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------|------|-----------------------|-------------|

| DC PARA             | METERS                                                           |                                                                   |                       |      |                       |             |

| I <sub>CC</sub>     | Total supply current                                             |                                                                   |                       | 360  |                       | mA          |

|                     | Power-down current                                               |                                                                   |                       | 2    |                       | mA          |

| IQ DEMOI            | DULATOR AND BASEBAND SECTION                                     |                                                                   |                       |      |                       |             |

| f <sub>RF</sub>     | Frequency range                                                  |                                                                   | 300                   |      | 1700                  | MHz         |

|                     | Gain range                                                       |                                                                   | 22                    | 24   |                       | dB          |

|                     | Gain step                                                        | See <sup>(1)</sup>                                                |                       | 1    |                       | dB          |

| Pin <sub>Max</sub>  | Maximum RF power input                                           | Before damage                                                     |                       | 25   |                       | dBm         |

| OIP3                |                                                                  | Gain setting = 24 <sup>(2)</sup>                                  |                       | 30   |                       | $dBV_{RMS}$ |

| P1dB <sub>Min</sub> |                                                                  | One tone <sup>(3)</sup>                                           |                       | 3    |                       | $dBV_{RMS}$ |

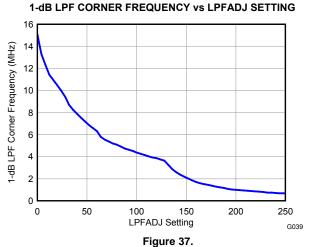

| f <sub>Min</sub>    | Minimum baseband low-pass filter (LPF) cutoff frequency          | 1-dB point <sup>(4)</sup>                                         |                       | 700  |                       | kHz         |

| f <sub>Max</sub>    | Maximum baseband LPF cutoff<br>frequency                         | 3-dB point <sup>(4)</sup>                                         | 15                    |      |                       | MHz         |

| f <sub>Bypass</sub> | Baseband LPF cutoff frequency in<br>bypass mode                  | 3-dB point <sup>(5)</sup>                                         |                       | 30   |                       | MHz         |

|                     |                                                                  | 1 × f <sub>C</sub>                                                |                       | 1    |                       | dB          |

|                     |                                                                  | 1.5 × f <sub>C</sub>                                              |                       | 8    |                       | dB          |

| F                   | Baseband relative attenuation at                                 | 2 × f <sub>C</sub>                                                |                       | 32   |                       | dB          |

| F <sub>sel</sub>    | LPF cutoff frequency $(f_C)^{(6)}$                               | 3 × f <sub>C</sub>                                                |                       | 54   |                       | dB          |

|                     |                                                                  | $4 \times f_{C}$                                                  |                       | 75   |                       | dB          |

|                     |                                                                  | 5 × f <sub>C</sub>                                                |                       | 90   |                       | dB          |

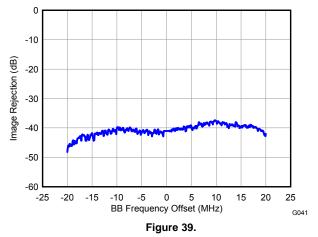

|                     | Image suppression                                                |                                                                   |                       | -40  |                       | dB          |

|                     | Output BB attenuator                                             |                                                                   |                       | 3    |                       | dB          |

|                     | $\mathbf{O}$ that the ord interval $\mathbf{O}$ and $\mathbf{O}$ | Parallel resistance                                               |                       | 1    |                       | kΩ          |

|                     | Output load impedance <sup>(7)</sup>                             | Parallel capacitance                                              |                       | 20   |                       | pF          |

| V <sub>CM</sub>     | Output, common-mode                                              | Measured at I- and Q-channel baseband outputs                     |                       | 1.5  |                       | V           |

|                     |                                                                  | Second harmonic <sup>(8)</sup>                                    |                       | -100 |                       | dBc         |

|                     | Baseband harmonic level                                          | Third harmonic <sup>(8)</sup>                                     |                       | -93  |                       | dBc         |

| LOCAL O             | SCILLATOR PARAMETERS                                             |                                                                   |                       |      |                       |             |

|                     | Local oscillator frequency                                       |                                                                   | 300                   |      | 1700                  | MHz         |

|                     | LO input level                                                   | See <sup>(9)</sup>                                                | -3                    | 0    | 6                     | dBm         |

|                     | LO leakage                                                       | At MIX <sub>INN</sub> /MIX <sub>INP</sub> at 0-dBm LO drive level |                       | -58  |                       | dBm         |

| DIGITAL I           | NTERFACE                                                         |                                                                   |                       |      |                       |             |

| V <sub>IH</sub>     | High-level input voltage                                         |                                                                   | $0.6 \times V_{CC}$   | 5    | V <sub>CC</sub>       | V           |

| VIL                 | Low-level input voltage                                          |                                                                   | 0                     |      | 0.8                   | V           |

| V <sub>OH</sub>     | High-level output voltage                                        |                                                                   | 0.8 × V <sub>CC</sub> |      |                       | V           |

| V <sub>OL</sub>     | Low-level output voltage                                         |                                                                   |                       |      | 0.2 × V <sub>CC</sub> | V           |

(1) Two consecutive gain settings.

(2) Two CW tones at an offset from LO frequency smaller than the baseband-filter cutoff frequency. Performance is set by baseband circuitry regardless of LO frequency.

(3) Single CW tone at an offset from LO frequency smaller than the baseband-filter cutoff frequency. Performance is set by baseband circuitry regardless of LO frequency.

(4) Baseband low-pass filter cutoff frequency is programmable through SPI register LPFADJ. LPFADJ = 0 corresponds to max bandwidth; LPFADJ = 255 corresponds to minimum BW.

(5) Filter Ctrl setting equal to 0.

(6) Attenuation relative to passband gain.

(7) The typical value for this parameter is the load impedance that the device is able to drive.

(8) LO frequency set to 900 MHz. Power-in set to -40 dBm. Gain setting at 24. DC offset calibration engaged. Input signal set at 2.5-MHz offset.

(9) LO power outside of this range is possible but may introduce degraded performance.

SLWS225B - DECEMBER 2010 - REVISED MAY 2011

#### www.ti.com

## ELECTRICAL CHARACTERISTICS (continued)

At  $V_{CC}$  = 5 V, LO power = 0 dBm, and  $T_A$  = +25°C,unless otherwise noted.

|                       | PARAMETERS                         | TEST CONDITIONS                       | MIN TYP MAX | UNIT |

|-----------------------|------------------------------------|---------------------------------------|-------------|------|

| f <sub>LO</sub> = 300 | ) MHz <sup>(10)</sup>              |                                       |             | 1    |

| G <sub>Max</sub>      | Maximum gain <sup>(11)</sup>       |                                       |             | dB   |

| NF                    | Noise figure                       | Gain setting = 24                     | 8.7         | dB   |

| IIP3                  | Third-order input intercept point  | Gain setting = 24 <sup>(12)(13)</sup> | 13.9        | dBm  |

| IIP2                  | Second-order input intercept point | Gain setting = $24^{(13)(14)}$        | 45          | dBm  |

| f <sub>LO</sub> = 700 | ) MHz <sup>(10)</sup>              |                                       |             |      |

| G <sub>Max</sub>      | Maximum gain <sup>(11)</sup>       | Gain setting = 24                     | 43          | dB   |

| NF                    | Noise figure                       | Gain setting = 24                     | 10.7        | dB   |

| IIP3                  | Third-order input intercept point  | Gain setting = $24^{(12)(13)}$        | 25          | dBm  |

| IIP2                  | Second-order input intercept point | Gain setting = $24^{(13)(14)}$        | 70          | dBm  |

| f <sub>LO</sub> = 900 | ) MHz <sup>(10)</sup>              |                                       |             |      |

| G <sub>Max</sub>      | Maximum gain <sup>(11)</sup>       | Gain setting = 24                     | 41          | dB   |

|                       |                                    | Gain setting = 24                     | 12.4        | dB   |

| NF                    | Noise figure                       | Gain setting = 16                     | 14.8        | dB   |

| IIP3                  | Third-order input intercept point  | Gain setting = $24^{(12)(13)}$        | 27          | dBm  |

| IIP2                  | Second-order input intercept point | Gain setting = $24^{(13)(14)}$        | 68          | dBm  |

| f <sub>LO</sub> = 142 | 25 MHz <sup>(10)</sup>             |                                       |             |      |

| G <sub>Max</sub>      | Maximum gain <sup>(11)</sup>       | Gain setting = 24                     | 36.9        | dB   |

| NF                    | Noise figure                       | Gain setting = 24                     | 15.5        | dB   |

| IIP3                  | Third-order input intercept point  | Gain setting = 24 <sup>(12)(13)</sup> | 27          | dBm  |

| IIP2                  | Second-order input intercept point | Gain setting = $24^{(13)(14)}$        | 65          | dBm  |

| f <sub>LO</sub> = 170 | 00 MHz <sup>(10)</sup>             |                                       |             |      |

| G <sub>Max</sub>      | Maximum gain <sup>(11)</sup>       | Gain setting = 24 35.9                |             | dB   |

| NF                    | Noise figure                       | Gain setting = 24                     | 17.5        | dB   |

| IIP3                  | Third-order input intercept point  | Gain setting = $24^{(12)(13)}$        | 25.5        | dBm  |

| IIP2                  | Second-order input intercept point | Gain setting = $24^{(13)(14)}$        | 60          | dBm  |

(10) For broadband frequency sweeps, the Picosecond balun (model #5310A) is used at the RF and LO input. For frequency bands between 600 MHz and 1250 MHz, the Murata balun LDB21897M005C-001 is used. Performance parameters adjusted for balun insertion loss. Recommended baluns for respective frequency band are listed:

700 MHz and 900 MHz: Murata LDB21897M005C-001 (or equivalent)

1740 MHz: Murata LDB211G8005C-001 (or equivalent)

1950 MHz: Murata LDB211G9005C-001 (or equivalent)

2025 MHz: Murata LDB211G9005C-001 (or equivalent)

2500 MHz: Murata LDB212G4005C-001 (or equivalent)

3500 MHz: Johanson 3600BL14M050E (or equivalent)

(11) Gain defined as voltage gain from MIX<sub>IN</sub> (V<sub>RMS</sub>) to either baseband output: BBI/Q<sub>OUT</sub> (V<sub>RMS</sub>) (12) Two CW tones of -30 dBm at  $f_{RF1} = f_{LO} \pm (2 \bullet f_c)$  and  $f_{RF2} = f_{LO} \pm [(4 \bullet f_c) + 100 \text{ kHz}]$ ;  $f_c =$  Baseband filter 1-dB cutoff frequency.

(13) Because the two-tone interference sources are outside of the baseband filter bandwidth, the results are inherently independent of the gain setting. Intermodulation parameters are recorded at maximum gain setting, where measurement accuracy is best.

(14) Two CW tones at -30 dBm at  $f_{RF1} = f_{LO} \pm (2 \bullet f_c)$  and  $f_{RF2} = f_{LO} \pm [(2 \bullet f_c) + 100 \text{ kHz}]$ ; IM2 product measured at 100-kHz output frequency.  $f_C =$  Baseband filter 1-dB cutoff frequency.

SLWS225B-DECEMBER 2010-REVISED MAY 2011

www.ti.com

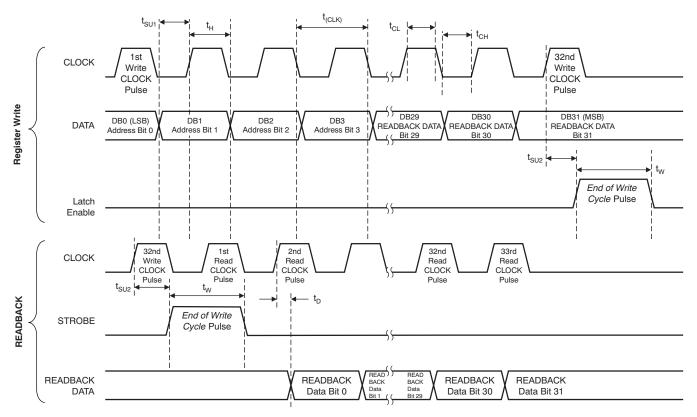

## TIMING REQUIREMENTS

At  $V_{CC}$  = 5 V, LO power = 0 dBm, and  $T_A$  = +25°C (unless otherwise noted).

|                    | PARAMETER           | TEST CONDITIONS | MIN | ΤΥΡ ΜΑΧ | UNIT |

|--------------------|---------------------|-----------------|-----|---------|------|

| t <sub>(CLK)</sub> | Clock period        |                 | 50  |         | ns   |

| t <sub>SU1</sub>   | Setup time, data    |                 | 10  |         | ns   |

| t <sub>H</sub>     | Hold time, data     |                 | 10  |         | ns   |

| t <sub>W</sub>     | Pulse width, STROBE |                 | 20  |         | ns   |

| t <sub>SU2</sub>   | Setup time, STROBE  |                 | 10  |         | ns   |

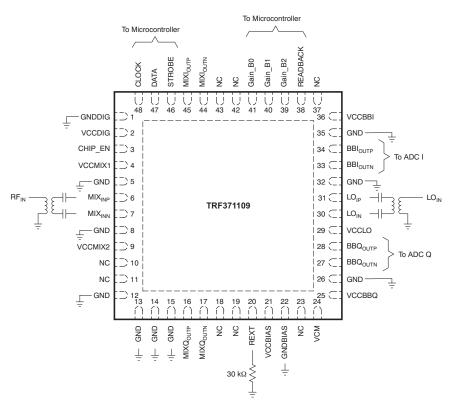

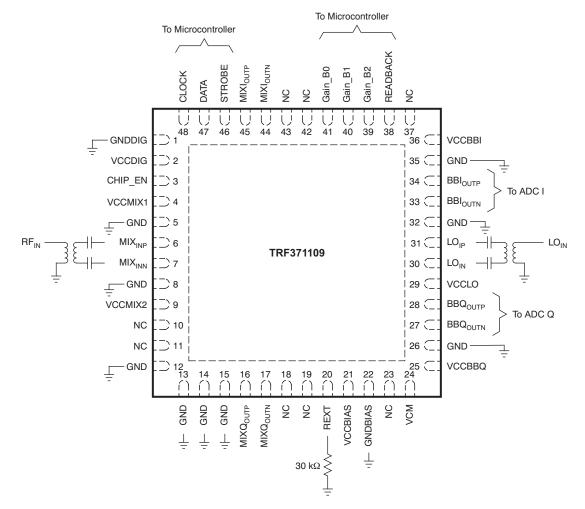

## **DEVICE INFORMATION**

## **PIN ASSIGNMENTS**

www.ti.com

### SLWS225B - DECEMBER 2010 - REVISED MAY 2011

### **PIN FUNCTIONS**

|     | PIN                  | 1/0 | DESCRIPTION                                          |  |

|-----|----------------------|-----|------------------------------------------------------|--|

| NO. | NAME                 | 1/0 | DESCRIPTION                                          |  |

| 1   | GNDDIG               |     | Digital ground                                       |  |

| 2   | VCCDIG               |     | Digital power supply                                 |  |

| 3   | CHIP_EN              | I   | Chip enable                                          |  |

| 4   | VCCMIX1              |     | Mixer power supply                                   |  |

| 5   | GND                  |     | Ground                                               |  |

| 6   | MIX <sub>INP</sub>   | I   | Mixer input: positive terminal                       |  |

| 7   | MIX <sub>INN</sub>   | I   | Mixer input: negative terminal                       |  |

| 8   | GND                  |     | Ground                                               |  |

| 9   | VCCMIX2              |     | Mixer power supply                                   |  |

| 10  | NC                   |     | No connect                                           |  |

| 11  | NC                   |     | No connect                                           |  |

| 12  | GND                  |     | Ground                                               |  |

| 13  | GND                  |     | Ground                                               |  |

| 14  | GND                  |     | Ground                                               |  |

| 15  | GND                  |     | Ground                                               |  |

| 16  | MIXQ <sub>OUTP</sub> | 0   | Mixer Q output: positive terminal (test pin)         |  |

| 17  | MIXQ <sub>OUTN</sub> | 0   | Mixer Q output: negative terminal (test pin)         |  |

| 18  | NC                   |     | No connect                                           |  |

| 19  | NC                   |     | No connect                                           |  |

| 20  | REXT                 | 0   | Reference bias external resistor                     |  |

| 21  | VCCBIAS              |     | Bias block power supply                              |  |

| 22  | GNDBIAS              |     | Bias block ground                                    |  |

| 23  | NC                   |     | No connect                                           |  |

| 24  | VCM                  | I   | Baseband input common-mode voltage                   |  |

| 25  | VCCBBQ               |     | Baseband Q chain power supply                        |  |

| 26  | GND                  |     | Ground                                               |  |

| 27  | BBQ <sub>OUTN</sub>  | 0   | Baseband Q (in quadrature) output: negative terminal |  |

| 28  | BBQ <sub>OUTP</sub>  | 0   | Baseband Q (in quadrature) output: positive terminal |  |

| 29  | VCCLO                |     | Local oscillator power supply                        |  |

| 30  | LO <sub>IN</sub>     | I   | Local oscillator input: negative terminal            |  |

| 31  | LO <sub>IP</sub>     | I   | Local oscillator input: positive terminal            |  |

| 32  | GND                  |     | Ground                                               |  |

| 33  | BBI <sub>OUTN</sub>  | 0   | Baseband I (in-phase) output: positive terminal      |  |

| 34  | BBI <sub>OUTP</sub>  | 0   | Baseband I (in-phase) output: negative terminal      |  |

| 35  | GND                  |     | Ground                                               |  |

| 36  | VCCBBI               |     | Baseband I (in phase) power supply                   |  |

| 37  | NC                   |     | No connect                                           |  |

| 38  | READBACK             | 0   | SPI readback data                                    |  |

| 39  | Gain_B2              | I   | PGA fast gain control bit 2                          |  |

| 40  | Gain_B1              | I   | PGA fast gain control bit 1                          |  |

| 41  | Gain_B0              | I   | PGA fast gain control bit 0                          |  |

| 42  | NC                   |     | No connect                                           |  |

| 43  | NC                   |     | No connect                                           |  |

| 44  | MIXIOUTN             | 0   | Mixer I output: negative terminal                    |  |

| 45  | MIXIOUTP             | 0   | Mixer I output: positive terminal                    |  |

| 46  | STROBE               | I   | SPI enable                                           |  |

| 47  | DATA                 | I   | SPI data input                                       |  |

| 48  | CLOCK                | 1   | SPI clock input                                      |  |

SLWS225B-DECEMBER 2010-REVISED MAY 2011

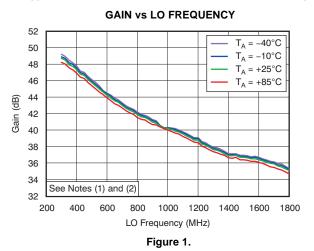

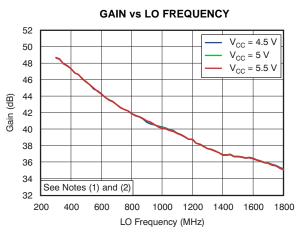

## **TYPICAL CHARACTERISTICS**

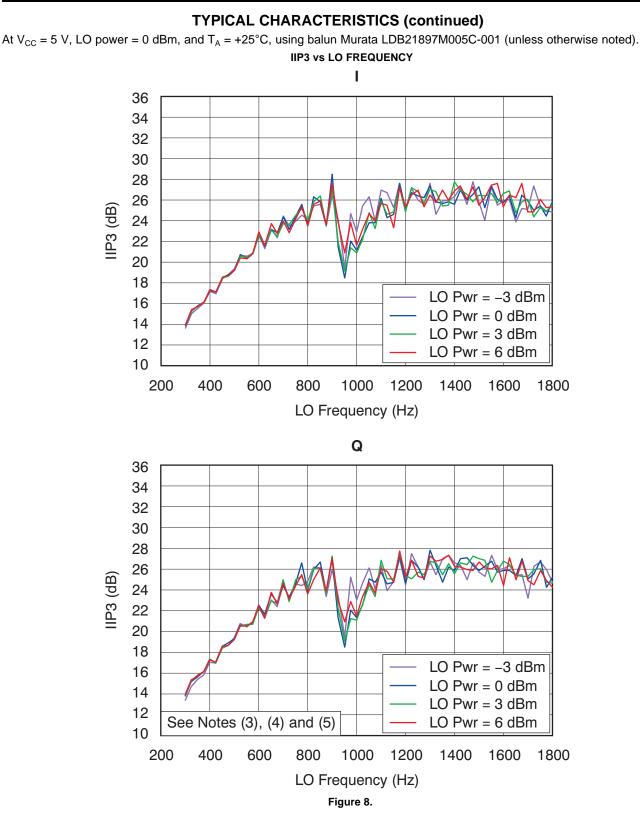

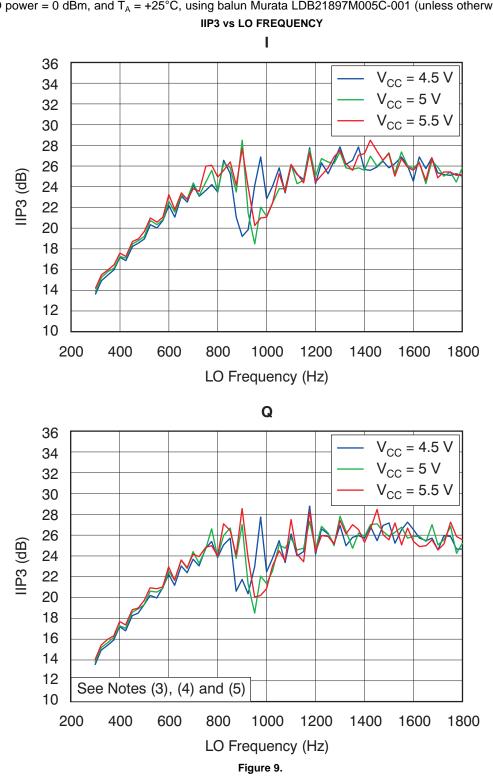

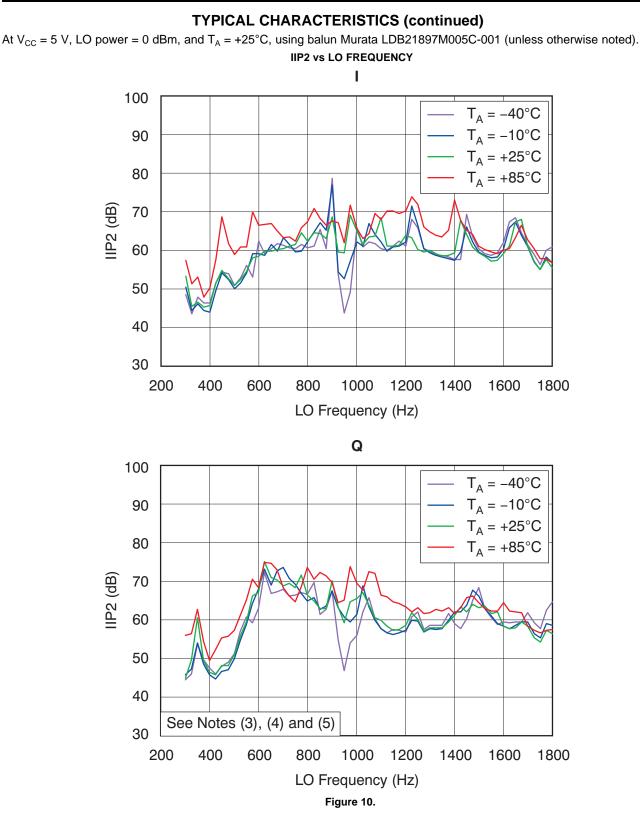

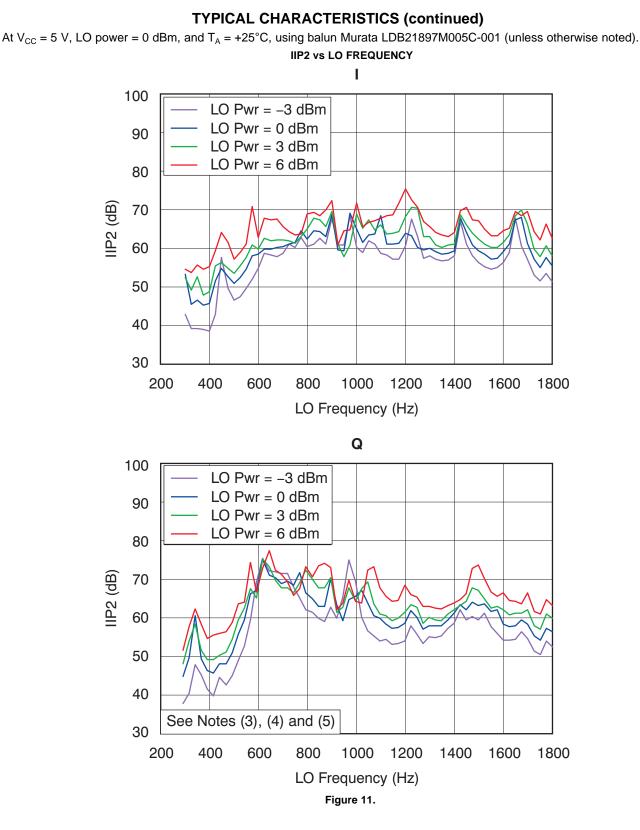

At  $V_{CC} = 5 \text{ V}$ , LO power = 0 dBm, and  $T_A = +25^{\circ}\text{C}$ , using balun Murata LDB21897M005C-001 (unless otherwise noted).

|                                                                                    | Table of Graphs                                  |                                            |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|--|--|

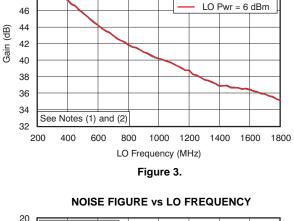

| Gain                                                                               | vs LO frequency <sup>(1)(2)(3)</sup>             | Figure 1, Figure 2, Figure 3               |  |  |

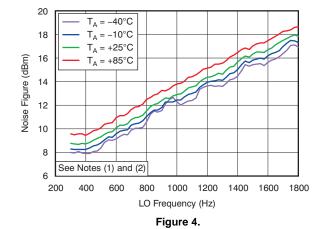

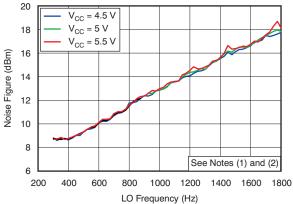

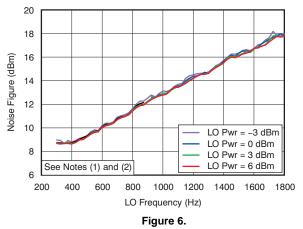

| Noise figure                                                                       | vs LO frequency <sup>(1)(2)(3)</sup>             | Figure 4, Figure 5, Figure 6               |  |  |

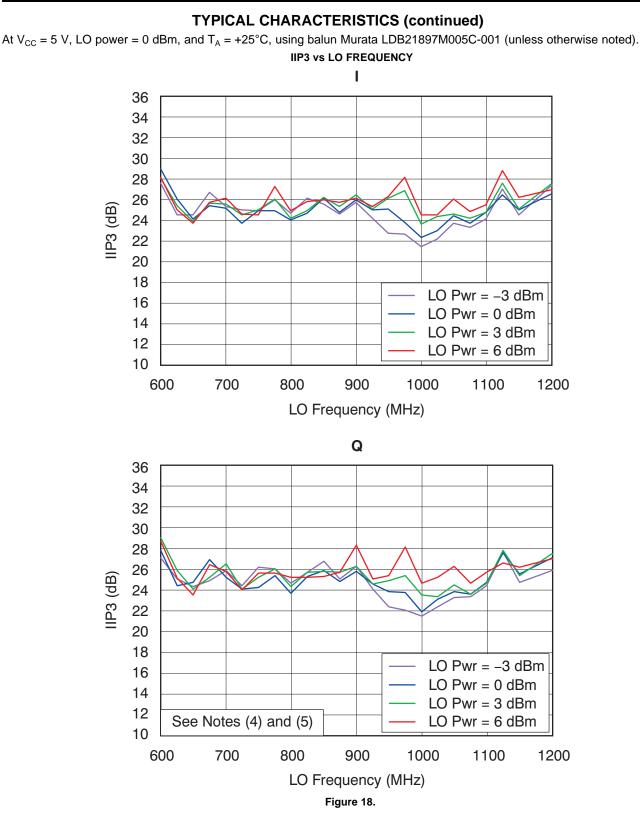

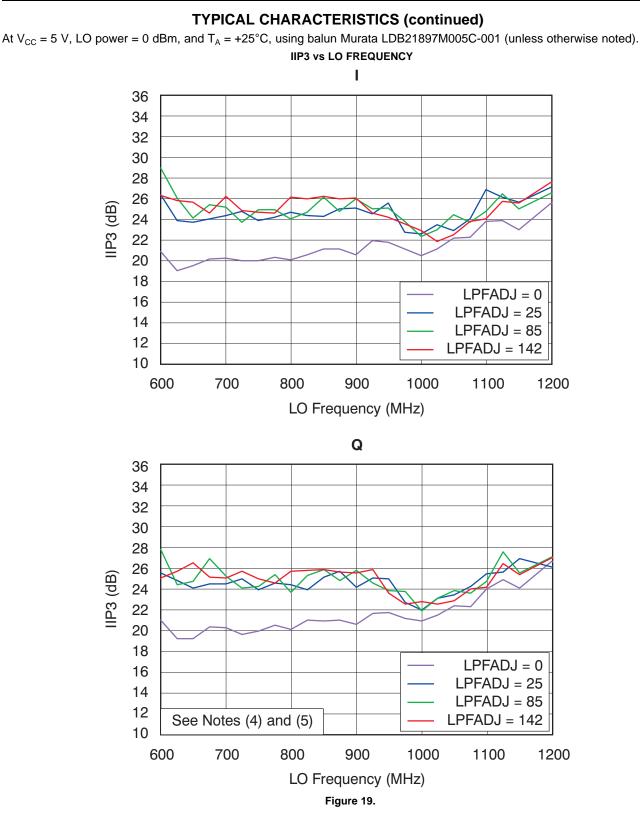

| IIP3                                                                               | vs LO frequency <sup>(4)(5)(6)</sup>             | Figure 7, Figure 9, Figure 8               |  |  |

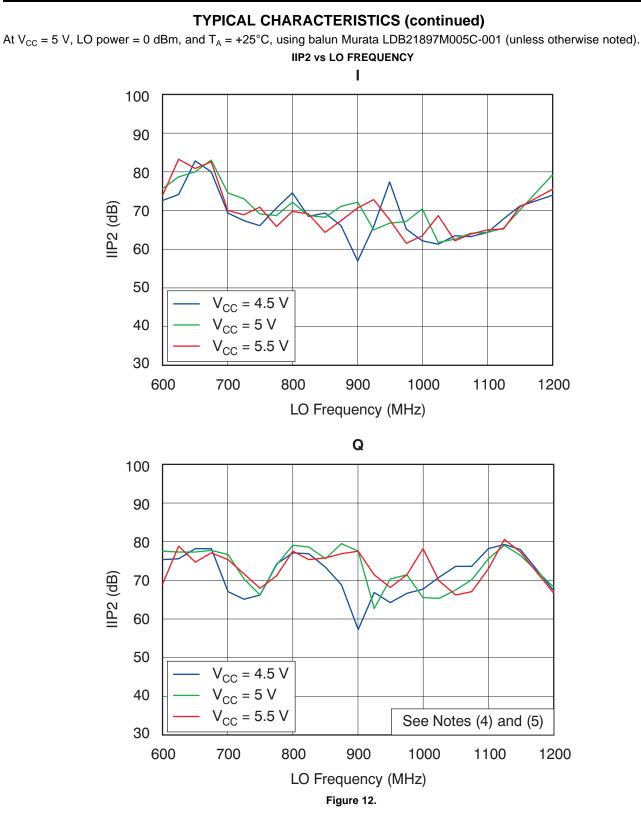

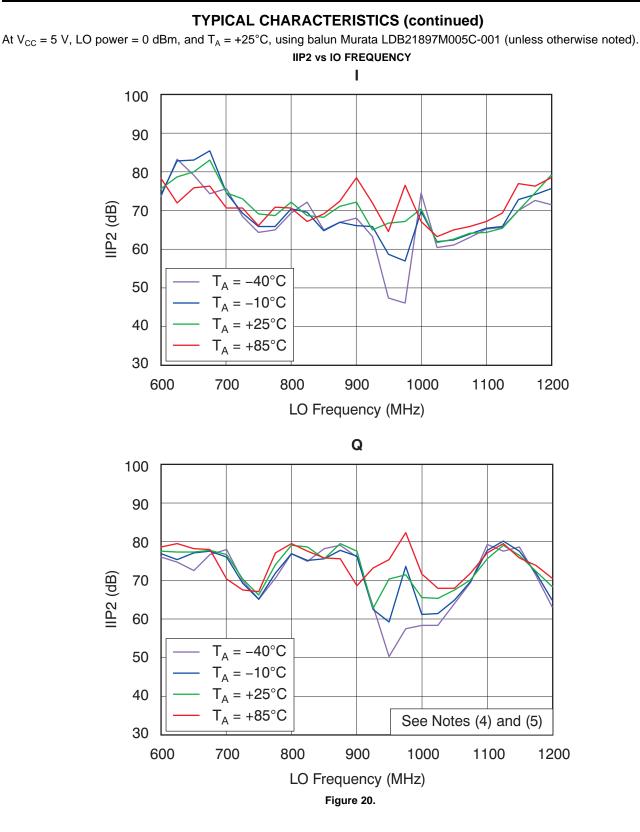

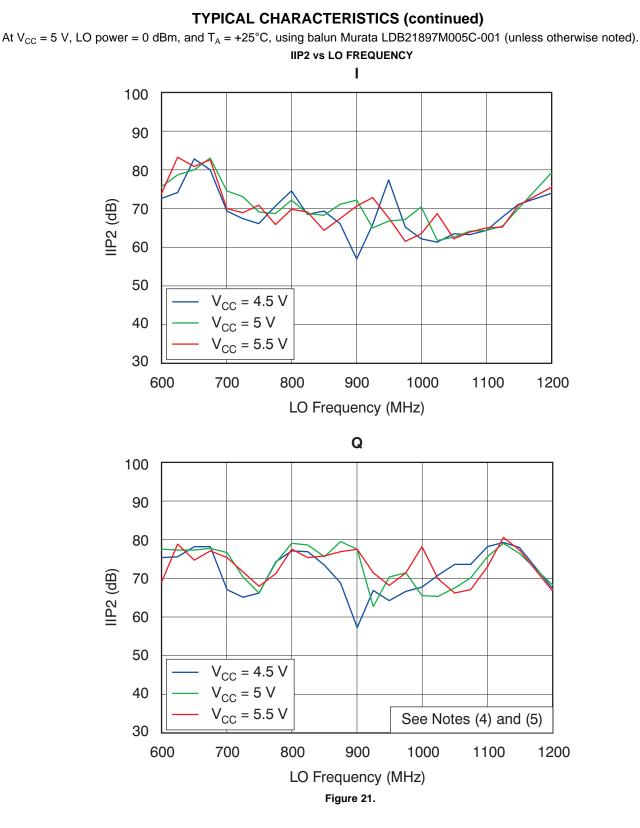

| IIP2                                                                               | vs LO frequency <sup>(4)(5)(6)</sup>             | Figure 10, Figure 12, Figure 11            |  |  |

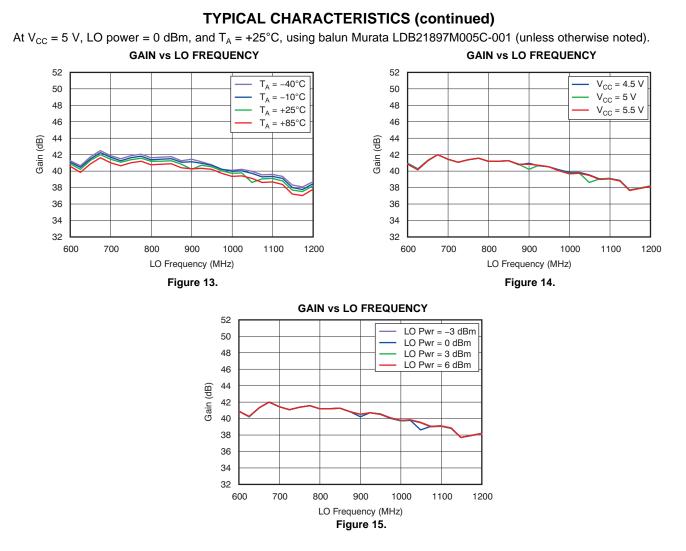

| Gain                                                                               | vs LO frequency                                  | Figure 13, Figure 14, Figure 15            |  |  |

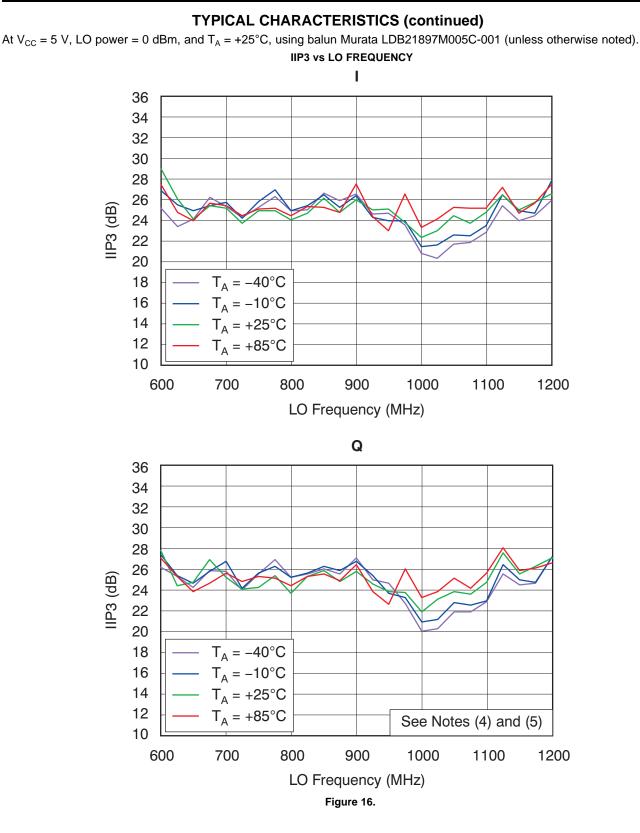

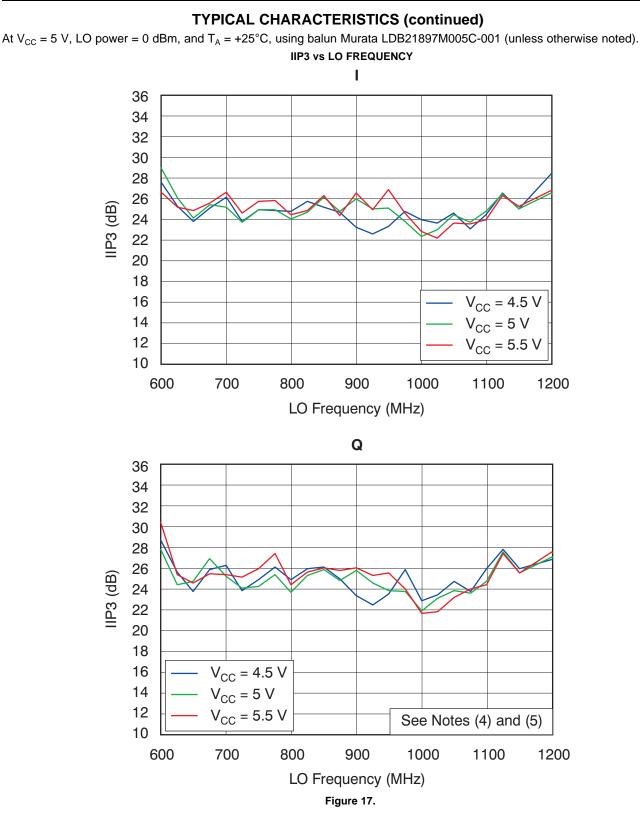

| IIP3                                                                               | vs LO frequency <sup>(5)(6)</sup>                | Figure 16, Figure 17, Figure 18, Figure 19 |  |  |

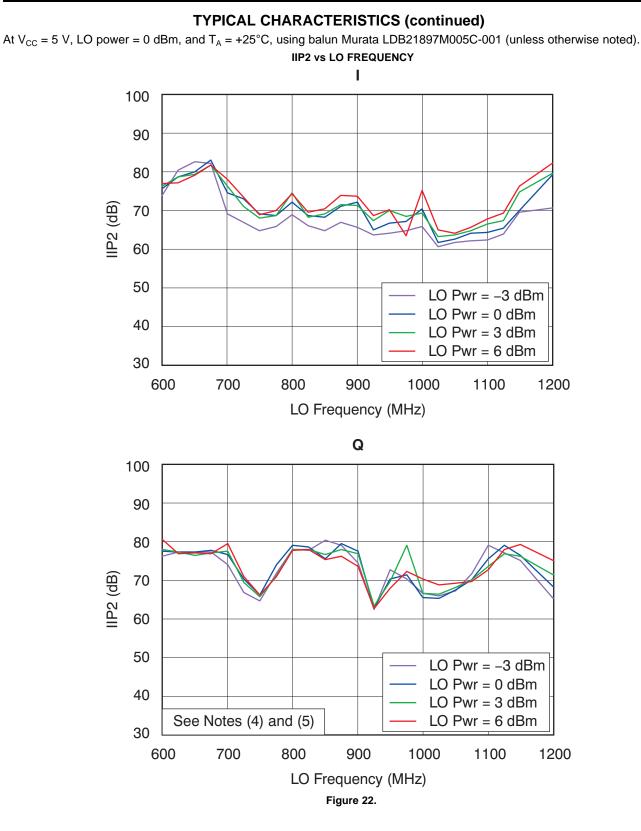

| IIP2                                                                               | vs LO frequency <sup>(5)(6)</sup>                | Figure 20, Figure 21, Figure 22, Figure 23 |  |  |

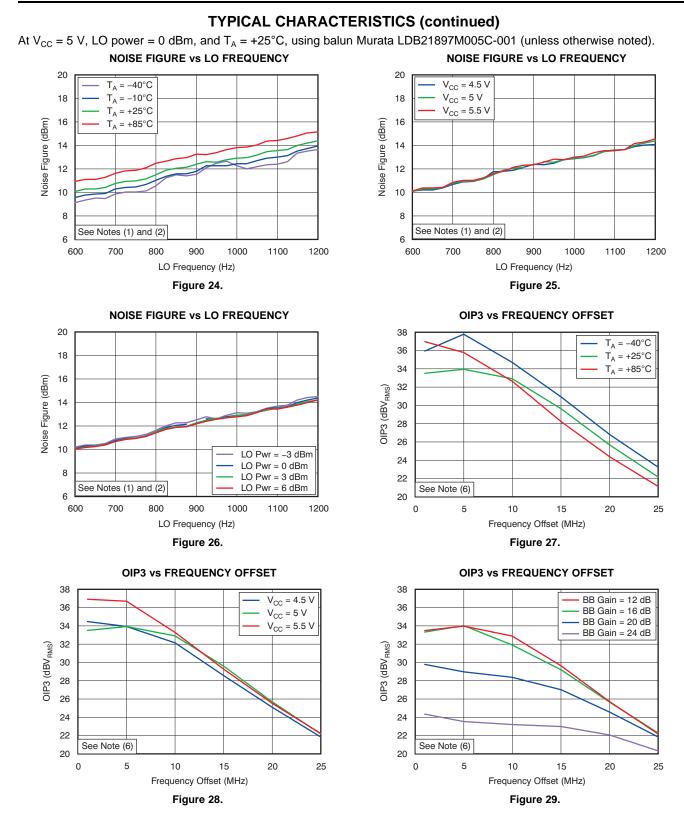

| Noise figure vs LO frequency <sup>(3)</sup>                                        |                                                  | Figure 24, Figure 25, Figure 26            |  |  |

| OIP3                                                                               | vs Frequency offset <sup>(7)(3)</sup>            | Figure 27, Figure 28, Figure 29, Figure 30 |  |  |

| Noise figure                                                                       | vs BB gain setting <sup>(8)</sup>                | Figure 31                                  |  |  |

| Gain                                                                               | vs BB gain setting <sup>(8)</sup>                | Figure 32                                  |  |  |

| Gain                                                                               | vs Frequency offset <sup>(9)</sup>               | Figure 33, Figure 34                       |  |  |

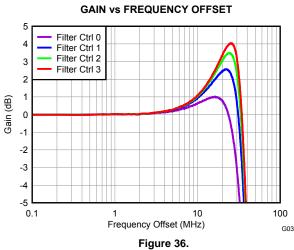

| Gain                                                                               | vs Frequency offset (bypass mode) <sup>(9)</sup> | Figure 35, Figure 36                       |  |  |

| 1-dB LPF corner frequency                                                          | vs LPFADJ setting                                | Figure 37                                  |  |  |

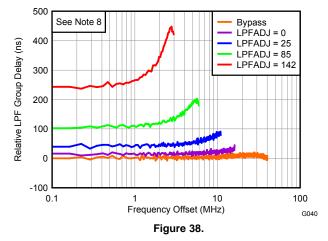

| Relative LPF group delay                                                           | vs Frequency offset <sup>(10)</sup>              | Figure 38                                  |  |  |

| Image rejection                                                                    | vs BB frequency offset                           | Figure 39                                  |  |  |

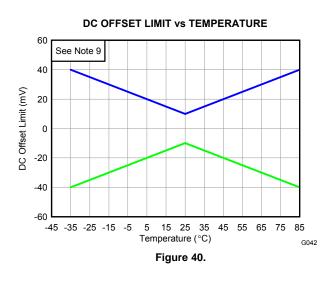

| DC offset limit                                                                    | vs Temperature <sup>(11)</sup>                   | Figure 40                                  |  |  |

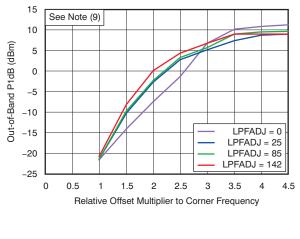

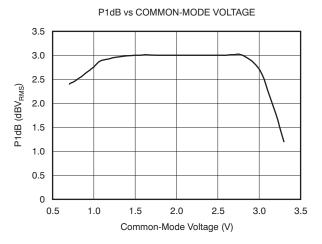

| Out-of-band P1dB vs Relative offset multiplier to corner frequency <sup>(12)</sup> |                                                  | Figure 41                                  |  |  |

(1) Measured with broadband Picosecond 5310A balun on the LO input and single ended connection on the RF input. Performance gain adjusted for the 3-dB differential to single-ended insertion loss.

(2) Performance ripple because of impedance mismatch on the RF input.

(3) Measured with the maximum baseband gain (BB gain) setting, unless otherwise noted.

(4) Measured with broadband Picosecond 5310A balun on the LO input and RF input. Balun insertion loss is compensated for in the measurement.

(5) Out-of-band intercept point is defined with tones that are at least two times farther out than the programmed LPF corner frequency that generate an intermodulation tone that falls inside the LPF passband.

(6) Out-of-band intercept point depends on the demodulator performance and not the baseband circuitry; the measurement is taken at max

(6) Out-of-band intercept point depends on the demodulator performance and not the baseband circuitry; the measurement is taken at max gain but is valid across all PGA settings.

(7) Measured with filter in bypass mode to characterize the passband circuitry across baseband frequencies.

(8) Data taken with LO frequency = 900 MHz.

(9) Normalized gain.

8

(10) Relative to the low frequency offset group delay in bypass mode.

(11) Idet set to 50 µA; RF signal is off; LO at 2.4 GHz at 0 dBm; Det filter set to 1 kHz; Clk Div set to 1024.

(12) In-band tone set to 1 MHz; out-of-band jammer tone set to specified relative offset ratio from the programmed corner frequency. Jammer tone is increased until in-band tone compresses 1 dB.

www.ti.com

RUMENTS

#### SLWS225B - DECEMBER 2010 - REVISED MAY 2011

#### www.ti.com

52

50

48

### **TYPICAL CHARACTERISTICS**

At  $V_{CC}$  = 5 V, LO power = 0 dBm, and  $T_A$  = +25°C, using balun Murata LDB21897M005C-001 (unless otherwise noted).

**GAIN vs LO FREQUENCY**

LO Pwr = -3 dBm

LO Pwr = 0 dBm

LO Pwr = 3 dBm

#### Figure 2.

#### **NOISE FIGURE vs LO FREQUENCY**

Figure 5.

NOISE FIGURE vs LO FREQUENCY

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

www.ti.com

10

SLWS225B - DECEMBER 2010-REVISED MAY 2011

EXAS STRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

www.ti.com

At  $V_{CC} = 5 \text{ V}$ , LO power = 0 dBm, and  $T_A = +25^{\circ}\text{C}$ , using balun Murata LDB21897M005C-001 (unless otherwise noted).

SLWS225B - DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

SLWS225B - DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

www.ti.com

Copyright © 2010–2011, Texas Instruments Incorporated

SLWS225B - DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

SLWS225B - DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

Copyright © 2010–2011, Texas Instruments Incorporated

SLWS225B - DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

SLWS225B-DECEMBER 2010-REVISED MAY 2011

SLWS225B - DECEMBER 2010 - REVISED MAY 2011

TEXAS INSTRUMENTS

www.ti.com

SLWS225B-DECEMBER 2010-REVISED MAY 2011

**TYPICAL CHARACTERISTICS (continued)** At  $V_{CC} = 5 \text{ V}$ , LO power = 0 dBm, and  $T_A = +25^{\circ}\text{C}$ , using balun Murata LDB21897M005C-001 (unless otherwise noted). **IIP2 vs LO FREQUENCY** I 100 90 80 IIP2 (dB) 70 60 50 LPFADJ = 0LPFADJ = 25 40 LPFADJ = 85LPFADJ = 14230 600 700 800 900 1000 1100 1200 LO Frequency (MHz) Q 100 90 80 IIP2 (dB) 70 60 50 LPFADJ = 0LPFADJ = 2540 LPFADJ = 85See Notes (4) and (5) LPFADJ = 14230 600 700 800 900 1200 1000 1100 LO Frequency (MHz) Figure 23.

EXAS

NSTRUMENTS

#### SLWS225B - DECEMBER 2010 - REVISED MAY 2011

Texas Instruments

www.ti.com

SLWS225B-DECEMBER 2010-REVISED MAY 2011

**TYPICAL CHARACTERISTICS (continued)** At  $V_{CC} = 5 \text{ V}$ , LO power = 0 dBm, and  $T_A = +25^{\circ}\text{C}$ , using balun Murata LDB21897M005C-001 (unless otherwise noted). **OIP3 vs FREQUENCY OFFSET NOISE FIGURE vs BB GAIN SETTING** 38 28 3-dB Attn On 3-dB Attn On 36 3-dB Attn Off 3-dB Attn Off 25 34 Noise Figure (dB) 32 OIP3 (dBV<sub>RMS</sub>) 22 30 28 19 26 24 16 22 See Note (6) 20 13 0 5 10 15 20 25 0 2 4 6 8 10 12 14 16 18 20 22 24 Frequency Offset (MHz) **BB** Gain Setting Figure 30. Figure 31. GAIN vs BB GAIN SETTING 43 **GAIN vs FREQUENCY OFFSET** 3-dB Attn On 40 20 3-dB Attn Off 37 0 34 31 Gain (dB) -20 28 Gain (dB) 25 -40 22 19 -60 16 LPFADJ = 0LPFADJ = 25 13 -80 LPFADJ = 850 2 4 6 8 10 12 14 16 18 20 22 24 LPFADJ = 142**BB** Gain Setting -100 10 100 0.1 Frequency Offset (MHz) G035 Figure 32. Figure 33. GAIN vs FREQUENCY OFFSET GAIN vs FREQUENCY OFFSET 5 20 LPFADJ = 0 4 LPFADJ = 25 0 LPFADJ = 85 3 LPFADJ = 1422 -20 1 Gain (dB) Gain (dB 0 -40 -1 -60 -2 Filter Ctrl 0 -3 Filter Ctrl 1 -80 Filter Ctrl 2 -4 Filter Ctrl 3 -5 -100 0.1 10 100 0.1 10 100 1000 1 1 Frequency Offset (MHz) Frequency Offset (MHz) G036 G037 Figure 34. Figure 35.

SLWS225B - DECEMBER 2010-REVISED MAY 2011

#### www.ti.com

EXAS

STRUMENTS

### **TYPICAL CHARACTERISTICS (continued)**

At V<sub>CC</sub> = 5 V, LO power = 0 dBm, and T<sub>A</sub> = +25°C, using balun Murata LDB21897M005C-001 (unless otherwise noted).

**RELATIVE LPF GROUP DELAY vs FREQUENCY OFFSET**

IMAGE REJECTION vs BB FREQUENCY OFFSET

**OUT-OF-BAND P1dB vs RELATIVE OFFSET MULTIPLIER** TO CORNER FREQUENCY

Figure 41.

SLWS225B-DECEMBER 2010-REVISED MAY 2011

www.ti.com

## **REGISTER INFORMATION**

## SERIAL INTERFACE PROGRAMMING REGISTERS DEFINITION

The TRF371109 features a three-wire serial programming interface (SPI) that controls an internal 32-bit shift register. There are three signals that must be applied: CLOCK (pin 48), serial DATA (pin 47), and STROBE (pin 46). DATA (DB0–DB31) is loaded LSB-first and is read on the rising edge of CLOCK. STROBE is asynchronous to CLOCK, and at its rising edge the data in the shift register is loaded into the selected internal register. The first two bits (DB0–DB1) are the address to select the available internal registers.

### **READBACK Mode**

The TRF371109 implements the capability to read back the content of the serial programming interface registers. In addition, it is possible to read back the status of the internal DAC registers that are automatically set after an auto dc-offset calibration. Each readback is composed by two phases: writing followed by the actual reading of the internal data (refer to Figure 42).

During the writing phase, a command is sent to the TRF371109 to set it in readback mode and to specify which register is to be read. In the proper reading phase, at each rising clock edge, the internal data is transferred into the READBACK pin and can be read at the following falling edge (LSB first). The first clock after LE goes high (end of writing cycle) is idle, and the following 32 clock pulses transfer the internal register content to the READBACK pin.

### Figure 42. Serial Programming Timing Diagram

Table 1 shows the register summary. Table 2 through Table 6 list the device setup information for Register 1 to Register 5, respectively. Table 7 lists the device setup for Register 0.

SLWS225B - DECEMBER 2010 - REVISED MAY 2011

www.ti.com

# Table 1. Register Summary<sup>(1)</sup>

|       |                        | 1                  |       |                  |                  |       |                  |

|-------|------------------------|--------------------|-------|------------------|------------------|-------|------------------|

| Bit # | Reg 1                  | Reg 2              | Bit # | Reg 3            | Reg 5            | Bit # | Reg 0            |

| Bit0  | _                      |                    | Bit0  |                  |                  | Bit0  |                  |

| Bit1  | Register address       | Register address   | Bit1  | Register address | Register address | Bit1  | Register address |

| Bit2  |                        |                    | Bit2  |                  |                  | Bit2  |                  |

| Bit3  | - SPI bank addr        | SPI bank addr      | Bit3  | SPI bank addr    | SPI bank addr    | Bit3  | SPI bank addr    |

| Bit4  |                        |                    | Bit4  | SI I Dalik addi  |                  | Bit4  |                  |

| Bit5  | PWD RF                 | En auto-cal        | Bit5  |                  | Mix GM trim      | Bit5  | ID               |

| Bit6  | NU                     |                    | Bit6  |                  |                  | Bit6  |                  |

| Bit7  | PWD buf                |                    | Bit7  | ILoadA           | Mix LO trim      | Bit7  |                  |

| Bit8  | Р                      |                    | Bit8  | ILUauA           |                  | Bit8  |                  |

| Bit9  | NU                     | IDAC for dc offset | Bit9  |                  | LO trim          | Bit9  |                  |

| Bit10 | PWD DC OFF DIG         | IDAC IOI de onset  | Bit10 |                  | LO unm           | Bit10 |                  |

| Bit11 | NU                     |                    | Bit11 |                  | Mix buf trim     | Bit11 | NU               |

| Bit12 | BB gain                |                    | Bit12 | ILoadB           |                  | Bit12 |                  |

| Bit13 |                        |                    | Bit13 |                  | Fltr trim        | Bit13 |                  |

| Bit14 |                        |                    | Bit14 |                  |                  | Bit14 |                  |

| Bit15 |                        |                    | Bit15 |                  | Out buf trim     | Bit15 |                  |

| Bit16 |                        |                    | Bit16 |                  |                  | Bit16 | DC offset Q DAC  |

| Bit17 |                        | QDAC for dc offset | Bit17 |                  |                  | Bit17 |                  |

| Bit18 |                        | QDAC IOI de offset | Bit18 |                  |                  | Bit18 |                  |

| Bit19 |                        |                    | Bit19 |                  |                  | Bit19 |                  |

| Bit20 | LPFADJ                 |                    | Bit20 | QLoadA           |                  | Bit20 |                  |

| Bit21 | LPFADJ                 |                    | Bit21 |                  |                  | Bit21 |                  |

| Bit22 |                        | IDet               | Bit22 |                  |                  | Bit22 |                  |

| Bit23 | -                      | IDet               | Bit23 |                  |                  | Bit23 |                  |

| Bit24 | -                      | Cal sel            | Bit24 |                  | NU               | Bit24 |                  |

| Bit25 | DC detector            |                    | Bit25 |                  |                  | Bit25 |                  |

| Bit26 | bandwidth<br>Fast gain | CLK div ratio      | Bit26 | QLoadB           |                  | Bit26 |                  |

| Bit27 |                        |                    | Bit27 |                  |                  | Bit27 |                  |

| Bit28 | Gain sel               | Cal clk sel        | Bit28 |                  |                  | Bit28 | DC offset I DAC  |

| Bit29 | Osc test               |                    | Bit29 | Bypass           |                  | Bit29 |                  |

| Bit30 | NU                     | Osc trim           | Bit30 | Elter stel       |                  | Bit30 |                  |

| Bit31 | En 3dB attn            |                    | Bit31 | Fltr ctrl        |                  | Bit31 |                  |

(1) Register 4 is not used.

## Table 2. Register 1 Device Setup

| <b>REGISTER 1</b> | NAME           | RESET VALUE | WORKING DESCRIPTION                          |

|-------------------|----------------|-------------|----------------------------------------------|

| Bit0              | ADDR<0>        | 1           |                                              |

| Bit1              | ADDR<1>        | 0           | Register address                             |

| Bit2              | ADDR<2>        | 0           |                                              |

| Bit3              | ADDR<3>        | 1           |                                              |

| Bit4              | ADDR<4>        | 0           | - SPI bank address                           |

| Bit5              | PWD_MIX        | 0           | Mixer power down (Off = '1')                 |

| Bit6              | NU             | 0           | Not used                                     |

| Bit7              | PWD_BUF        | 1           | Mixer out test buffer power down (Off = '1') |

| Bit8              | PWD_FILT       | 0           | Baseband filter power down (Off = '1')       |

| Bit9              | NU             | 0           | Not used                                     |

| Bit10             | PWD_DC_OFF_DIG | 1           | DC offset calibration power down (Off = '1') |

Copyright © 2010–2011, Texas Instruments Incorporated

SLWS225B-DECEMBER 2010-REVISED MAY 2011

TEXAS INSTRUMENTS

www.ti.com

| <b>REGISTER 1</b> | NAME        | RESET VALUE | WORKING DESCRIPTION                                                                                                                              |  |  |  |  |  |  |

|-------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit11             | NU          | 1           | Not used                                                                                                                                         |  |  |  |  |  |  |

| Bit12             | BBGAIN_0    | 1           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit13             | BBGAIN_1    | 1           | Baseband gain setting. Default = 15. Range is from 0 (minimum gain                                                                               |  |  |  |  |  |  |

| Bit14             | BBGAIN_2    | 1           | setting) to 24 (maximum gain setting). See the <i>Application Information</i> section for more information on gain setting and fast gain control |  |  |  |  |  |  |

| Bit15             | BBGAIN_3    | 1           | options.                                                                                                                                         |  |  |  |  |  |  |

| Bit16             | BBGAIN_4    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit17             | LPFADJ_0    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit18             | LPFADJ_1    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit19             | LPFADJ_2    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit20             | LPFADJ_3    | 0           | Sets programmable low-pass filter corner frequency. Range = 255                                                                                  |  |  |  |  |  |  |

| Bit21             | LPFADJ_4    | 0           | (lowest corner frequency) to 0 (highest corner frequency). Default values 128.                                                                   |  |  |  |  |  |  |

| Bit22             | LPFADJ_5    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit23             | LPFADJ_6    | 0           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit24             | LPFADJ_7    | 1           |                                                                                                                                                  |  |  |  |  |  |  |

| Bit25             | EN_FLT_B0   | 0           | Selects dc offset detector filter bandwidth.                                                                                                     |  |  |  |  |  |  |

| Bit26             | EN_FLT_B1   | 0           | Setting {00, 01, 11} = {10 MHz, 10 kHz, 1 kHz}                                                                                                   |  |  |  |  |  |  |

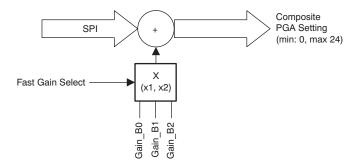

| Bit27             | EN_FASTGAIN | 0           | Enable external fast-gain control                                                                                                                |  |  |  |  |  |  |

| Bit28             | GAIN_SEL    | 0           | Fast-gain control multiplier bit (×2 = 1)                                                                                                        |  |  |  |  |  |  |

| Bit29             | OSC_TEST    | 0           | Enables Osc out on readback pin if = 1                                                                                                           |  |  |  |  |  |  |

| Bit30             | NU          | 0           | Not used                                                                                                                                         |  |  |  |  |  |  |

| Bit31             | EN 3dB Attn | 0           | Enables output 3-dB attenuator                                                                                                                   |  |  |  |  |  |  |

|                   |             |             |                                                                                                                                                  |  |  |  |  |  |  |

**EN\_FLT\_B0/1:** These bits control the bandwidth of the detector used to measure the dc offset during the automatic calibration. There is an RC filter in front of the detector that can be fully bypassed. EN\_FLT\_B0 controls the resistor (bypass = 1), while EN\_FLT\_B1 controls the capacitor (bypass = 1). The typical 3-dB cutoff frequencies of the detector bandwidth are summarized in Table 3 (see the *Application Information* section for more detail on the dc offset calibration and the detector bandwidth).

### **Table 3. Detector Bandwidth Settings**

| EN_FLT_B1 | EN_FLT_B0 | TYPICAL 3-dB CUTOFF FREQ | NOTES                          |

|-----------|-----------|--------------------------|--------------------------------|

| x         | 0         | 10 MHz                   | Maximum bandwidth, bypass R, C |

| 0         | 1         | 10 kHz                   | Enable R                       |

| 1         | 1         | 1 kHz                    | Minimum bandwidth, enable R, C |

| Table 4. | Register | 2 Device | Setup |

|----------|----------|----------|-------|

|----------|----------|----------|-------|

| REGISTER 2 | NAME       | RESET VALUE | WORKING DESCRIPTION                                |

|------------|------------|-------------|----------------------------------------------------|

| Bit0       | ADDR<0>    | 0           |                                                    |

| Bit1       | ADDR<1>    | 1           | Register address                                   |

| Bit2       | ADDR<2>    | 0           |                                                    |

| Bit3       | ADDR<3>    | 1           |                                                    |

| Bit4       | ADDR<4>    | 0           | SPI bank address                                   |

| Bit5       | EN_AUTOCAL | 0           | Enable autocal when = '1'; reset to '0' when done. |

## Table 2. Register 1 Device Setup (continued)

SLWS225B - DECEMBER 2010 - REVISED MAY 2011

www.ti.com

## Table 4. Register 2 Device Setup (continued)

| <b>REGISTER 2</b> | NAME             | RESET VALUE | WORKING DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-------------------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit6              | IDAC_BIT0        | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Bit7              | IDAC_BIT1        | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Bit8              | IDAC_BIT2        | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Bit9              | IDAC_BIT3        | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Bit10             | IDAC_BIT4        | 0           | I-DAC bits to be set during manual dc offset cal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Bit11             | IDAC_BIT5        | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |